一直想了解一下vivado的高层次综合是如何是如何使用的,今天下午学习了一下HLS的基本使用,现将其记录如下。

首先点击VIVADO HLS,然后出现以下界面:

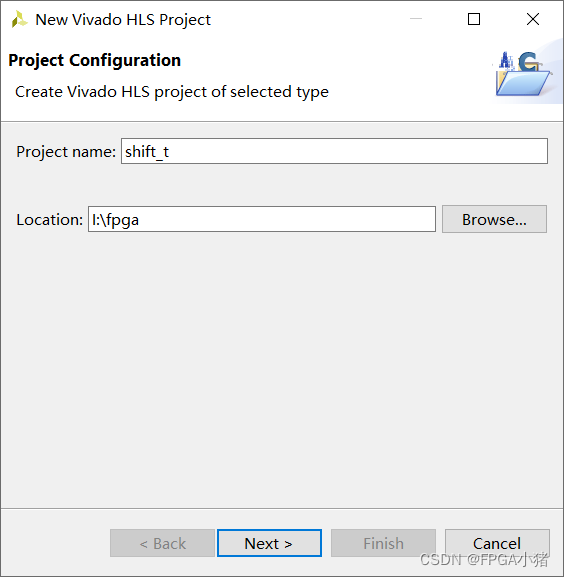

然后在quick start中根据需求点击自己需要的,这里点击Create New Project,创建一个新的项目。出现导引栏:

根据需求给其命名并存放在相应位置,点击next。

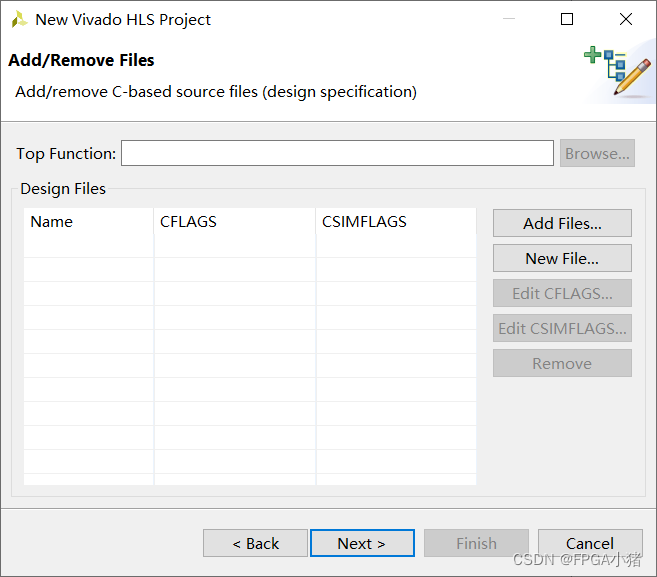

Top Function就是你要根据哪个函数综合成IP模块,自己自定义。下面的设计文件如果有用到已经存在的就可将其添加进来,没有的话就next。

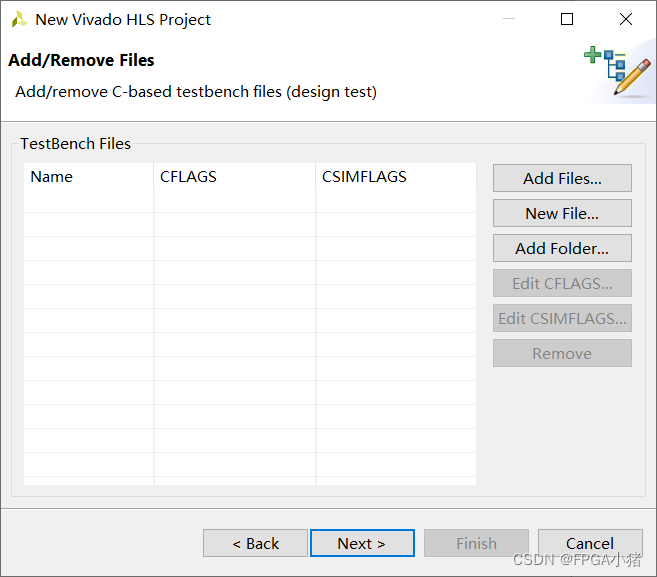

testbench也是一样的,有就加进来,没有就直接点击next。

testbench也是一样的,有就加进来,没有就直接点击next。

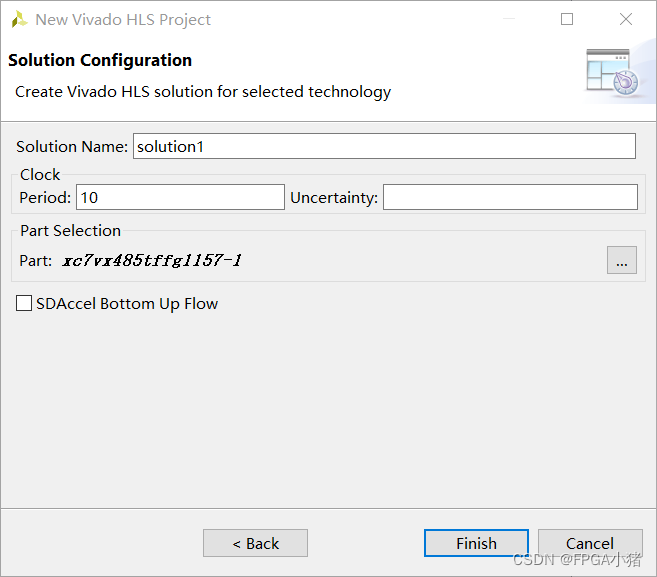

在这里选择解决方案,不同的解决方案对应不同的芯片和相对应的约束,一个HLS project可以有多个解决方案。part对应的芯片信号。点击finish。

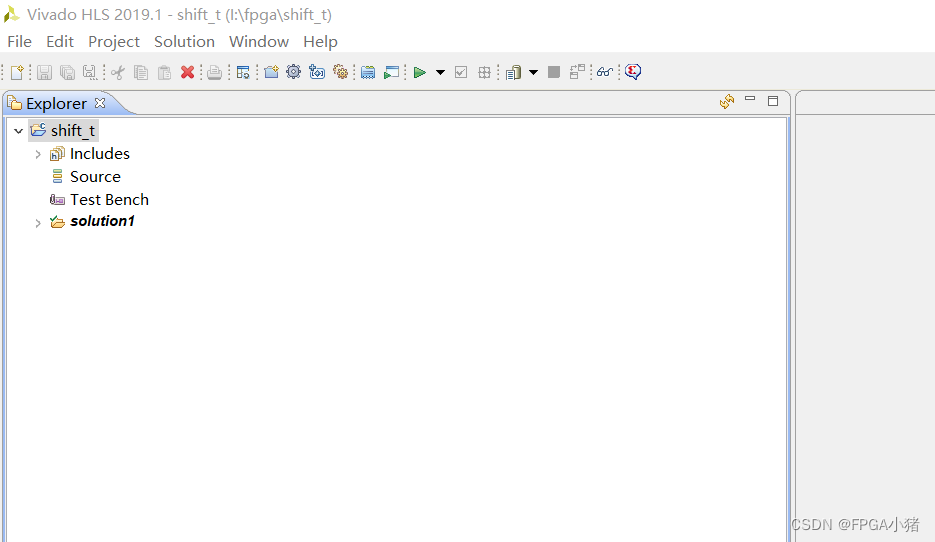

之后出现以下界面:

Source对应写的文件,testbench就是测试文件。这里右键source,新建.cpp文件。

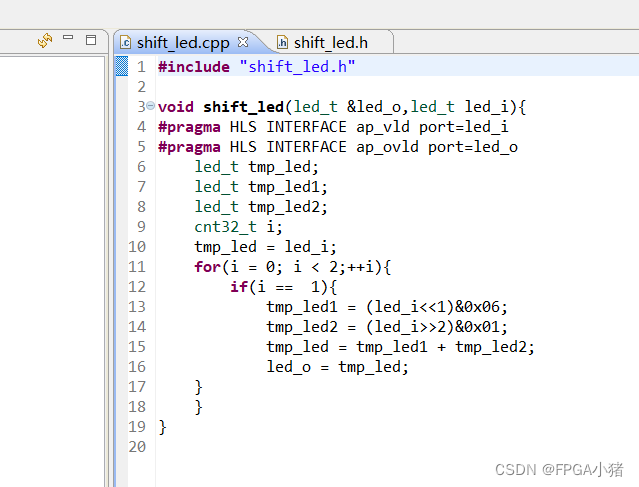

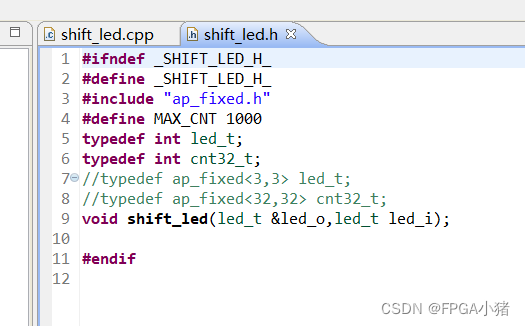

编写两个文件分别为头文件和源文件。

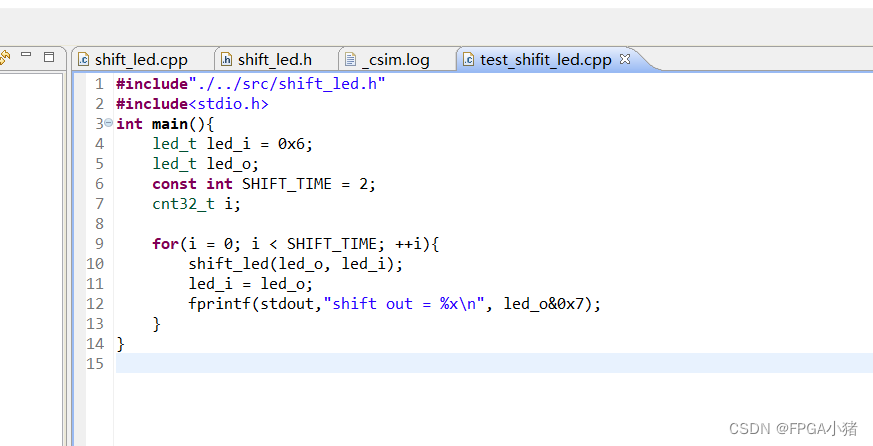

无误后,编辑test bench文件

之后点击菜单栏的project,run c simulation。

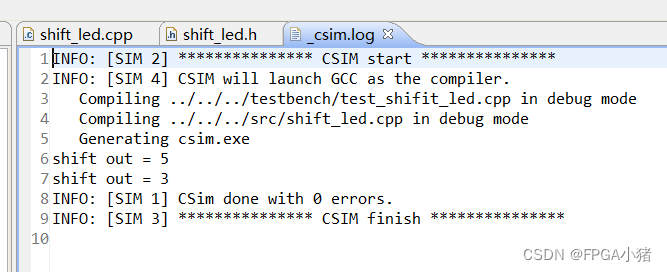

根据自己需求打钩。点击ok得到打印输出。

根据自己需求打钩。点击ok得到打印输出。

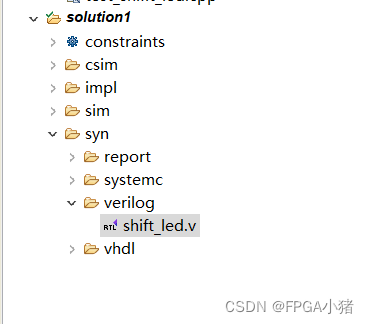

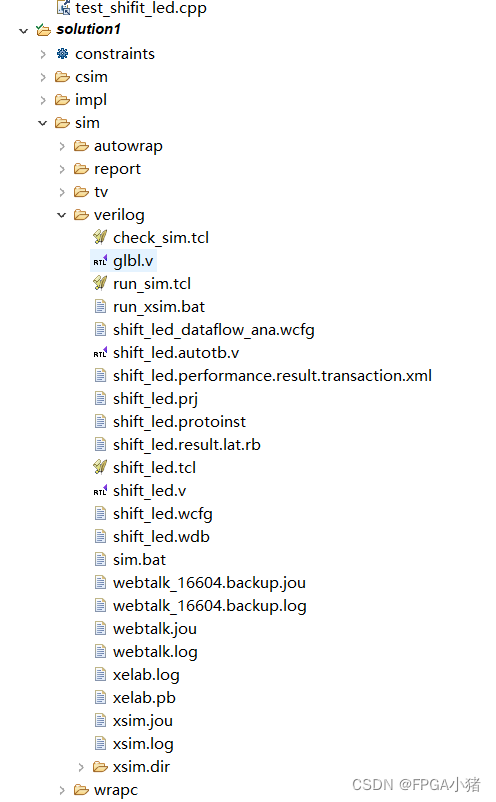

没问题,点击菜单栏的Solution->Run c synthesis->active Solution,生成Verilog语言。在下图子目录下生成.v文件。

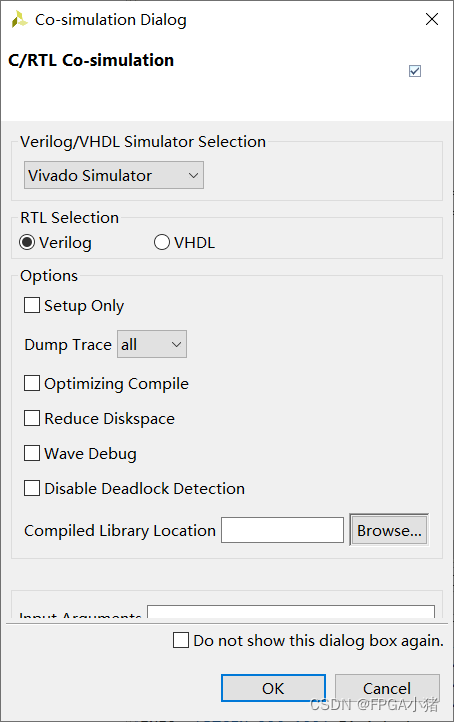

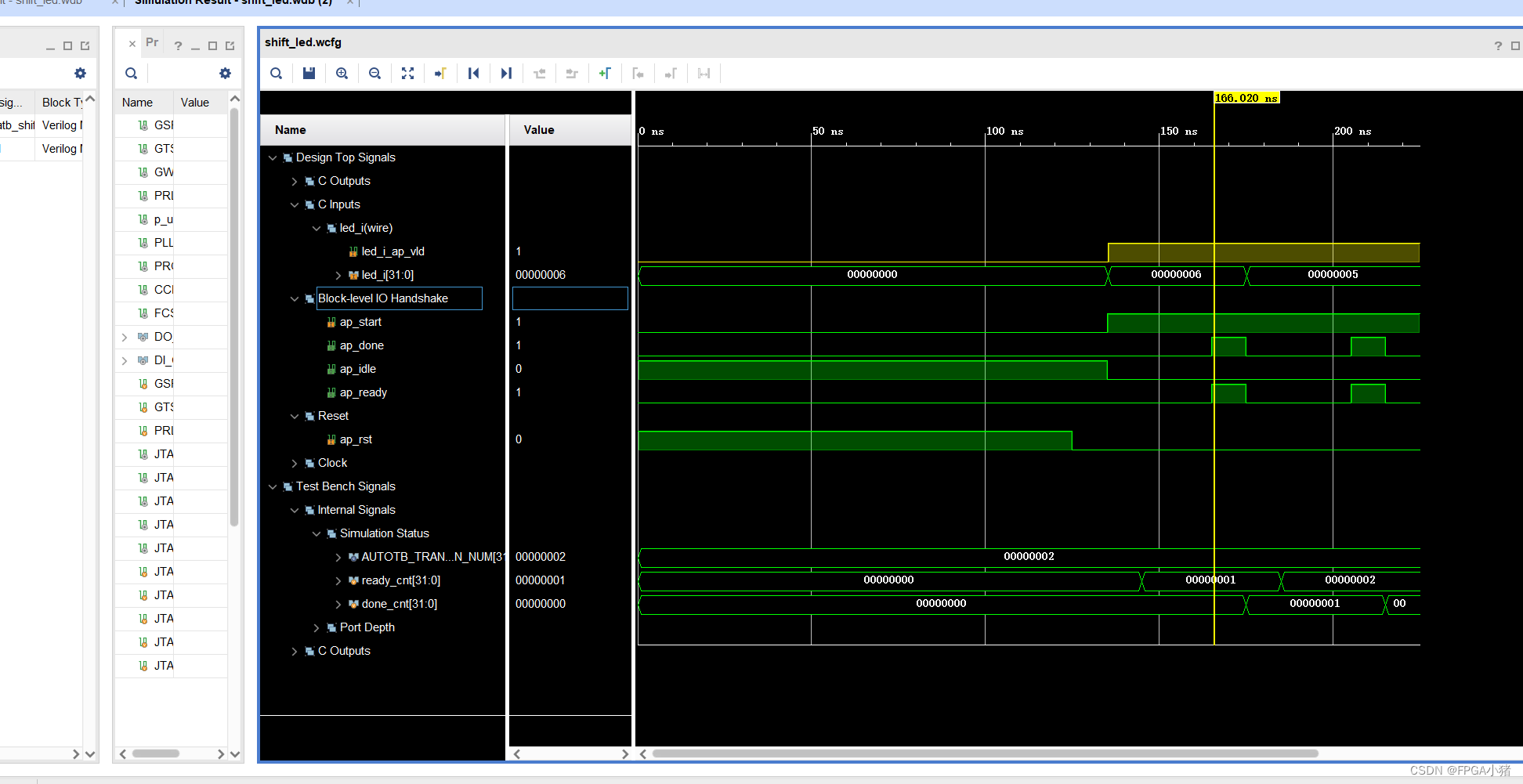

点击点击菜单栏的Solution->Run c/RTL Cosimulation。生成波形图。

ok后,生成可在VIVADO下打开的波形wcfg文件。

使用vivado打开shift_led.wcfg。

142

142

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?