Verilog HDL的结构化建模

一、前言

结构描述方式就是将硬件电路描述成一个分级子模块系统,通过逐层调用这些模块构成功能复杂的数字逻辑电路和系统的一种描述方式。根据所调用子模块的不同抽象级别,可以将模块的结构描述方式分成如下三类:

- 模块级建模:通过调用由用户设计生成的低级子模块来对硬件电路结构进行说明,这种情况下由低级模块的实例组成。

- 门级建模:通过调用Verilog HDL内部的基本门级元件来对硬件电路的结构进行说明,这种情况下模块将由基本门级元件的实例组成。

- 开关级建模:通过调用Verilog HDL内部的基本开关元件来对硬件电路的结构进行说明,这种情况下模块将由基本开关级元件的实例组成。

二、 模块级建模

如下所示,我们可以先定义一个半加器模块,然后通过调用半加器来构成一个全加器

module halfadder(a, b, s, c); // 半加器模块

input a,b;

output c,s;

assign s = a ^ b;

assign c = a & b;

endmodule

module fulladder(p, q, ci, co, sum); // 全加器模块

input p,q,ci;

output co,sum;

wire w1,w2,w3;

halfadder u1(p, q, w1, w2);

halfadder u2(ci, w1, sum, w3);

assign co = w2 | w3;

endmodule

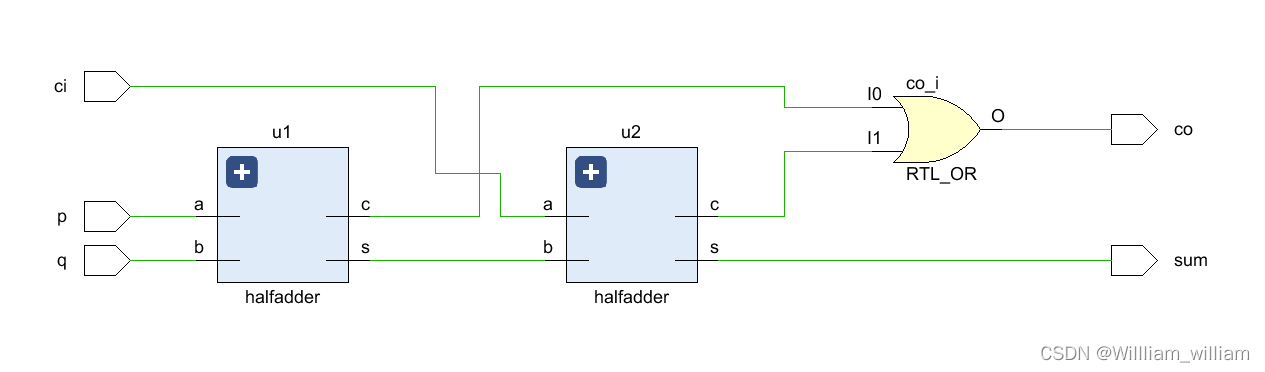

经过综合后得到的电路图如下所示

三、 门级建模

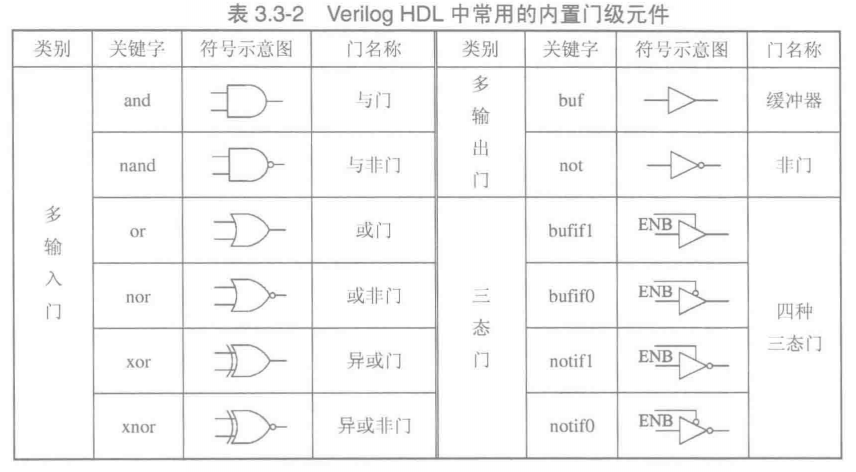

Verilog HDL常用的内置门级元件如下

多输入门元件调用的语法格式如下:

元件名 <实例名> ( <输出端口>, <输入端口1>, <输入端口2>, ..., <输入端口n> )

例如:

and and1(out, in1, in2);

or or2(out, a, b, c, d);

xor x1(xout, p1, p2, p3, p4);

多输出门元件调用的语法格式如下:

元件名 <实例名> ( <输出端口1>, <输出端口2>, ..., <输入端口n>, <输入端口> )

例如:

not not1(out1, out2, in);

buf buf1(out1, out2, out3, in);

三态门元件调用的语法格式如下:

元件名 <实例名> ( <数据输出端口>, <数据输入端口>, <控制端口> )

例如:

bufif1 bf1(bus, mem, enable);

bufif0 bf0(out1, in1, ctrl);

notif1 nt1(out, in, ctrl);

notif0 nt0(addr, abus, select);

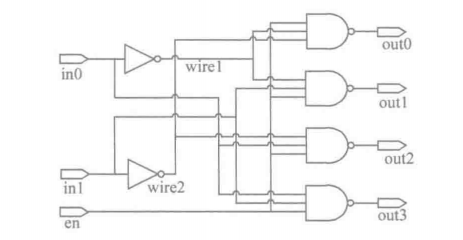

如下为调用门级单元实现的2-4线译码器

module decoder2_4(in0, in1, en, out0, out1, out2, out3);

output out0, out1, out2, out3;

input in0, in1, en;

wire w1,w2;

not u1(w1, in0),

u2(w2, in1);

nand u3(out0, en, w1, w2),

u4(out1, en, w1, in1),

u5(out2, en, in0, w2),

u6(out3, en, in0, in1);

endmodule

经过综合后得到的电路图如下所示

四、 开关级建模

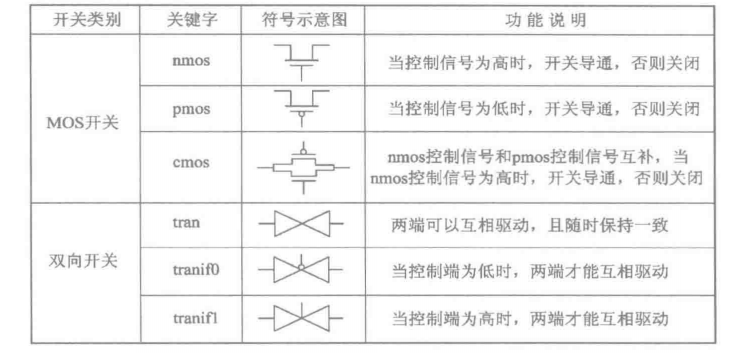

如下为Verilog HDL提供的开关级元器件

2输入与非门的Verilog HDL程序代码如下所示

module nnand2(a, b, y);

input a,b;

output y;

supply0 Gnd; // supply0为内部参量,表示低电平

supply1 Vdd; // supply1为内部参量,表示高电平

wire im1;

pmos g1(y, Vdd, a);

pmos g2(y, Vdd, b);

nmos g3(y, im1, a);

nmos g4(im1, Gnd, b);

endmodule

然后我们编写测试模块如下所示

module tb;

reg a,b;

wire out;

nnand2 u1(a, b, out);

initial begin

a = 0; b = 0;

#100;

a = 0; b = 1;

#100;

a = 1; b = 0;

#100;

a = 1; b = 1;

#100;

end

endmodule

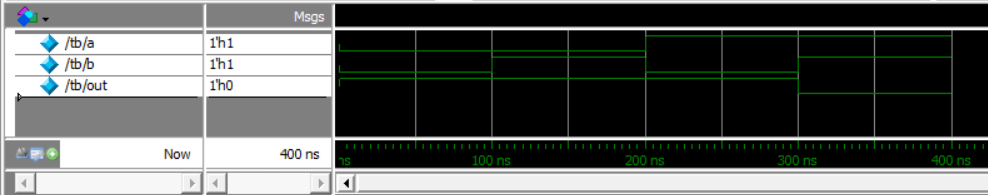

可得仿真波形如下所示,可以看出,其逻辑关系为与非门

其cmos电路如图所示

五、附录

上一篇:Verilog学习之路(4)— Verilog HDL的程序设计语句

下一篇:Verilog学习之路(6)— 组合电路的设计

1073

1073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?