🌟🌟🌟博主主页:MuggleZero 🌟🌟🌟

《ARMv8架构初学者笔记》专栏地址:《ARMv8架构初学者笔记》

前文:

对于使用Set和Way的clean和invalidate操作,我们只能在特定级别的cache上执行。对于使用虚拟地址的操作,ARM架构定义了两种架构(PoU和PoC)来帮助我们基于虚拟地址clean或invalidate cache。

指令和数据可以保存在独立的cache中,也可以保存在统一的cache中。一个cache层次结构可以有一个或多个独立的指令和数据cache,有一个或多个统一的缓存,位于最接近主存储器的层次。cache拓扑结构的内存一致性可以用统一点(PoU)、一致性点(PoC)、持久性点(PoP)和深度持久性点(PoDP)来定义。

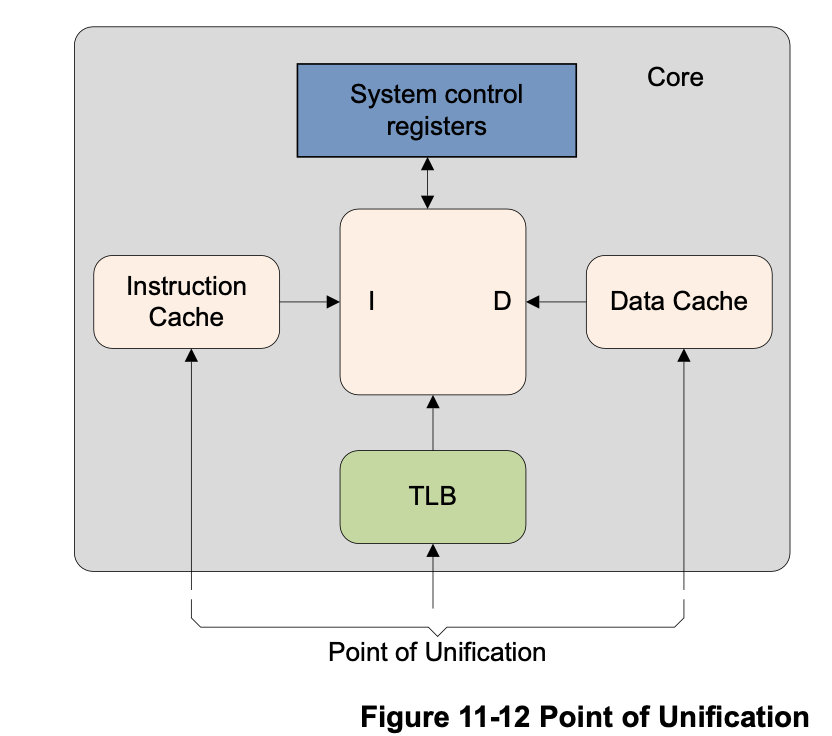

PoU(Point of Unification)

一个CPU core的PoU是指core的指令和数据cache以及映TLB保证能看到同一个内存位置的拷贝点。例如,在一个有哈佛一级缓存和用于缓存映射表项的TLB的系统中,一个统一的二级缓存将是PoU点。如果没有外部cache,主内存将是PoU点。

对PoU的了解使得self-modifying的代码能够确保未来的指令获取是由代码的修改版本正确进行的。我们可以通过使用一个两阶段的过程来做到这一点。

-

按地址清理相关的数据cache条目。

-

按地址废止指令缓存条目。

如果PoU点在任何一级数据cache之前,由VA对PoU点指令进行的数据或统一缓存的清理是否会产生转换故障。

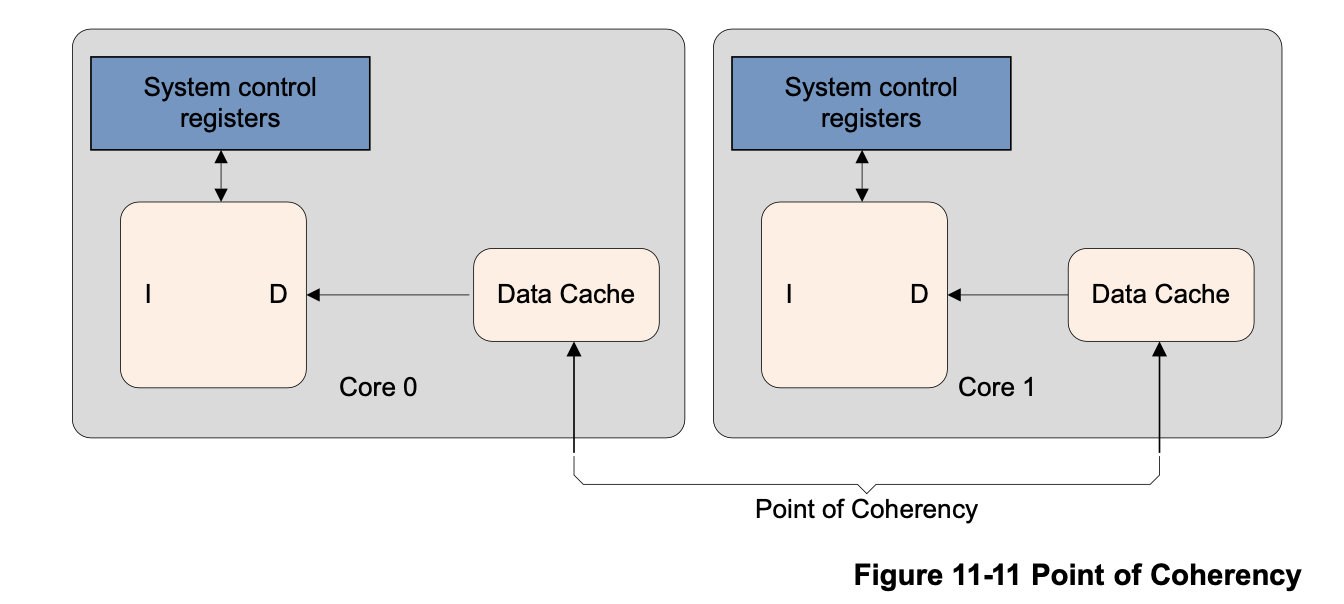

PoC(Point of Coherency)

对于一个特定的地址,PoC是所有观察者,例如内核、DSP或DMA引擎,能够访问内存的点,保证能够看到相同的内存位置的副本。通常情况下,这是主要的外部系统内存。

欢迎关注我的个人微信公众号,一起交流学习嵌入式开发知识!

关注「求密勒实验室」

本文深入解析ARMv8架构中的PoU(统一点)与PoC(一致性点),探讨虚拟地址下clean和invalidate操作在不同cache层次的影响,以及它们在自修改代码和内存一致性策略中的关键作用。通过实例和内存拓扑分析,带你走进高级缓存管理的世界。

本文深入解析ARMv8架构中的PoU(统一点)与PoC(一致性点),探讨虚拟地址下clean和invalidate操作在不同cache层次的影响,以及它们在自修改代码和内存一致性策略中的关键作用。通过实例和内存拓扑分析,带你走进高级缓存管理的世界。

548

548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?