🌟🌟🌟博主主页:MuggleZero 🌟🌟🌟

《ARMv8架构初学者笔记》专栏地址:《ARMv8架构初学者笔记》

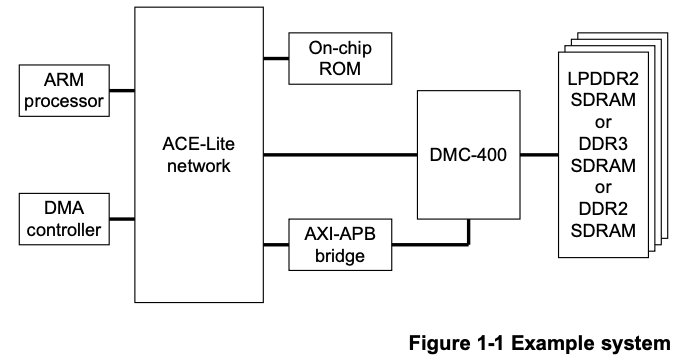

DMC(Dynamic Memory Controller)-400是400系列的一个动态内存控制器。DMC-400是一个符合高级微控制器总线结构(AMBA)的片上系统(SoC)外设,由ARM开发、测试和授权。它是一个高性能、区域优化的内存控制器,与AMBA ACE-Lite协议兼容。它支持以下内存设备:

-

双倍数据速率2(DDR2)同步动态随机存取存储器(SDRAM)。

-

低功耗双倍数据速率2(LPDDR2)-S2 SDRAM

-

lpddr2-s4 SDRAM

-

双倍数据速率3(DDR3)SDRAM

-

低电压DDR3 SDRAM。

DMC-400实现了SoC和芯片外部DRAM设备之间的数据传输。它通过一个或多个ACE-Lite接口连接到片上系统。它通过其存储器接口块和DFI接口连接到DRAM设备。

它实现了与以下协议的兼容:

-

ACE-Lite协议

-

AMBA3 APB协议

-

JEDEC LPDDR2 JESD209-2标准

-

JEDEC DDR3 JESD79-3D标准

-

JEDEC DDR2 JESD79-2E标准

-

DFI v2.1.1规范。

DMC400有以下特性:

-

可在Verilog中使用的软宏单元

-

可配置的硬件,支持面积和性能优化

-

多个ACE-Lite系统接口

-

多个未完成的交易

-

系统服务质量(QoS)和请求仲裁,以实现低延迟传输和内存带宽的最佳利用

-

对交易障碍的保护

-

ACE-Lite系统接口的可配置位宽

-

独立的读接受能力和写接受能力

-

AMBA ACE-Lite独占访问传输

-

ACE-Lite和APB接口之间的同步n:1时钟连接

-

多个内存接口

-

优化使用外部存储器总线

-

DRAM省电

-

可编程的外部存储器宽度

-

每个内存接口的可配置的内存芯片选择数量

-

用于64位和32位SDRAM的内存纠错码(ECC)。

-

使用DFI2.1.1接口的物理层(PHY)接口。

欢迎关注我的个人微信公众号,一起交流学习嵌入式开发知识!

关注「求密勒实验室」

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?