ICC学习——LAB1数据准备和基础流程

文章目录

学习目标:

1.完成数据准备,将设计数据保存到milkway中

2.从floorplan到route完整流程

预期效果:

1.为自己创建milkway

2.将参考库(reference library)链接至设计库(design library)

3.读入TLU+(plus)模型,提取寄生

4.读入网表

5.应用sdc约束

6.应用时序和优化控制

7.载入DEF格式的floorplan

8.使用place_opt完成place和优化操作

9.使用clock_opt建立并优化时钟树

10.使用route_opt布线优化

11.产生并读懂时序报告

12.在新对话中加载以前的设计

介绍:主要完成两部分工作,一部分利用netlist,sdc约束和floorplan创建Milkway 设计库(design library)。第二部分完成标准单元放置,创建CTS,并进行布线。

相关文件和目录

A:.synopsys_dc_setup

B:设计数据(Design Data)

Risc_chip.v ——网表文件

Risc_chip.def ——floorplan

Risc_chip.sdc ——时序约束

C:scripts 脚本

opt_ctrl.tcl——时序和优化控制

zic_timing.tcl(zic:zero interconnect )——检查零互联时序约束

derive_pg.tcl——创建PG 连接

D:solutions 解决方案

run.tcl 所有命令执行的脚本

Task1 创建Milkway库

1.目录移至工作目录

cd ../lab1_data_setup

ls -la

可以看到.synopsys_dc.setup文件,以.开头的文件在Linux下是不可见的。

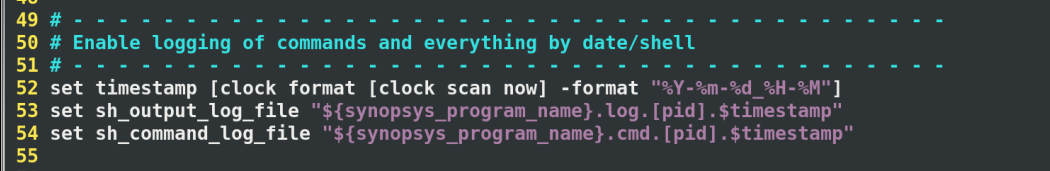

2.查看.synopsys_dc.setup

3.在.synopsys_dc.setup文件底部定义了变量

如:set my_mw_lib risc_chip.mw

如LAB0A实验中使用的printvar命令,如果忘记了可以使用此命令查看变量

4.在3中变量上方定义了逻辑库

如set_spp_var link_library set_min_library

上面设置了一些别名,正如在LAB0A中提到的,

也可以设置log文件的名字。

Note:定义的变量可以按照任何顺序应用。

5.退出.synopsys_dc.setup文本

6.从UNIX命令行启动ICC

icc_shell

在ICC终端启动时所有的输出都存放到log文件中

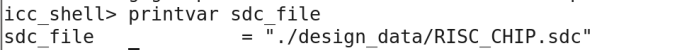

7.为了验证.synopsys_dc.setup文件已经被读了,可以通过查询其中的一个变量进行检测。

printvar sdc_file

8.启动GUI

start_gui

也可以直接输入gui,这个实验提前预设了脚本(设置在.synopsys_dc.setup中?不在,应该是主目录下的.synopsys_dc.setup)

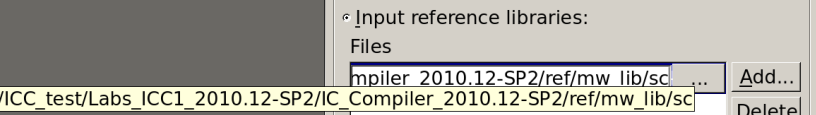

9.创建Milkway设计库

a:使用Main Window的菜单,File—>Create Library,挑出Create Library窗口

b:使用已经定义过的逻辑库名和工艺文件名(设置在.synopsys_dc.setup中?)

c:将参考库链接到设计库中。(参考库指的是物理库),将标准单元sc加入到设计库中

d:增加IO库和Macro库。“IO”和“ram 16*128”

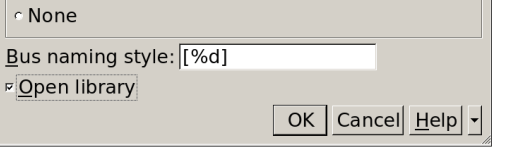

e:将“open library复选框勾上”,可以在设计库被创建后直接打开。

f:点击OK

Note:预计会出现关于“Missing CapModel Sections”的警告

忽略以上警告,之后会载入TLU+文件

查看Main Window中的命令,查看以上GUI操作对应的TCL命令

create_mw_lib -technology $tech_file -mw_reference_library "$mw_path/sc $mw_path/io $mw_path/ram16X128" -bus_naming_style{

[%d]} -open $my_mw_lib

10.在另一个终端或者在icc_shell执行以下命令,观察新创建的risc_chip.mw设计库的内容

ls -a risc_chip.mw

#或者

icc_shell > ls risv_chip.mw

Note:应该有3个lib文件和一个lock文件

Task2 载入netlist,TLU+,约束和控制

1.读入verilog网表钱,确保所有设计库是打开的,一个简单的方法去检查,目录打开File —>Open Library条目是否变黑,如果变黑了,当前库就处于打开状态。

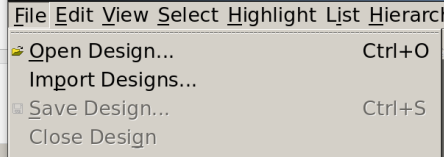

2.选择File —> Import Designs,打开导入设计对话框。

3.在输入形式(i

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1605

1605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?