结构描述: 用门来描述器件的功能;

primitives(基本单元) : Verilog语言已定义的具有简单逻辑功能的功能模型(models);基本单元是Verilog开发库的一部分。大多数ASIC和FPGA元件库是用这些基本单元开发的。基本单元库是自下而上的设计方法的一部分

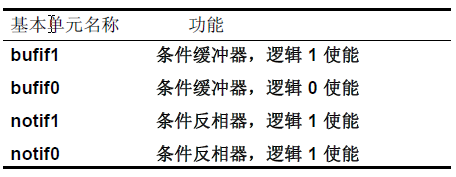

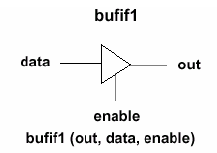

条件基本单元有三个端口:输出、数据输入、使能输入;Verilog有四种不同类型的条件基本单元

这四种基本单元只能有三个引脚:output, input, enable;

这些单元由enable引脚使能;

当条件基本单元使能信号无效时,输出高阻态

基本单元实例化:

在端口列表中,先说明输出端口,然后是输入端口;

实例化时实例的名字是可选项;

延迟说明和信号强度说明是可选项;

模块实例化(module instantiation)

模块

Verilog结构描述

最新推荐文章于 2024-01-18 09:26:29 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3784

3784

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?