0 概述

之前在windows环境下简单学习了Scala的基本语法,并在windos环境下安装了JVM环境和Scala编译器,运行了一些简单的Scala程序。今天开始正式搭建Chisel开发环境和学习Chisel,同时为了有利于后续的学习和开发,也是因为Chisel的工作环境对windows不太友好,所以后续的开发都会在linux上进行。

我这里选择的是使用的VMware搭建的虚拟机环境,版本为ubuntu 22.04,如果不确定版本号的可以使用

lsb_release -a进行查询。虚拟机的安装等等网上资源很多就不赘述了。

1 安装sbt

sbt(scala build tool)的Github网址:sbt Reference Manual — sbt Reference Manual (scala-sbt.org)

有兴趣的,可以在主页上查看,上边介绍的也很详细。大概的安装步骤包括:

- 安装JDK(推荐使用JDK8, 11或17版本)

- 安装sbt并运行

- 建立一个简单的“hello world”工程

- 学习如何使用sbt

- 到.sbt的构建定义下去了解更多关于构建的更多信息

1.1 安装JDK

安装JDK有两种方法,第一种方式是通过AdoptOpenJDK来安装,需要输入命令

sudo apt install openjdk-8-jdk git make gtkwave即可。

另一种方法是通过SDKMAN来安装和管理多个JDK版本,这也是sbt官网推荐的方法,它最大的好处就是可以使用sdk来直接安装sbt,非常的方便,但是经过多次尝试,一直无法成功安装SDKMAN,尽管SDKMAN和现有网站资料上都给出了一些教程,但都不外乎

curl -s "https://get.sdkman.io" | bash

source "$HOME/.sdkman/bin/sdkman-init.sh"

sdk version

sdk list java //查询sdk支持的java版本

sdk install java //安装最新的java版本

sdk install java **** //安装指定版本这些,在亲自尝试了多次之后:

首先是发现22.04版本没有预装curl,安装后再次运行遇到了各种各样的报错信息,先是无法连接github.com,增加hosts之后仍报错

curl: (56) Recv failure: Connection reset by peer 多次尝试无果后改为第一种直接安装JDK 8的方式,随后再单独安装sbt,如果有安装成功SDKMAN的非常希望可以给出一些建议,指出问题,感激不尽!

1.2 安装sbt

这里选择使用deb的形式安装,这里sbt - Download (scala-sbt.org)

也给出了其他安装更详细的教程。

echo "deb https://repo.scala-sbt.org/scalasbt/debian all main" | sudo tee /etc/apt/sources.list.d/sbt.list

echo "deb https://repo.scala-sbt.org/scalasbt/debian /" | sudo tee /etc/apt/sources.list.d/sbt_old.list

curl -sL "https://keyserver.ubuntu.com/pks/lookup?op=get&search=0x2EE0EA64E40A89B84B2DF73499E82A75642AC823" | sudo apt-key add

sudo apt-get update

sudo apt-get install sbt这里,作者亲自一一尝试过是可以完成安装的!

1.3 运行Scala程序

运行第一个Scala程序,从Hello world开始,新建一个文件夹中新建一个文件可以叫“hello.scala”,里边输入

object HelloScala extends App{

println("Hello Chisel World!")

}然后在当前文件夹下运行

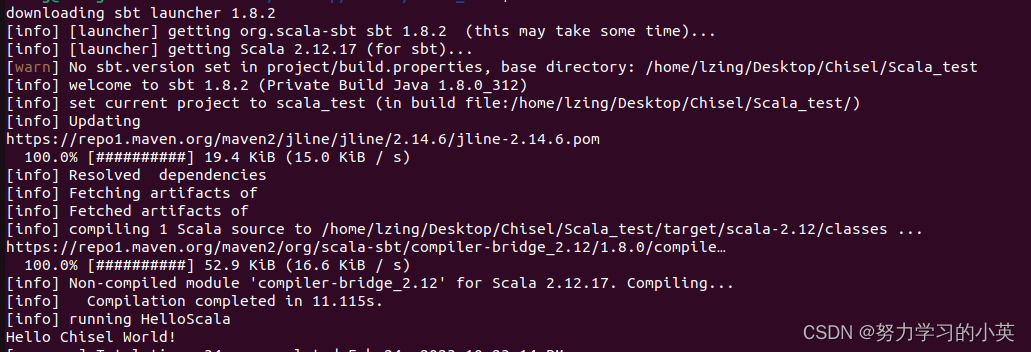

sbt run第一次运行可能需要花费比较长的时间,我这里话费了大概25分钟左右,因为第一次需要下载和编译很多链接,等之后几次再编译就快很多了。

可以看到,这里已经输出了Hello Chisel World,说明sbt已经成功安装完成了。

同时要注意,这仅仅是一个Scala代码并不是一个完整的Chisel代码,Chisel也仅是Scala中的一个库,要想正确使用并运行Chisel,还需要进行一些操作,如下。

2 安装一个开发工具

前边反复说到,Chisel其实就是Scala中的一个库,所有Scala的语法都能在Chisel上运行,而且Chisel也是依赖于Scala的编译工具的,所以实际上所有可用于Scala编写管理的开发工具都适用于Chisel,可以是使用一个文本编译器如gvim或vscode这类,也可以选择可以联想语法的IDEA。这其中安装一个自己比较喜欢的就可以了。

2.1 安装IDEA

网络上相关资源已经非常多了,给一个我觉得还不错的链接:Linux系统安装IDEA保姆级教程_linux安装idea_囧囧JOJO的博客-CSDN博客

2.2 安装VSCODE

同样,VSCODE的安装也非常的多:linux安装vscode_wasApp的博客-CSDN博客

3 运行一个Chisel的“Hello World”

之前学习C语言之类的软件描述语言的第一个程序一般都是“Hello World”,而使用硬件如单片机或FPGA则常常是点亮一个LED灯,所以本小节简单运行一个使用Chisel语言描述的LED闪烁程序。

3.1 下载实例程序

schoeberl/chisel-examples: Chisel examples and code snippets (github.com)

是官方收集的一个Chisel实例程序集合,我们首先要做的就是从Github上下载示例程序

git clone https://github.com/schoeberl/chisel-examples.git之后进入示例程序:

cd chisel-examples/hello-world/然后可以使用VSCODE等文本编译器在src/main/scala中查看源码,

/*

* This code is a minimal hardware described in Chisel.

*

* Blinking LED: the FPGA version of Hello World

*/

import chisel3._

/**

* The blinking LED component.

*/

class Hello extends Module {

val io = IO(new Bundle {

val led = Output(UInt(1.W))

})

val CNT_MAX = (50000000 / 2 - 1).U

val cntReg = RegInit(0.U(32.W))

val blkReg = RegInit(0.U(1.W))

cntReg := cntReg + 1.U

when(cntReg === CNT_MAX) {

cntReg := 0.U

blkReg := ~blkReg

}

io.led := blkReg

}

/**

* An object extending App to generate the Verilog code.

*/

object Hello extends App {

(new chisel3.stage.ChiselStage).emitVerilog(new Hello())

}3.2 运行示例程序

由于现有的大部分EDA软件并没有很好的支持Chisel,所以要想让编写的Chisel代码能够在FPGA或EDA软件上编译综合等,需要先将Chisel代码专为你verilog代码,在hello-world文件下打开命令行:

sbt run等待运行完成后会在当前目录下生成一个Hello.v文件,即Chisel代码对应的verilog文件:

module Hello(

input clock,

input reset,

output io_led

);

`ifdef RANDOMIZE_REG_INIT

reg [31:0] _RAND_0;

reg [31:0] _RAND_1;

`endif // RANDOMIZE_REG_INIT

reg [31:0] cntReg; // @[Hello.scala 19:23]

reg blkReg; // @[Hello.scala 20:23]

wire [31:0] _cntReg_T_1 = cntReg + 32'h1; // @[Hello.scala 22:20]

assign io_led = blkReg; // @[Hello.scala 27:10]

always @(posedge clock) begin

if (reset) begin // @[Hello.scala 19:23]

cntReg <= 32'h0; // @[Hello.scala 19:23]

end else if (cntReg == 32'h17d783f) begin // @[Hello.scala 23:28]

cntReg <= 32'h0; // @[Hello.scala 24:12]

end else begin

cntReg <= _cntReg_T_1; // @[Hello.scala 22:10]

end

if (reset) begin // @[Hello.scala 20:23]

blkReg <= 1'h0; // @[Hello.scala 20:23]

end else if (cntReg == 32'h17d783f) begin // @[Hello.scala 23:28]

blkReg <= ~blkReg; // @[Hello.scala 25:12]

end

end

// Register and memory initialization

`ifdef RANDOMIZE_GARBAGE_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_INVALID_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_REG_INIT

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_MEM_INIT

`define RANDOMIZE

`endif

`ifndef RANDOM

`define RANDOM $random

`endif

`ifdef RANDOMIZE_MEM_INIT

integer initvar;

`endif

`ifndef SYNTHESIS

`ifdef FIRRTL_BEFORE_INITIAL

`FIRRTL_BEFORE_INITIAL

`endif

initial begin

`ifdef RANDOMIZE

`ifdef INIT_RANDOM

`INIT_RANDOM

`endif

`ifndef VERILATOR

`ifdef RANDOMIZE_DELAY

#`RANDOMIZE_DELAY begin end

`else

#0.002 begin end

`endif

`endif

`ifdef RANDOMIZE_REG_INIT

_RAND_0 = {1{`RANDOM}};

cntReg = _RAND_0[31:0];

_RAND_1 = {1{`RANDOM}};

blkReg = _RAND_1[0:0];

`endif // RANDOMIZE_REG_INIT

`endif // RANDOMIZE

end // initial

`ifdef FIRRTL_AFTER_INITIAL

`FIRRTL_AFTER_INITIAL

`endif

`endif // SYNTHESIS

endmodule

运行到这里就已经说明Chisel代码已经可以运行了,接下来的主要任务就是熟悉sbt、熟悉idea、熟悉Chisel语法以及学习其他相关知识。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?