1、MOS的三个极怎么判定?

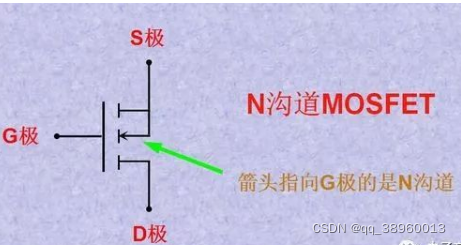

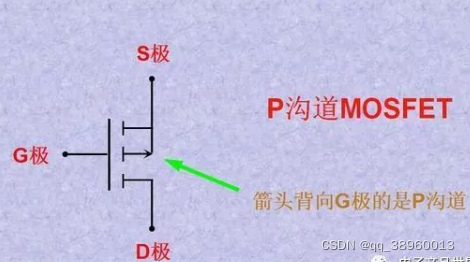

MOS管符号上的三个脚的辨认要抓住关键地方 :

G极:门控引脚脚这个比较好辨认,T字型的就是。

S极:不论是P沟道还是N沟道,两根线相交的就是。

D极:不论是P沟道还是N沟道,是单独引线的那边。

2、判断他们是N沟道还是P沟道?

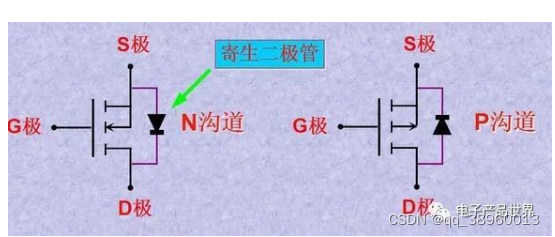

3、寄生二极管的方向判断

N沟道:S指向D极

P沟道:D指向S极

4、Mosfet 参数选型

1. 选用N沟道还是P沟道

为设计选择正确器件的第一步是决定采用N沟道还是P沟道MOS管。

在典型的功率应用中,当一个MOS管接地,而负载连接到干线电压上时,该MOS管就构成了低压侧开关。在低压侧开关中,应采用N沟道MOS管,这是出于对关闭或导通器件所需电压的考虑。

当MOS管连接到总线及负载接地时,就要用高压侧开关。通常会在这个拓扑中采用P沟道MOS管,这也是出于对电压驱动的考虑。

一般来说,N沟道比P沟道便宜。因此从节约成本的角度出发,选用N沟道。

2. 确定耐压值

要选择适合应用的器件,必须确定驱动器件所需的电压。

因此第二步是确定所需的额定电压,或者器件所能承受的最大电压。额定电压越大,器件的成本就越高。根据实践经验,额定电压应当大于干线电压或总线电压。这样才能提供足够的保护,使MOS管不会失效。

就选择MOS管而言,必须确定漏极至源极间可能承受的最大电压,即最大VDS。反映在MOS管的datasheet中如下图所示。

知道MOS管能承受的最大电压会随温度而变化这点十分重要。设计人员必须在整个工作温度范围内测试电压的变化范围。额定电压必须有足够的余量覆盖这个变化范围,确保电路不会失效。设计工程师需要考虑的其他安全因素包括由开关电子设备(如电机或变压器)诱发的电压瞬变。不同应用的额定电压也有所不同;通常,便携式设备为20V、FPGA电源为20~30V、85~220VAC应用为450~600V。

3. 确定额定电流

第三步是选择MOS管的额定电流。视电路结构而定,该额定电流应是负载在所有情况下能够承受的最大电流。

与电压的情况相似,设计人员必须确保所选的MOS管能承受这个额定电流,即使在系统产生尖峰电流时。两个考虑的电流情况是连续模式和脉冲尖峰。在连续导通模式下,MOS管处于稳态,此时电流连续通过器件。脉冲尖峰是指有大量电涌(或尖峰电流)流过器件。一旦确定了这些条件下的最大电流,只需直接选择能承受这个最大电流的器件便可。反映在MOS管的datasheet中如下图所示。

选好额定电流后,还必须计算导通损耗。在实际情况下,MOS管并不是理想的器件,因为在导电过程中会有电能损耗,这称之为导通损耗。MOS管在“导通”时就像一个可变电阻,由器件的RDS(ON)所确定,并随温度而显著变化。器件的功率耗损可由Iload2×RDS(ON)计算,由于导通电阻随温度变化,因此功率耗损也会随之按比例变化。对MOS管施加的电压VGS越高,RDS(ON)就会越小;反之RDS(ON)就会越高。对系统设计人员来说,这就是取决于系统电压而需要折中权衡的地方。对便携式设计来说,采用较低的电压比较容易(较为普遍),而对于工业设计,可采用较高的电压。注意RDS(ON)电阻会随着电流轻微上升。关于RDS(ON)电阻的各种电气参数变化可在制造商提供的技术资料表中查到。

技术对器件的特性有着重大影响,因为有些技术在提高最大VDS时往往会使RDS(ON)增大。对于这样的技术,如果打算降低VDS和RDS(ON),那么就得增加晶片尺寸,从而增加与之配套的封装尺寸及相关的开发成本。业界现有好几种试图控制晶片尺寸增加的技术,其中最主要的是沟道和电荷平衡技术。

在沟道技术中,晶片中嵌入了一个深沟,通常是为低电压预留的,用于降低导通电阻RDS(ON)。为了减少最大VDS对RDS(ON)的影响,开发过程中采用了外延生长柱/蚀刻柱工艺。例如,飞兆半导体开发了称为SupeRFET的技术,针对RDS(ON)的降低而增加了额外的制造步骤。这种对RDS(ON)的关注十分重要,因为当标准MOSFET的击穿电压升高时,RDS(ON)会随之呈指数级增加,并且导致晶片尺寸增大。SuperFET工艺将RDS(ON)与晶片尺寸间的指数关系变成了线性关系。这样,SuperFET器件便可在小晶片尺寸,甚至在击穿电压达到600V的情况下,实现理想的低RDS(ON)。结果是晶片尺寸可减小达35%。而对于最终用户来说,这意味着封装尺寸的大幅减小。

4. 确定热要求

选择MOS管的下一步是计算系统的散热要求。设计人员必须考虑两种不同的情况,即最坏情况和真实情况。建议采用针对最坏情况的计算结果,因为这个结果提供更大的安全余量,能确保系统不会失效。在MOS管的资料表上还有一些需要注意的测量数据;比如封装器件的半导体结与环境之间的热阻,以及最大的结温。

器件的结温等于最大环境温度加上热阻与功率耗散的乘积(结温=最大环境温度+[热阻×功率耗散])。根据这个方程可解出系统的最大功率耗散,即按定义相等于I2×RDS(ON)。由于设计人员已确定将要通过器件的最大电流,因此可以计算出不同温度下的RDS(ON)。值得注意的是,在处理简单热模型时,设计人员还必须考虑半导体结/器件外壳及外壳/环境的热容量;即要求印刷电路板和封装不会立即升温。

雪崩击穿是指半导体器件上的反向电压超过最大值,并形成强电场使器件内电流增加。该电流将耗散功率,使器件的温度升高,而且有可能损坏器件。半导体公司都会对器件进行雪崩测试,计算其雪崩电压,或对器件的稳健性进行测试。计算额定雪崩电压有两种方法;一是统计法,另一是热计算。而热计算因为较为实用而得到广泛采用。除计算外,技术对雪崩效应也有很大影响。例如,晶片尺寸的增加会提高抗雪崩能力,最终提高器件的稳健性。对最终用户而言,这意味着要在系统中采用更大的封装件。

5. 确定开关性能

选择MOS管的最后一步是决定MOS管的开关性能。影响开关性能的参数有很多,但最重要的是栅极/漏极、栅极/ 源极及漏极/源极电容。这些电容会在器件中产生开关损耗,因为在每次开关时都要对它们充电。MOS管的开关速度因此被降低,器件效率也下降。为计算开关过程中器件的总损耗,设计人员必须计算开通过程中的损耗(Eon)和关闭过程中的损耗(Eoff)。MOSFET开关的总功率可用如下方程表达:Psw=(Eon+Eoff)×开关频率。而栅极电荷(Qgd)对开关性能的影响最大。

————————————————

版权声明:本文为CSDN博主「吮指原味张」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/mahoon411/article/details/116981291

https://blog.csdn.net/qq_53649853/article/details/121474026?spm=1001.2101.3001.6650.2&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-2.pc_relevant_default&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-2.pc_relevant_default&utm_relevant_index=5

657

657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?