笔者语:

这是硬缸系列的第二集,今年(划去)春节前我一定会把它补完的(FLAG)

这是硬缸系列的第二集第一部分,MOSFET的特性与选择。

长期连载,这个系列的其他集点击这里

写这篇文章的时候,我参考了大量的文章,这些文章通常来自值得信赖的电子元件公司或权威的EE杂志。在一些地方,我引用了他们的 图片(假如您是图片的作者,觉得不合适,可以及时的E-MAIL我),感谢这些工程师的工作。有一些文章,没有做出引用但是同样很有帮助,我也一并放在下面(小服务器放不下,大家可以自行搜索,后续有时间可能会做一些翻译工作,到时候再放出)。

参考资料:

TI:

《History of FET technology and the move to NexFET™》

《看懂MOSFET数据表》

ON-SEMI:

AN-6099:《采用屏蔽式栅极技术的新型 PowerTrench®MOSFET 提高同步整流 应用的系统效率和功率密度》

AN-9010:《MOSFET Basics》

AN-9034 功率 MOSFET 雪崩应用指南

ST:

SILICA-STDay-MotorControl-2015/LV_F7_EMI.pdf

MOSFET(金属氧化物半导体场效应晶体管),是近年来大量使用的分立半导体器件。

随着技术的不断提高,民用市场的爆发等多重因素的影响下,我们可以看到650V以及100V以下的MOS产品越来越丰富(主要用于移动电源和适配器)。封装技术也在不断升级,我们可以看到现在不少IC可以内置功率MOS,这在以前是不可想象的(因为二者的工艺完全不一样)。

!!!!下列涉及的MOS技术参数,都是需要注明在一定的条件下测得才有意义!!!!

!!!!下列涉及的MOS技术参数,都是需要注明在一定的条件下测得才有意义!!!!

!!!!下列涉及的MOS技术参数,都是需要注明在一定的条件下测得才有意义!!!!

注:模电课介绍MOSFET时常常将他用于放大器,但是实际生产实践中,一般用作开关的会更多一些。此文也只着重介绍其作为开关时的一些特性。

一、结构

MOSFET的结构决定了他的具体性能的上限。多年以来,人类的科技树主要发展了低压MOS,高压MOS以及宽禁带半导体。

一般认为,05年之前,主要是发展了半导体器件技术,05年之后,主要是发展了封装/散热技术,以及系统集成技术。

人类点科技树,无非就是这么几点:

-更低的RDSon、Vce(sat)、Qg、Qoss、Eoss、成本

-更优异的体二极管Qrr、trr、Irrm

-更强的EAS能力、短路能力、耐冲击能力

-更小的寄生参数

-更好的散热能力

-更容易驱动

这其中的大多数参数都是与半导体技术密不可分的。

值得一提的是,书上所能见到的那种MOS结构的示意图,其实根本没啥载流能力,商业化MOS一般是把许许多多这样的小结构(称为晶胞,一般长六边形,好像是IR的专利来的),并联起来。就像下图这张NXP的2N7002一样。(图源:https://zeptobars.com/en/read/NXP-2N7002-TrenchMOS-N-Channel-MOSFET)

低压MOS方面,早期主要是TrenchFET,后来出现了Optimos和NexFET,分别是英飞凌和TI家的技术。

左:传统的TrenchFET,右:NexFET。

TrenchFET 技术的广泛使用是由于它替代平面技术的特定管芯尺寸下具有极低的导通电阻,唯一的不足就是寄生电容通常会有所增加。面积比较大的沟道墙使它很难降低内部的寄生电容。

TI通过收购一家称作CICLON的半导体公司而获得的NexFET 技术,其可以获得与 TrenchFET技 术相似的导通电阻,而相应的寄生电容大约降低 50% 。器件底部侧面的扩散 MOS(LDMOS:横向扩散金属氧化物半导体)和垂直流动电流可以得到很高的电流密度。图 1 所示的结构显示出栅极下面的面积在源极区和漏极区重叠得很少,这就使得内部寄生电容很小。寄生电容的降低会使开关时的电荷(Qg、Qgs、Qgd)降低。因此,器件的开关速度会更快,也降低了 MOSFET 中的开关损耗。同时,驱动电路所需要的能量也比较低,这也降低了驱动器中的损耗。

而英飞凌的Optimos主要用的是屏蔽栅技术,ON-SEMI因为收购了仙童半导体获得的MOS技术也是屏蔽栅,有意思的是完成对仙童收购的安森美在电源产品上仅次于收购了IR的英飞凌。

Optimos技术特点:

利用实现电荷平衡原理引入水平耗尽,降低Rsp,提高击穿电压 。

由于屏蔽栅的存在,极大降低了米勒电容Cgd;

栅极电荷小,开关损耗小,降低驱动损耗,提高开关速度;

特征导通Rsp电阻小;成本更低。

Optimos结构示意图

Optimos实际结构的X光成像

二、安全

写在最前,永远记得:MOSFET只有一种死法:(结温)过热!!!

任何半导体器件都应该第一关注的是安全性,即:我选择的器件能不能在这个环境下进行工作。

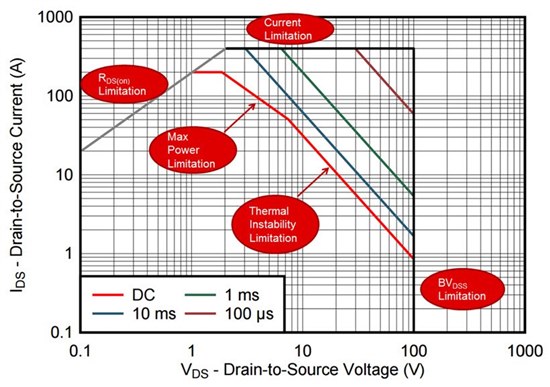

如何判断?条件众多,且显然是一个相与的关系,简单的逻辑分析后,我们不难得到最基本的几条红线:过压,过流,过热,这也是我们引入安全工作区 (SOA) 曲线的原因。

典型的SOA曲线

可以看到它的边界都由一些器件的极限参数(红圈)所框定。一般来说,只要器件工作在SOA曲线内,都是安全的。但是实际设计中,考虑到厂商的不老实(更改测试条件、标的是测试中遇到的最大值等等),以及一些突发的浪涌和脉冲,都是需要留出一定的余量的。

当然,实际的MOS工作环境一般都比较恶劣,工况各不相同,一条单纯的SOA曲线并不能很好的说明全部的问题。我们需要一些其他的参数。

无钳位电感开关 (UIS) 额定值便应运而生,并且从它在PowerMOS的Datasheet中被广泛测试和发布之时,就一直很好用。(前提是厂家没有在测试条件上作假)

众所周知,半导体器件一般都存在着雪崩击穿这一现象,雪崩击穿时Vds被钳位,且单纯的雪崩击穿可恢复,所以在生产实践中,MOS的雪崩击穿被工程师们广泛的运用。自然而然的,如果有一套评价体系,可以定量的测量MOS雪崩击穿的能力,那么他的测试数值就能很好的反应一个MOS是否“皮实耐操”。20世纪80年代中期,单脉冲UIS评估体系便这样被广泛的使用了。

该UIS评估体系仅要求用户确定流经PowerMOS晶体管的峰值电流(IAS)、UIS脉冲起始时刻的结温(TJ),以及晶体管处于雪崩状态的时间(tAV)。它允许确定任意应用是否符合特定UIS能力,并且可对最差情况进行仿真,同时还能非常灵活地计算尚未搭建的电路UIS应力,或计算不容易仿真的条件。

UIS测试由下图中所示的测试电路执行。在FET关闭时,其上施加了一个电源电压,然后检查器件上是否有泄露。在FET接通时,电感器电流稳定增加。当达到所需的电流时,FET被关闭,FET上的Ldi/dt电压摆幅在MOSFET击穿电压之上,从而激活了其内在的寄生双极晶体管,并在FET上出现有效的雪崩效应。这项测试重复进行,电流逐渐增加,直到一开始的泄漏测试失败,表明器件已被损坏。

UIS测试电路

方程式E = ½ LI2 计算的是FET的雪崩能量。这是测试的开始。通过改变电感器尺寸,你能够更改受测器件上施加的应力。可以预见的是,电感器越大,损坏FET所需的UIS电流越低。然而,这个较小的电流不会被方程式(用于计算雪崩能量)中电感器增加的尺寸抵消,这样的话,尽管电流减少了,这个值实际上是增加了。

查到的资料显示,TI使用0.1mH电感器来测试所有即将投入量产的器件,并且在FET数据表内给出与之相关的能量值。不排除其他厂家使用更大的电感进行测试来伪造更好看的UIS的纸面数据。

UIS的数值是一方面,但是很多时候MOS往往处于DC脉冲的状态(超过100ms),这时,我们就应该更关注的是器件的ID了

观察一个典型的MOS的datasheet,你一定会发现,几乎每个MOS的ID都被细分成了几项。

我们以TI公司的CSD18532为例,你会发现TI公司的MOS同样是CSD18532,会有不同的后缀,比如KCS,Q5B.虽然我还没能从官方那确认,KCS和Q5B里面的DIE是同款,但是我觉得可能性很大。

打开他们的datasheet:

http://www.ti.com/cn/lit/ds/symlink/csd18532q5b.pdf

http://www.ti.com/cn/lit/ds/symlink/csd18532kcs.pdf

我们可以看到电流的参数有封装限制电流和芯片限制电流还有脉冲漏极电流三种。下图左为Q5B后缀(SON封装)的,右图为KCS后缀(TO-220封装)

产生数据差异的主要原因是不同封装的散热能力不同。

而且实际中我们一般都需要对对应的参数进行降额处理。

三、损耗

MOSFET 作为开关使用时的主要损耗包括开关损耗、传导损耗、体二极管损耗和栅极驱动损耗。

开关损耗主要是由器件本身结构的寄生电容产生的。

传导损耗是器件工作在增强模式时由导通电阻(RDS(on))产生的。

体二极管损耗是正向电压和反向恢复电荷(Qrr)的函数。

栅极驱动损耗由 MOSFET 的栅电荷(Qg)决定。

因此,寄生电容和导通电阻(RDS(on))决定了器件在特定应用中的性能。

四、封装与热性能

对MOS来说,封装对他的影响主要是带来的寄生参数和散热效果的改变。

不外乎:

更小的寄生电感

更紧凑的尺寸

更好的散热能力

更大的电流承载能力

更高的可靠性

3412

3412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?