实现功能

想验证不是25M频率情况下,LED的显示模式

硬件

Xilinx Spartan6

软件

ISE 14.6,就是下面几个,不是Vivado哦,因为芯片版本低,只能用这个软件(又是蠢哭的一天)

代码

主例化程序(我也不知道该怎么叫,就酱吧)

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 20:40:24 11/19/2021

// Design Name:

// Module Name: PllControlLedCombFre

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module PllControlLedCombFre(

input extrst,

input extclk,

output [7:0] led

);

wire clk25m; //定义12.5MHZ例化信号

wire clk12m5; //定义12.5MHZ例化信号

wire clk50m; //定义50MHZ例化信号

wire clk100m; //定义100MHZ例化信号

wire clk45m; //定义45MHZ例化信号

wire pllrst; //定义PLL分频器的复位引脚

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

ledControler instance_name

(// Clock in ports

.CLK_IN1(extclk), // IN

// Clock out ports

.CLK_OUT1(clk25m), // OUT

.CLK_OUT2(clk12m5), // OUT

.CLK_OUT3(clk50m), // OUT

.CLK_OUT4(clk100m), // OUT

.CLK_OUT5(clk45m), // OUT

// Status and control signals

.RESET(!extrst),// IN

.LOCKED(pllrst)); // OUT

// INST_TAG_END ------ End INSTANTIATION Template ---------

//开始例化

//例化25M分频频率 其中n值设为#(24)即24位计数 即2^24 = 16_777_216 | 25M = 25_000_000

ledControlComb #(24) instanceLedControlclk25m(

.instanceclk(clk25m),

.instancerst(pllrst),

.instanceled(led[2])

);

//例化12.5M分频频率 其中n值设为#(23)即23位计数 即2^23 = 8_388_608 | 12.5M = 12_500_000

ledControlComb #(23) instanceLedControlclk12m5(

.instanceclk(clk12m5),

.instancerst(pllrst),

.instanceled(led[0])

);

//例化50M分频频率 其中n值设为#(25)即25位计数 即2^25 = 33_554_432 | 50M = 50_000_000

ledControlComb #(25) instanceLedControlclk50m(

.instanceclk(clk50m),

.instancerst(pllrst),

.instanceled(led[4])

);

//例化100M分频频率 其中n值设为#(26)即26位计数 即2^26 = 67_108_864 | 100M = 100_000_000

ledControlComb #(26) instanceLedControlclk100m(

.instanceclk(clk100m),

.instancerst(pllrst),

.instanceled(led[6])

);

//例化145M分频频率 其中n值设为#(25)即25位计数 即2^25 = 33_554_432 | 45M = 45_000_000

ledControlComb #(25) instanceLedControlclk45m(

.instanceclk(clk100m),

.instancerst(pllrst),

.instanceled(led[7])

);

assign led[1] = 1'b1;

assign led[3] = 1'b1;

assign led[5] = 1'b1;

endmodule

分例化程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 21:01:47 11/19/2021

// Design Name:

// Module Name: ledControlComb

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module ledControlComb(

input instancerst,

input instanceclk,

output instanceled

);

parameter instanceCnt = 24;

reg [instanceCnt - 1:0] cnt;

always @ (posedge instanceclk or negedge instancerst)

if(!instancerst) cnt <= 24'd0;

else cnt <= cnt + 1'b1;

assign instanceled = cnt[instanceCnt - 1];

endmodule

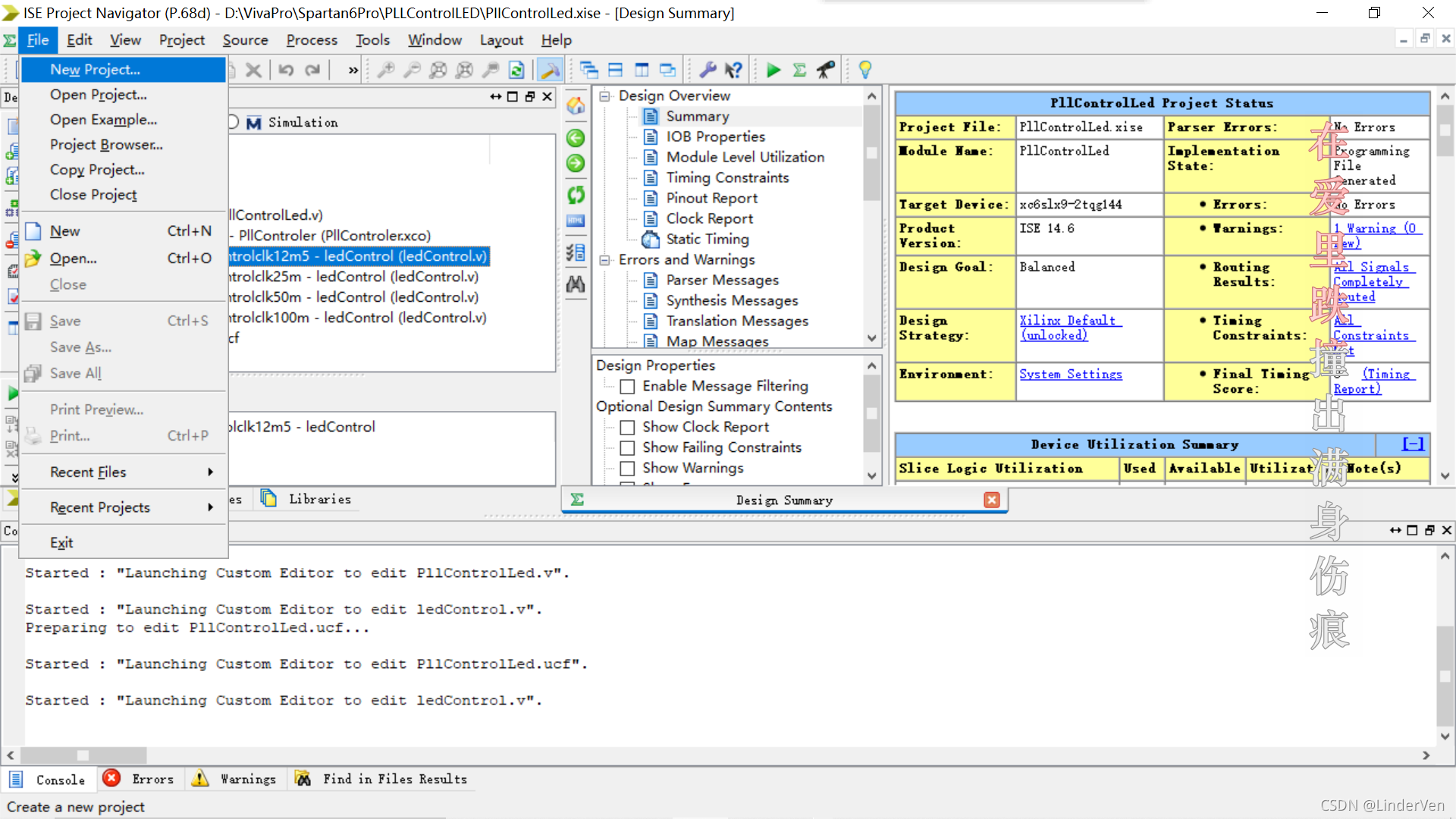

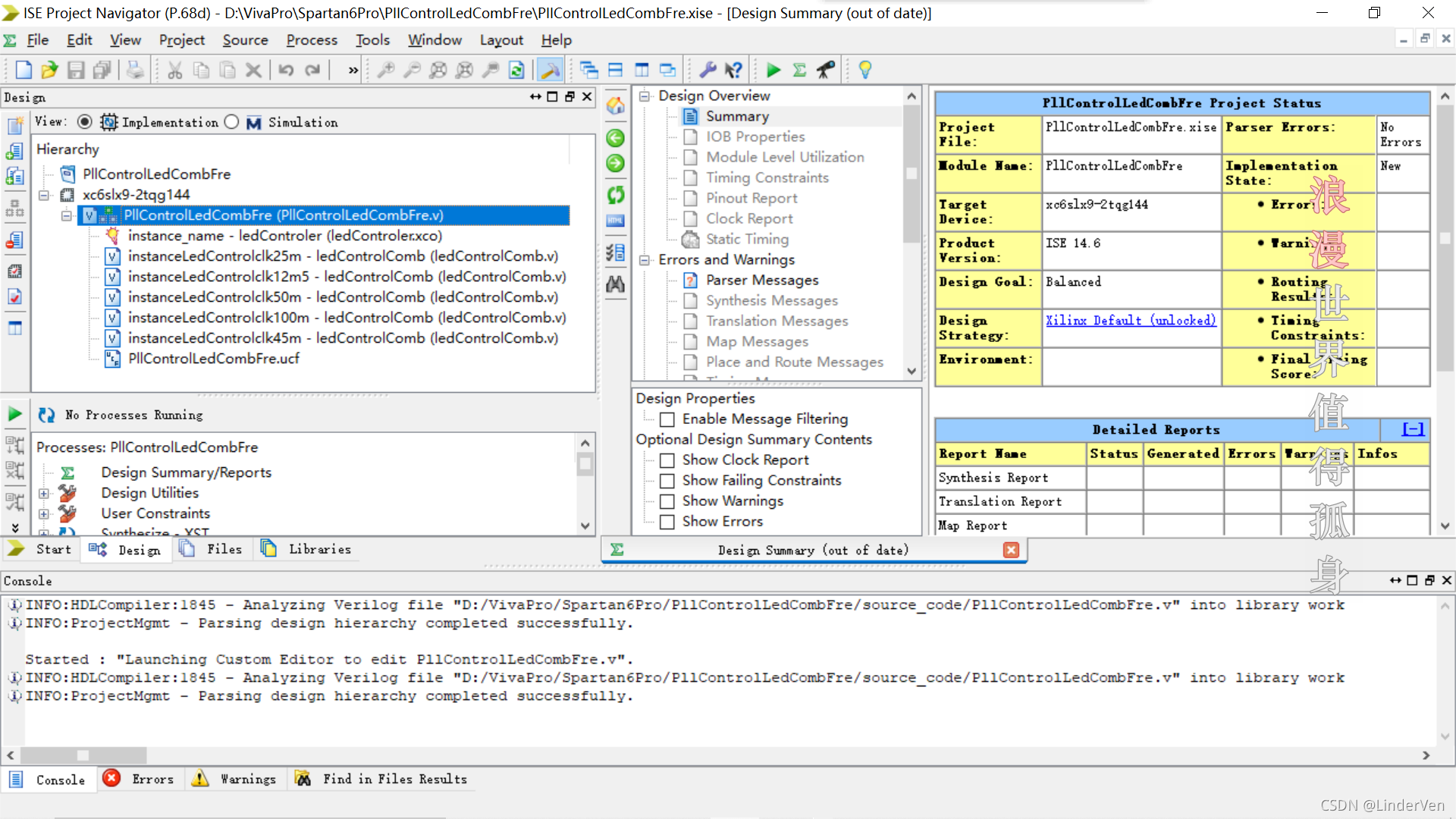

从创建工程讲起(long long ago~~~~)

有点多,图片中代码不一定对,但是上面的代码一定对,因为会出错,要调试,,,

创建工程

上面就是创建工程,不用多说,非常熟悉了

上面就是创建工程,不用多说,非常熟悉了

中间还有个选择文件类型的页面,没截下来,选Verilog啥啥的,下面还有机会不急

中间还有个选择文件类型的页面,没截下来,选Verilog啥啥的,下面还有机会不急

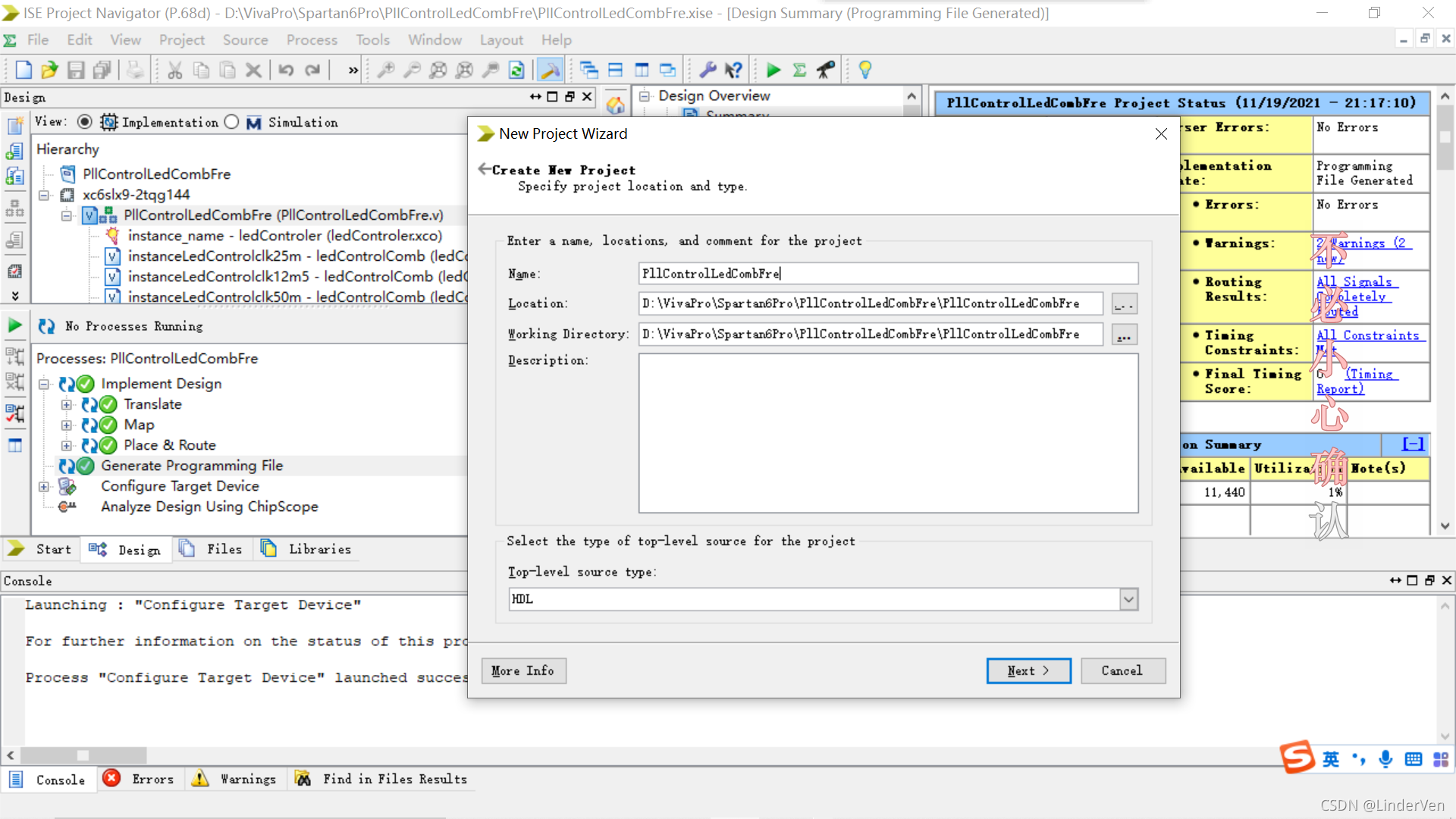

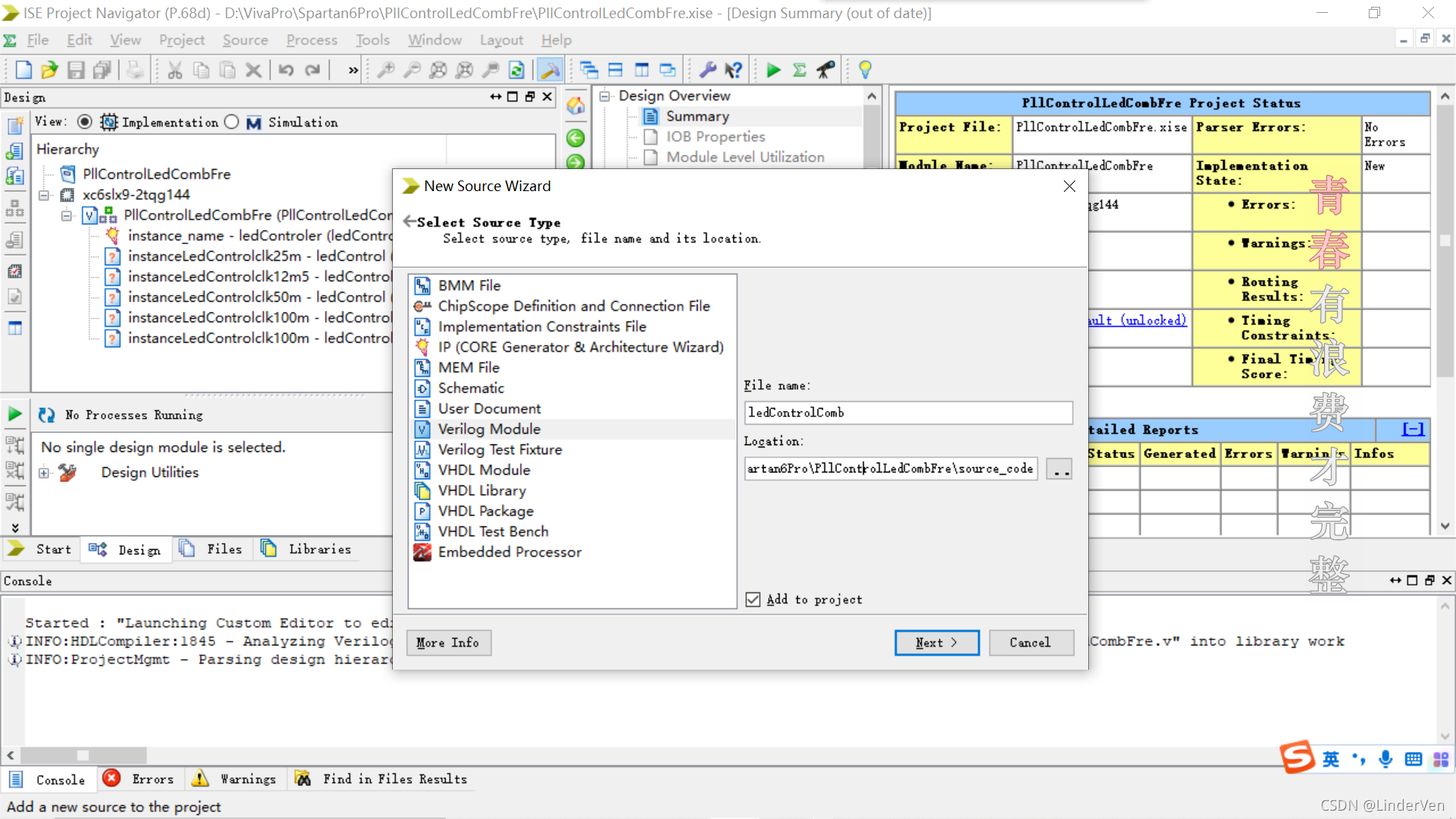

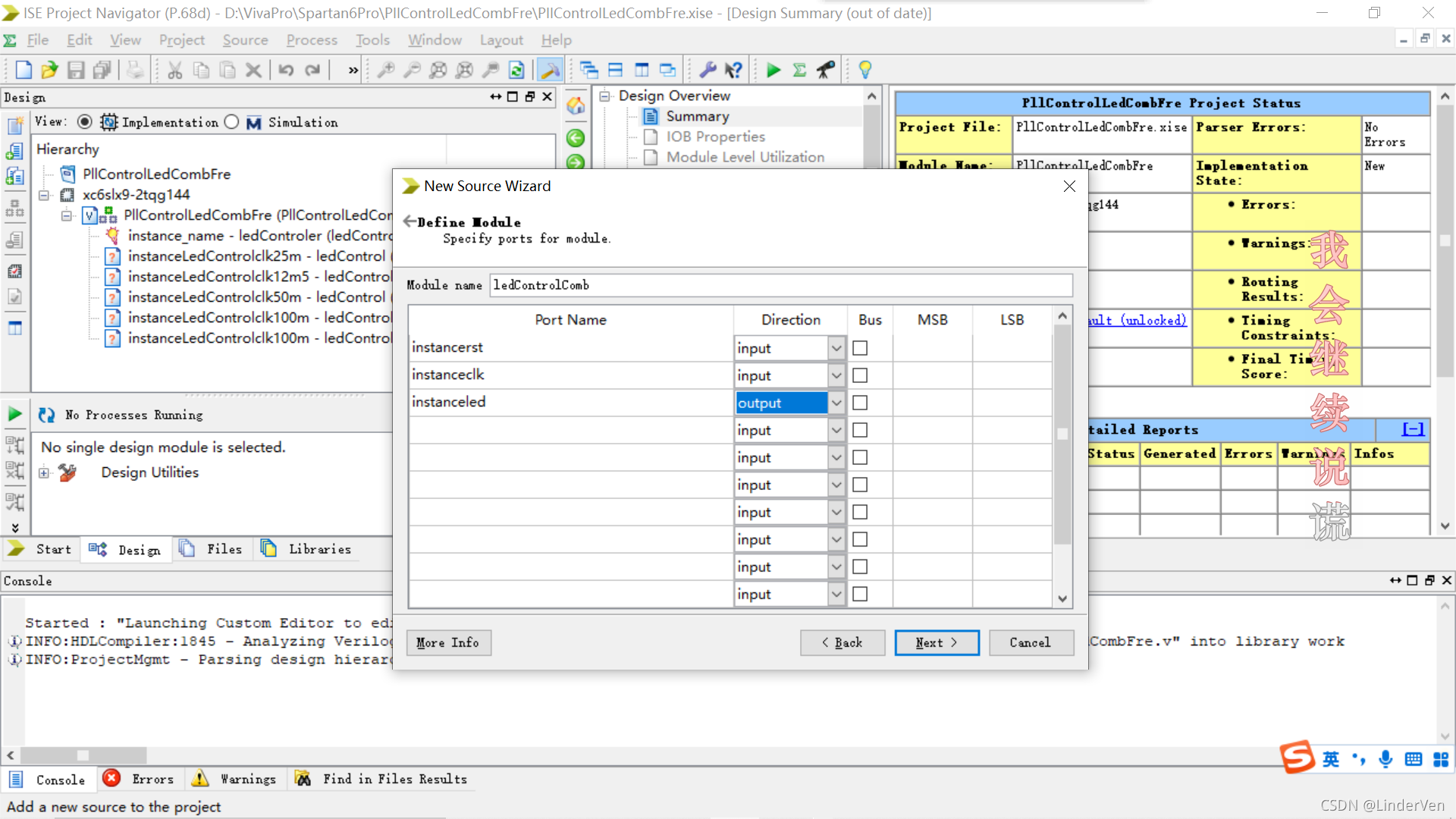

这个就是相关的文件名,文件路径设置,应该也没问题

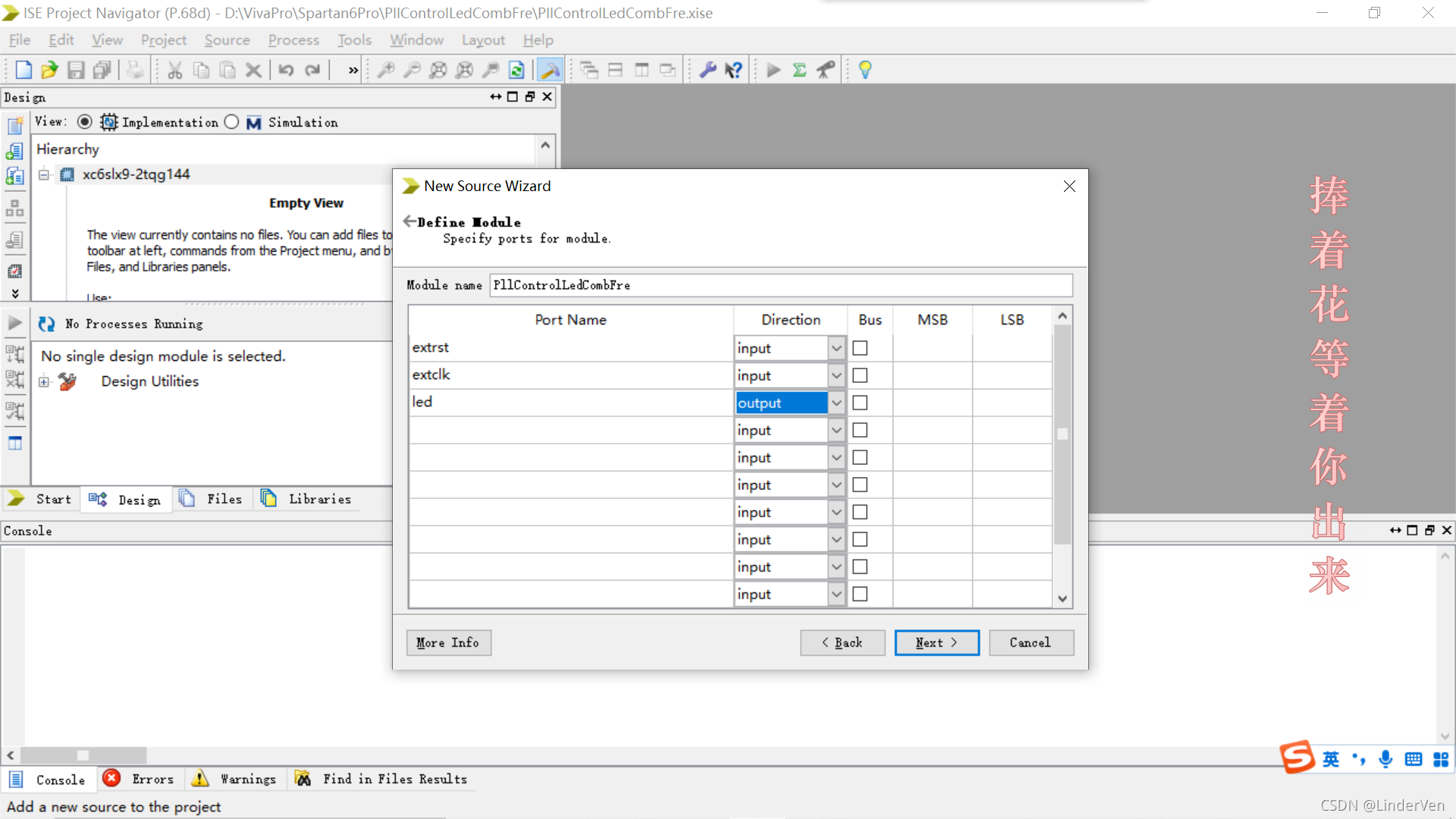

设置好路径文件名后,会弹出来个这个,让你设置你的引脚,一般程序中用什么引脚设置什么引脚(注意输入输出的选择)

设置好路径文件名后,会弹出来个这个,让你设置你的引脚,一般程序中用什么引脚设置什么引脚(注意输入输出的选择)

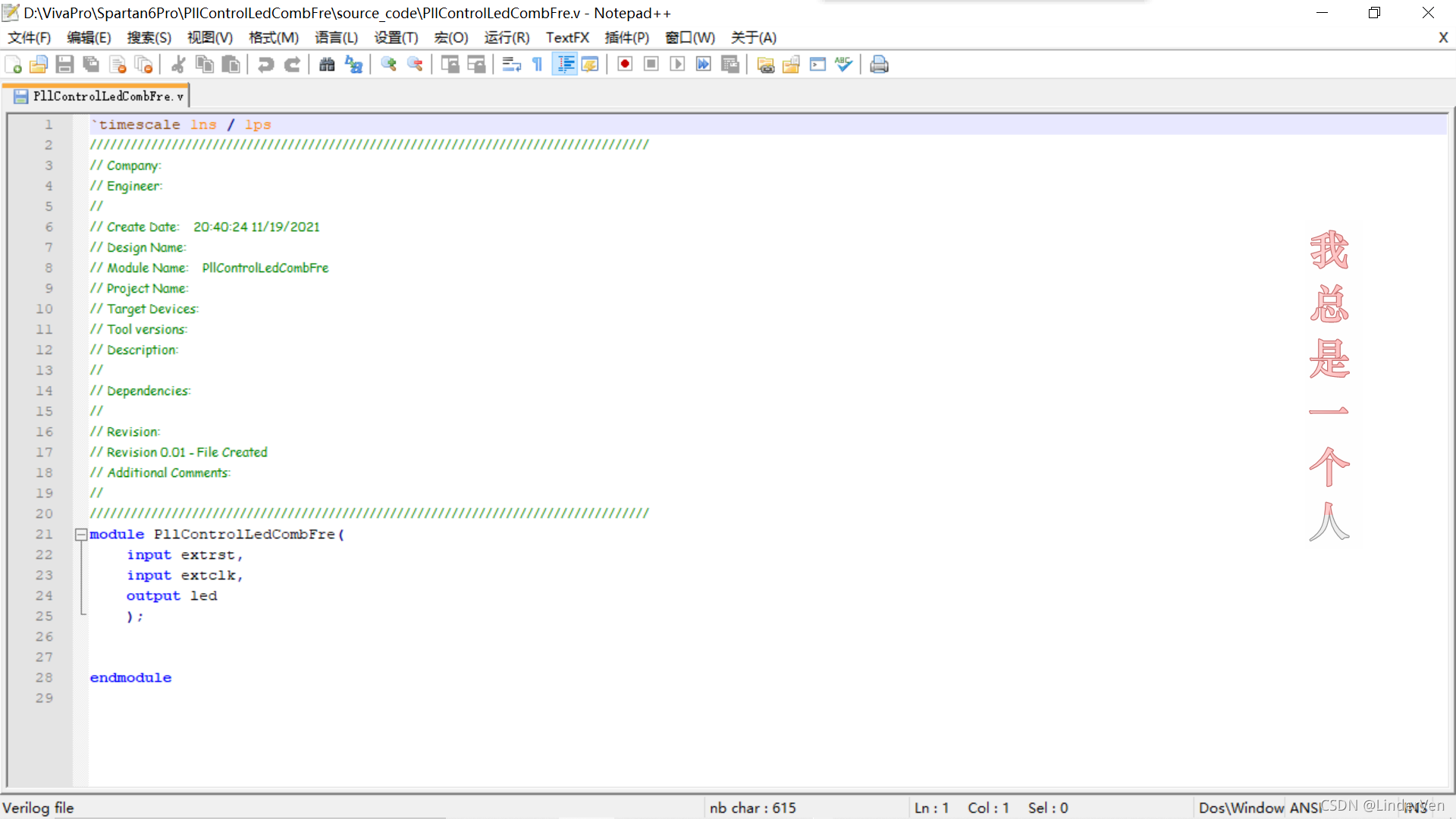

这个就是你设置好引脚啥的后,系统给你分配的初始化的文件,当然有需要的话还得改改,不是一定不能动的哦(可以改的)

这个就是你设置好引脚啥的后,系统给你分配的初始化的文件,当然有需要的话还得改改,不是一定不能动的哦(可以改的)

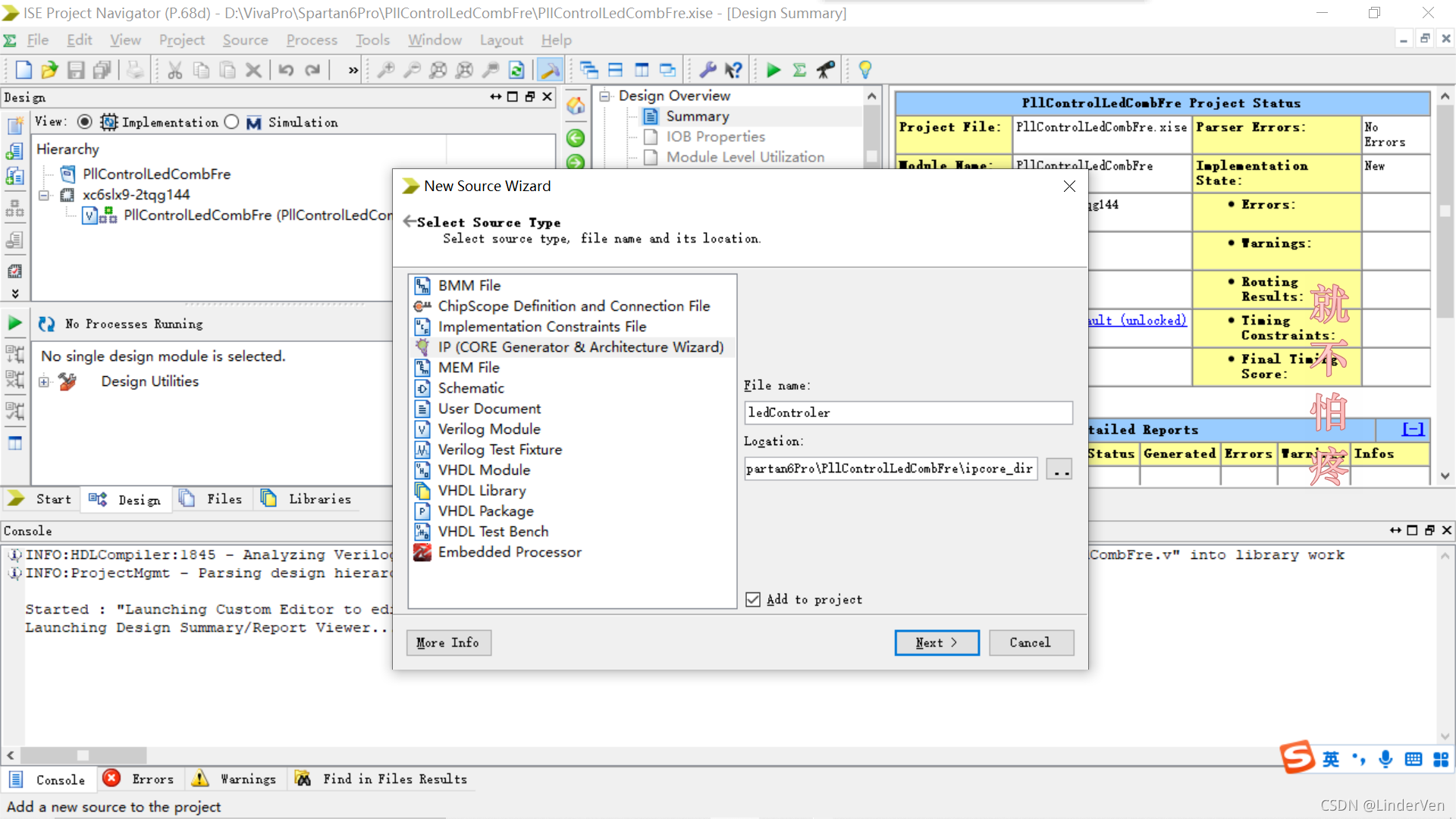

创建IP核文件

呐呐呐,就是这个忘了截(上面提到的)上面那个选择verilog module类型的,咱这个不是,这次是要建一个IP核文件,这次是要建一个IP核文件,这次是要建一个IP核文件

呐呐呐,就是这个忘了截(上面提到的)上面那个选择verilog module类型的,咱这个不是,这次是要建一个IP核文件,这次是要建一个IP核文件,这次是要建一个IP核文件

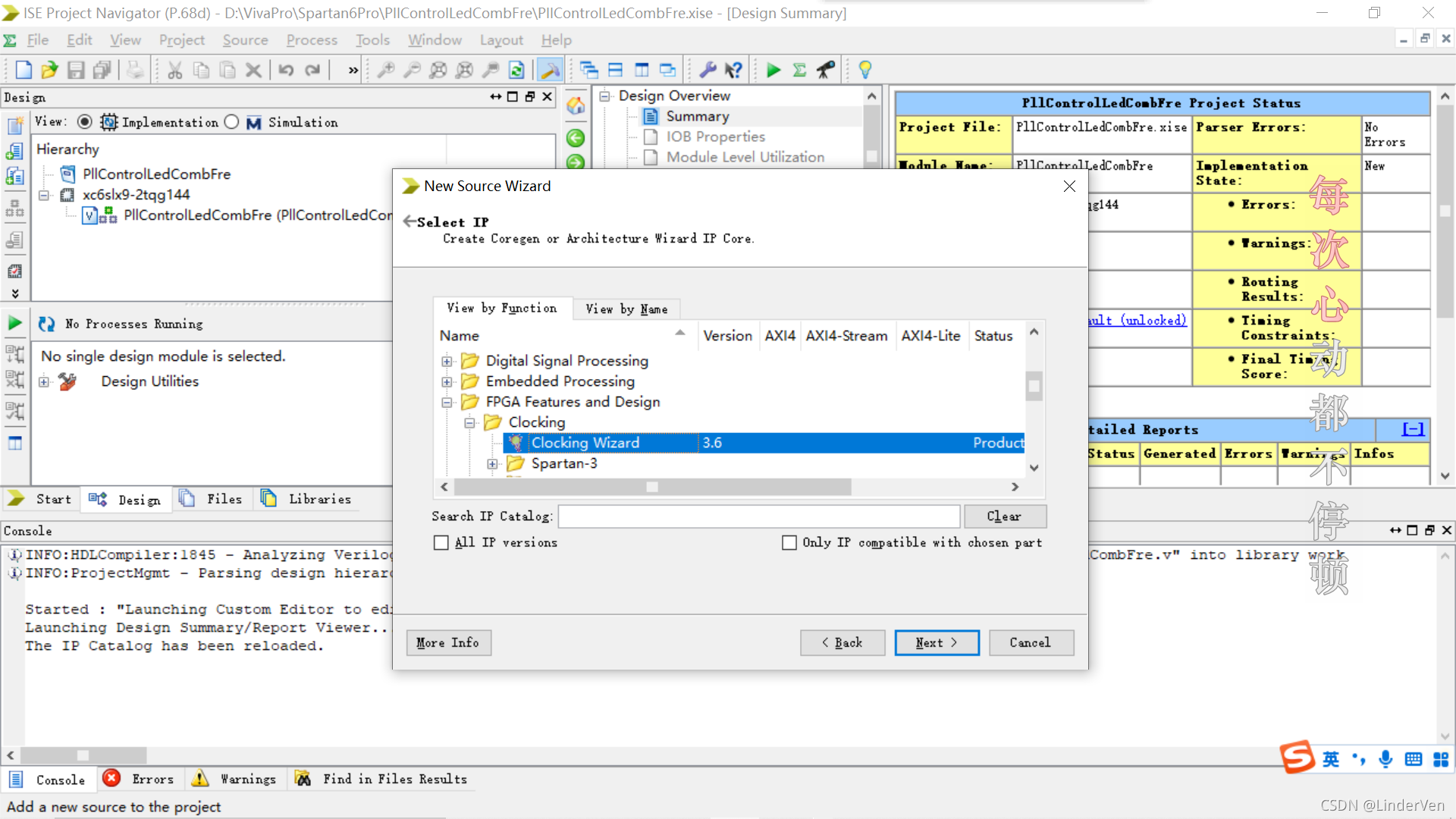

如上图,也是通过鼠标右键有个new,就到这儿了,然后选择IP(core generate啥啥啥的那个文件),路径是ipcore_dir

然后就是选择相关的类型和配置了,按照图片上来就行,有啥重要的我会提一下

然后就是选择相关的类型和配置了,按照图片上来就行,有啥重要的我会提一下

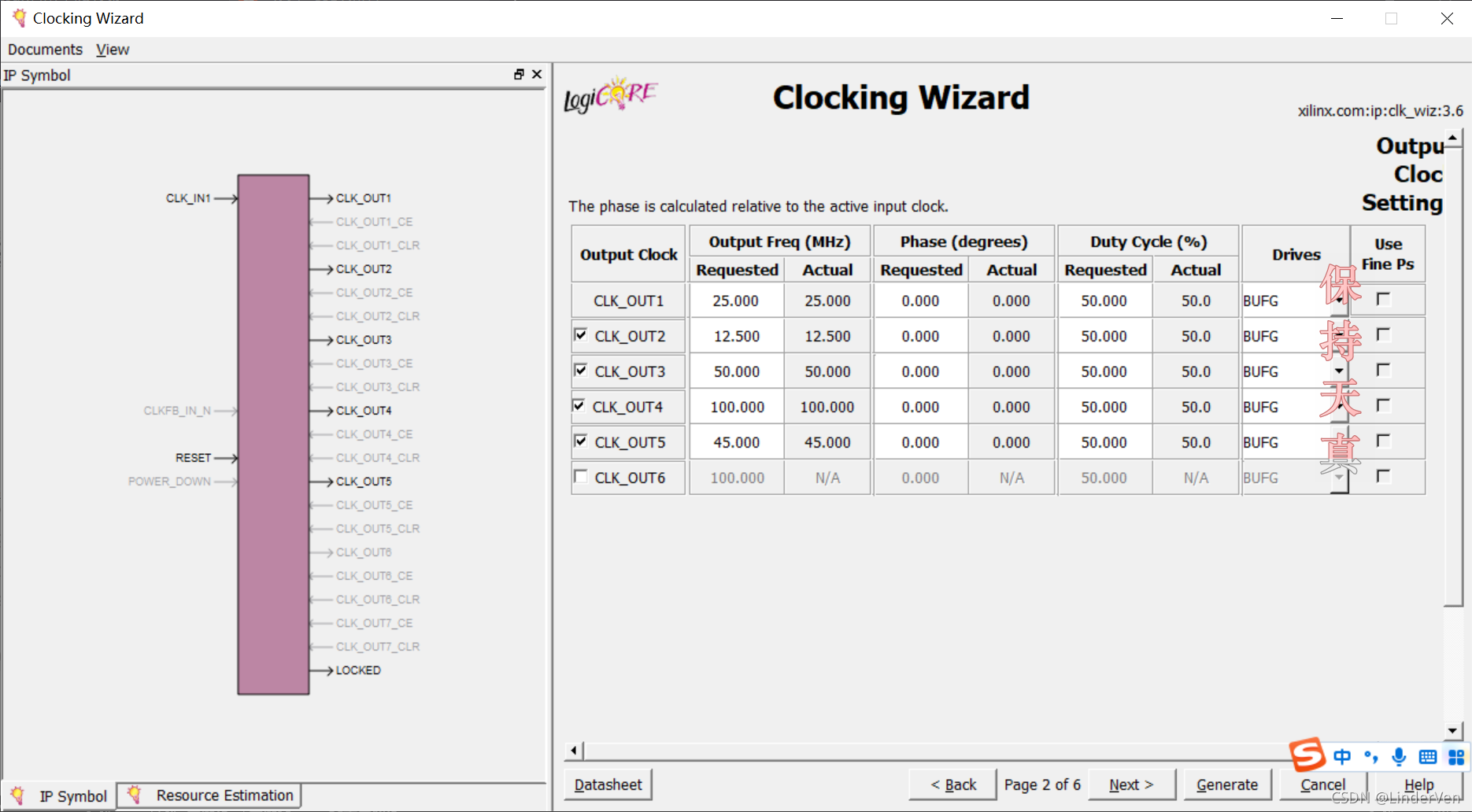

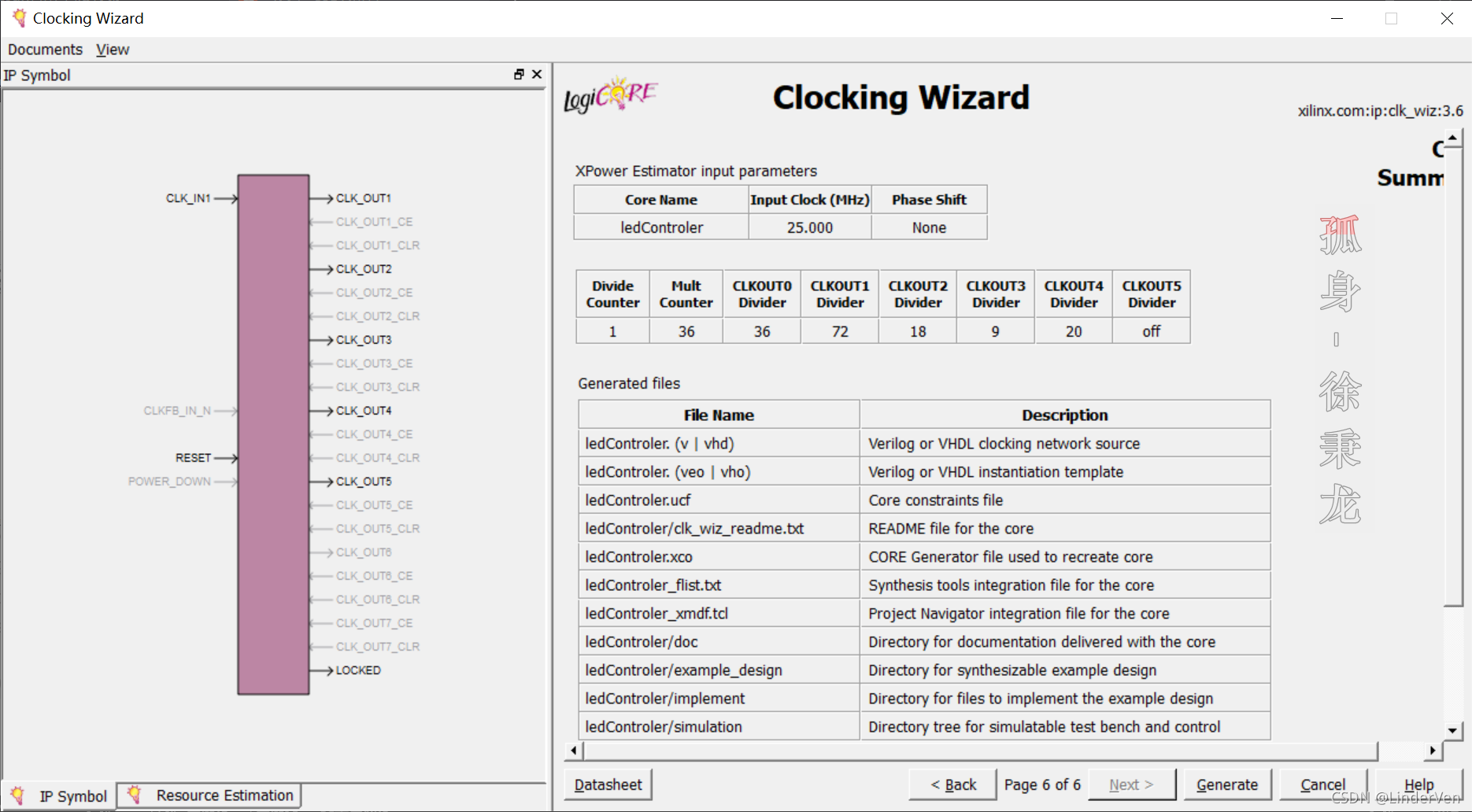

然后会跳到IP配置界面1,设置主频为25.000,初始应该是100.000

然后会跳到IP配置界面1,设置主频为25.000,初始应该是100.000

然后就是根据你需要的频率设置分频或者倍频,我用了5种,因为教程都是25M的倍频或者分频,我弄了个45M,想看看会是啥样

然后就是根据你需要的频率设置分频或者倍频,我用了5种,因为教程都是25M的倍频或者分频,我弄了个45M,想看看会是啥样

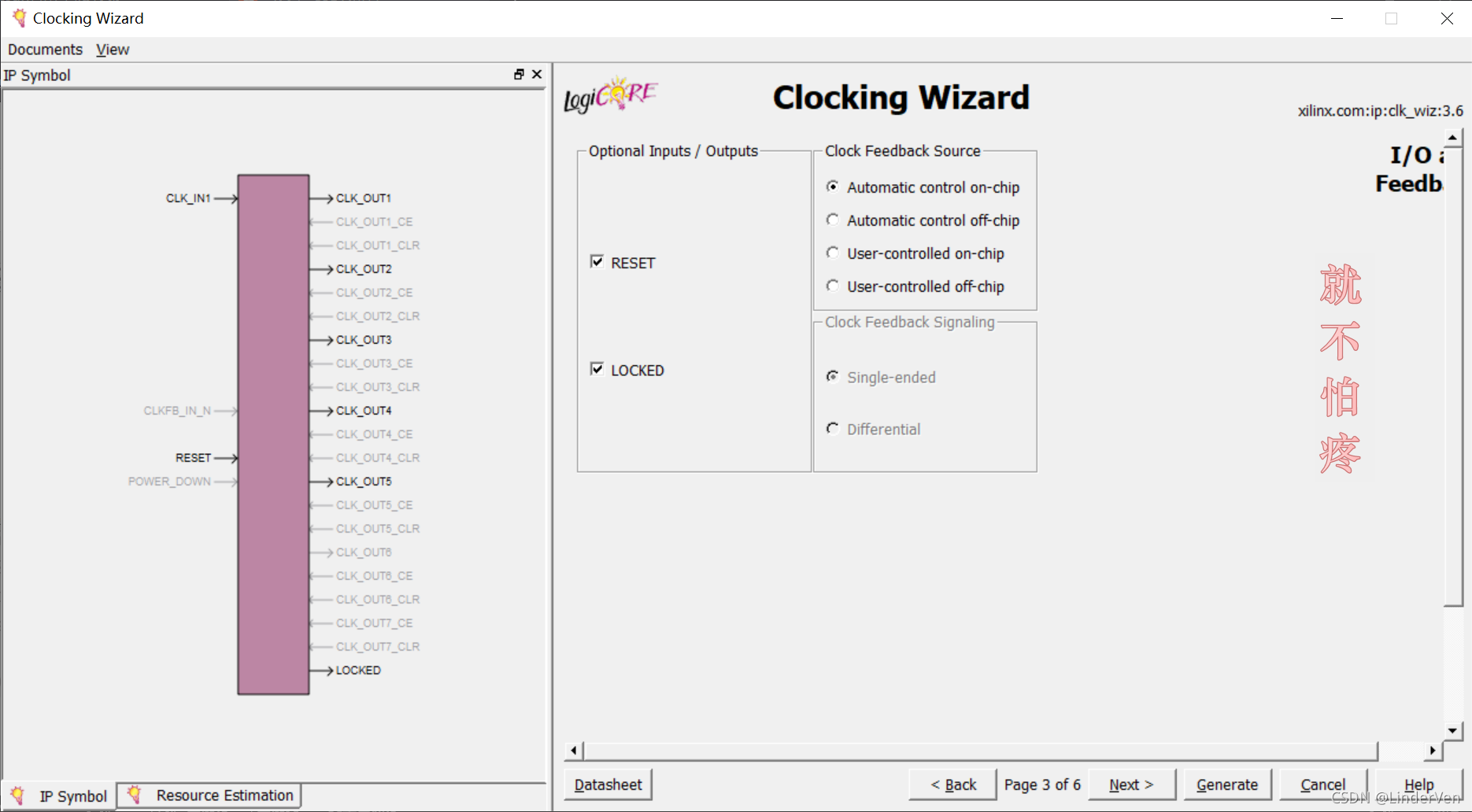

这,,,也是个设置界面

这,,,也是个设置界面

这个也是,到这儿就设置完了,点击generate

这个也是,到这儿就设置完了,点击generate

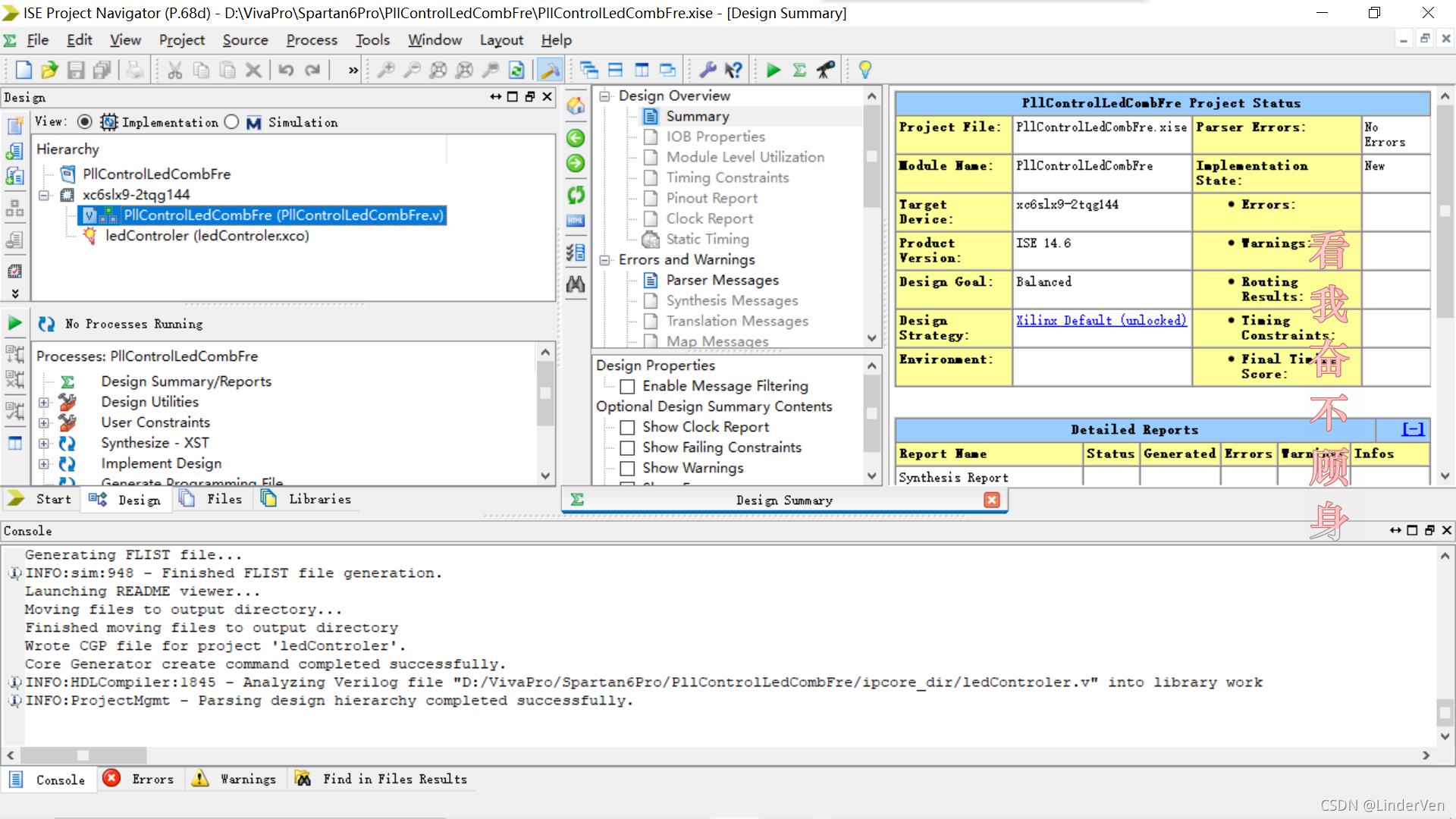

你看,出来个红色的白炽灯图标

你看,出来个红色的白炽灯图标

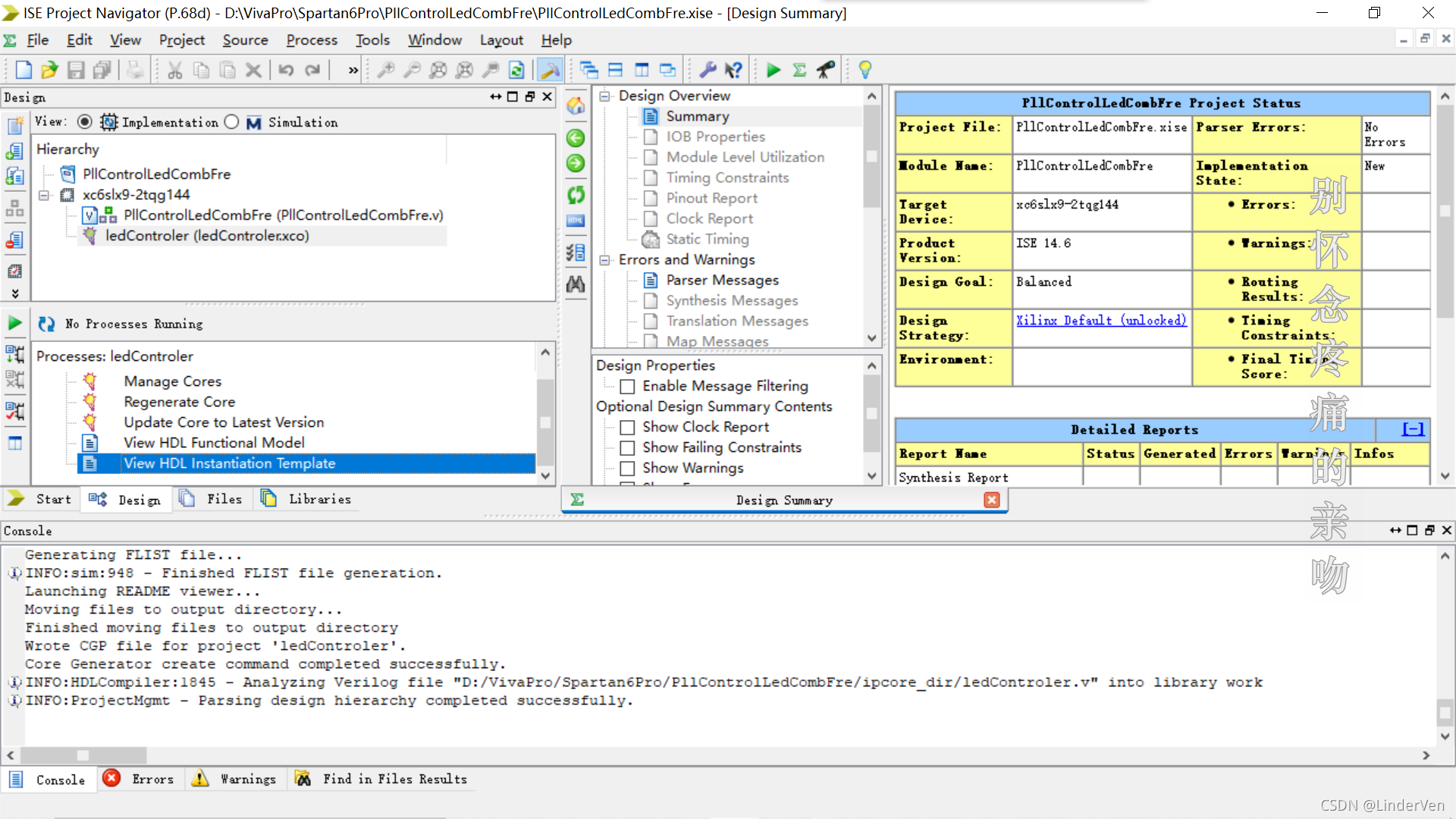

点击红色的白炽灯,在下一栏proccesses ,那一栏展开,找到view HDL instantiation template,双击打开

点击红色的白炽灯,在下一栏proccesses ,那一栏展开,找到view HDL instantiation template,双击打开

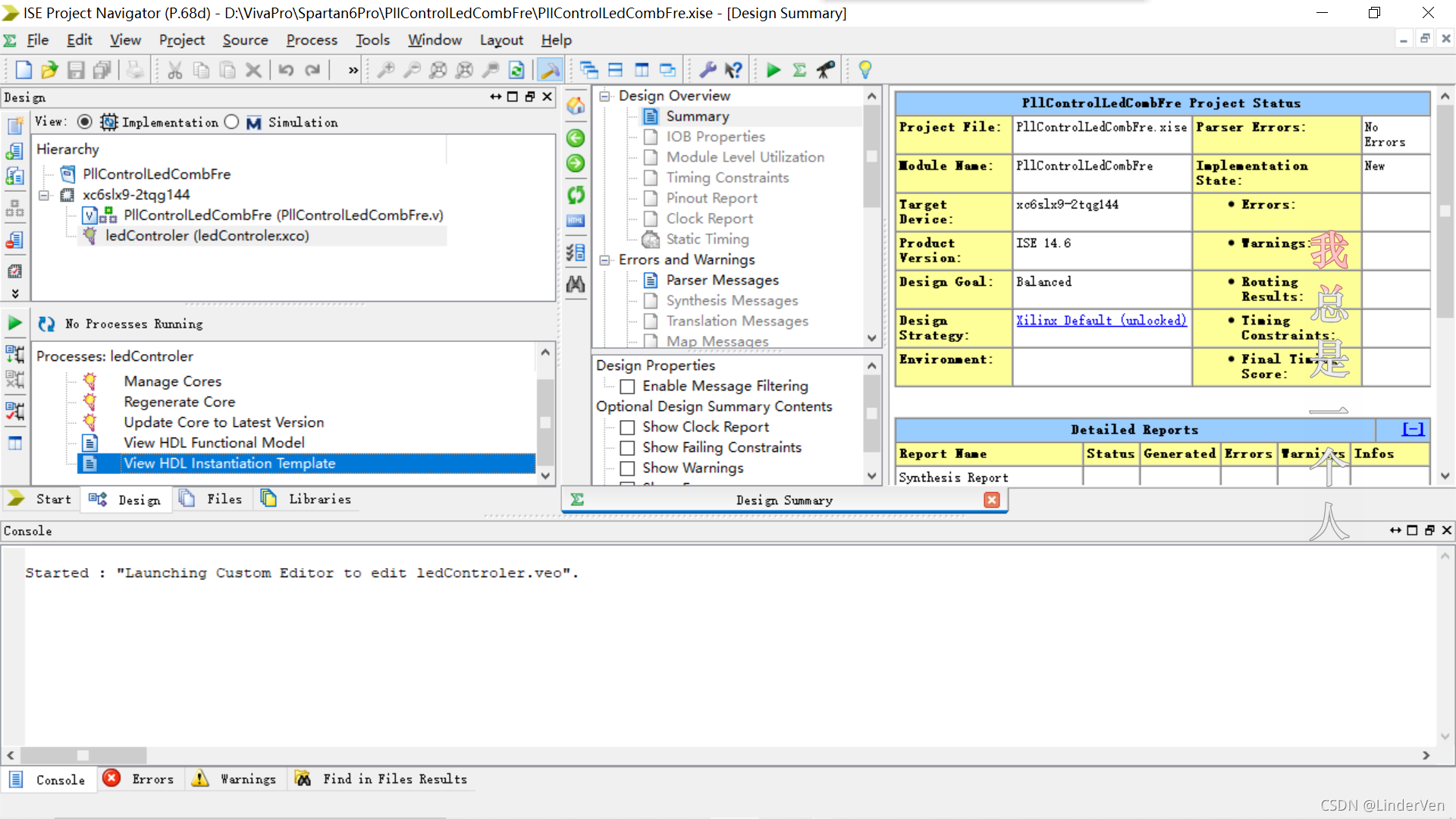

对,双击(是不是截重了,,,)

对,双击(是不是截重了,,,)

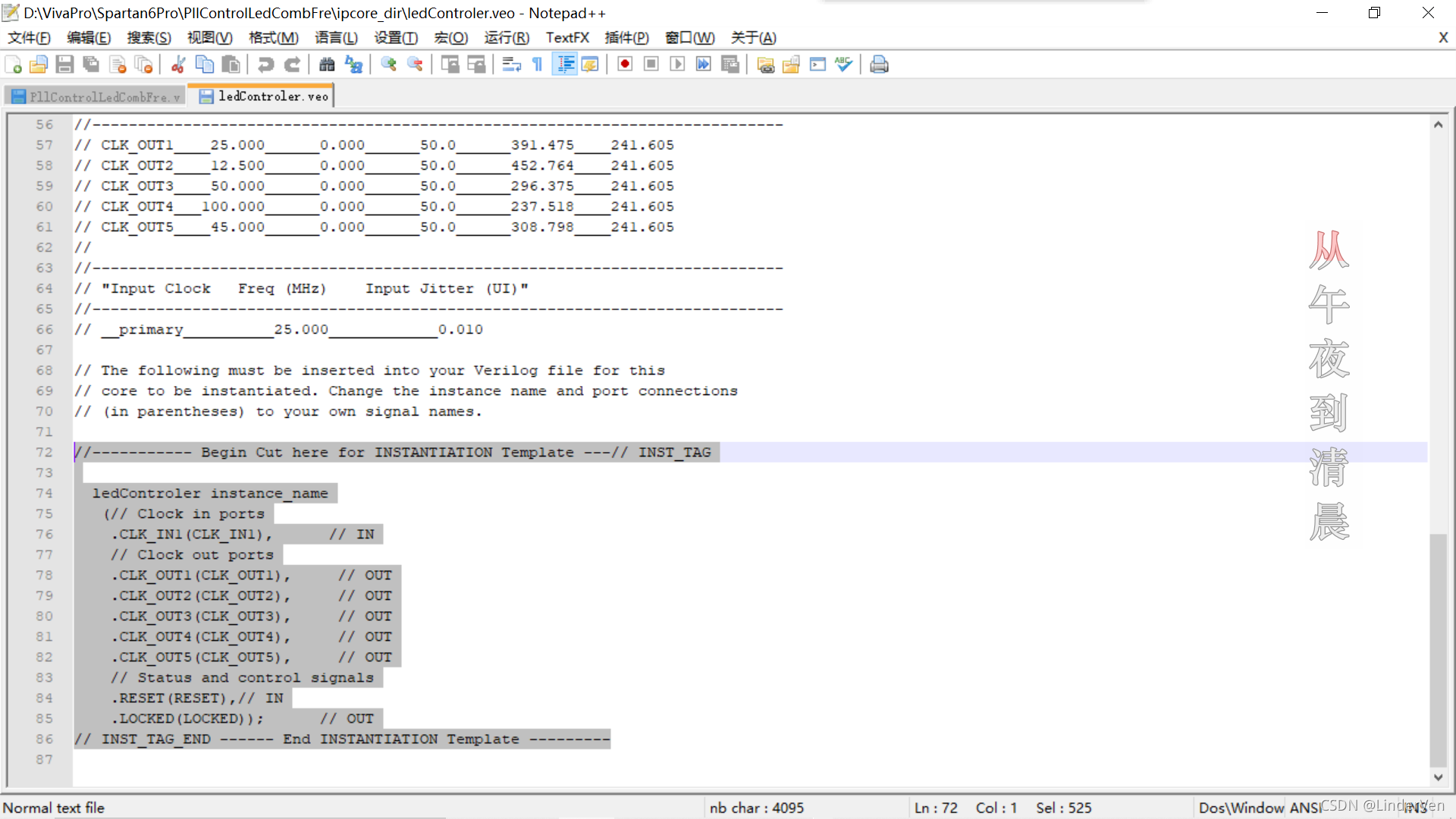

这就是IP核文件打开后的样子,将黑底的代码复制

这就是IP核文件打开后的样子,将黑底的代码复制

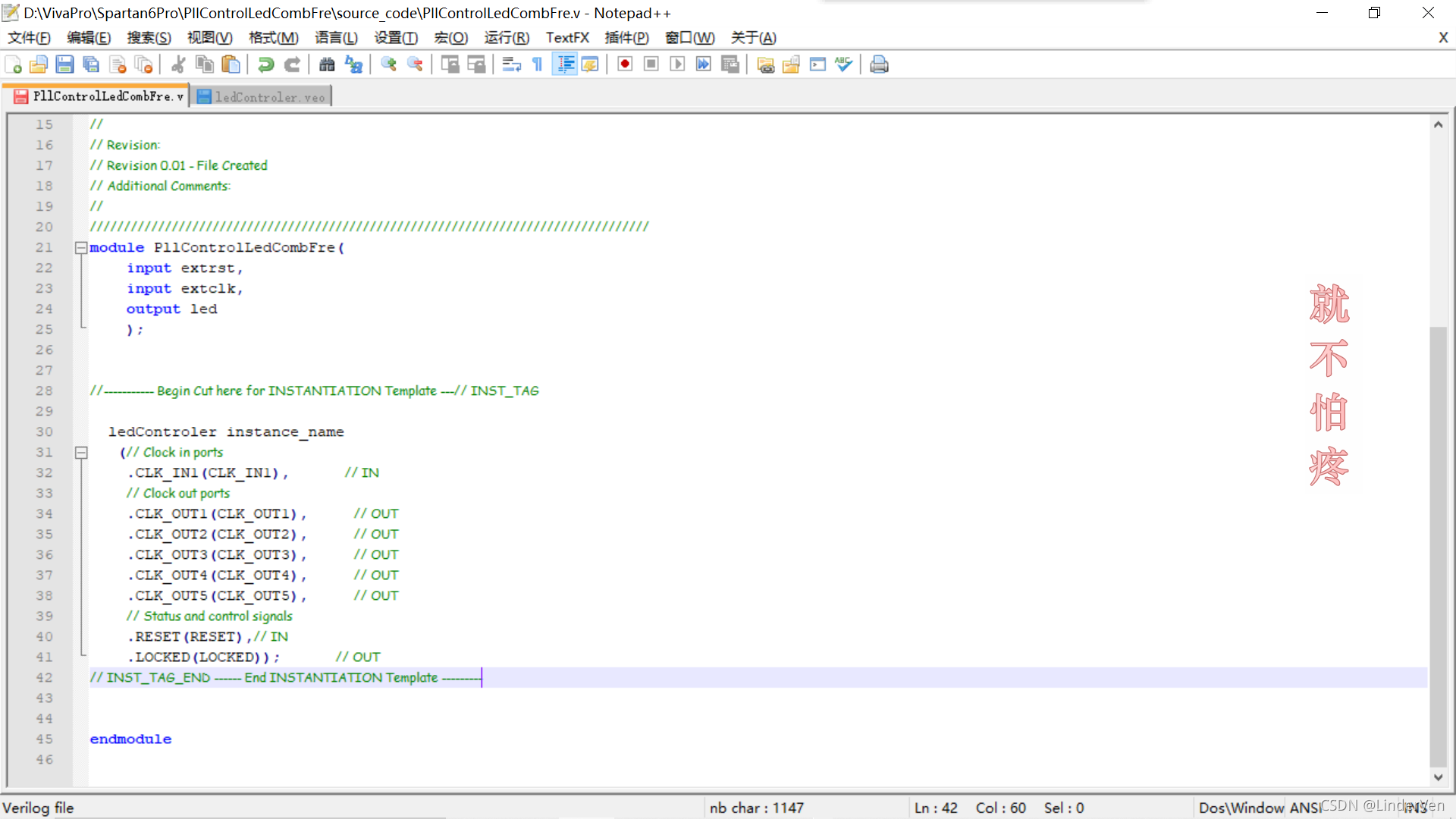

粘到刚刚系统给咱的初始化文件中,像上图那样

粘到刚刚系统给咱的初始化文件中,像上图那样

(这儿有错误,是.CLK_IN1()里面填的和.LOCKED()里面填的,可以对照一下代码)

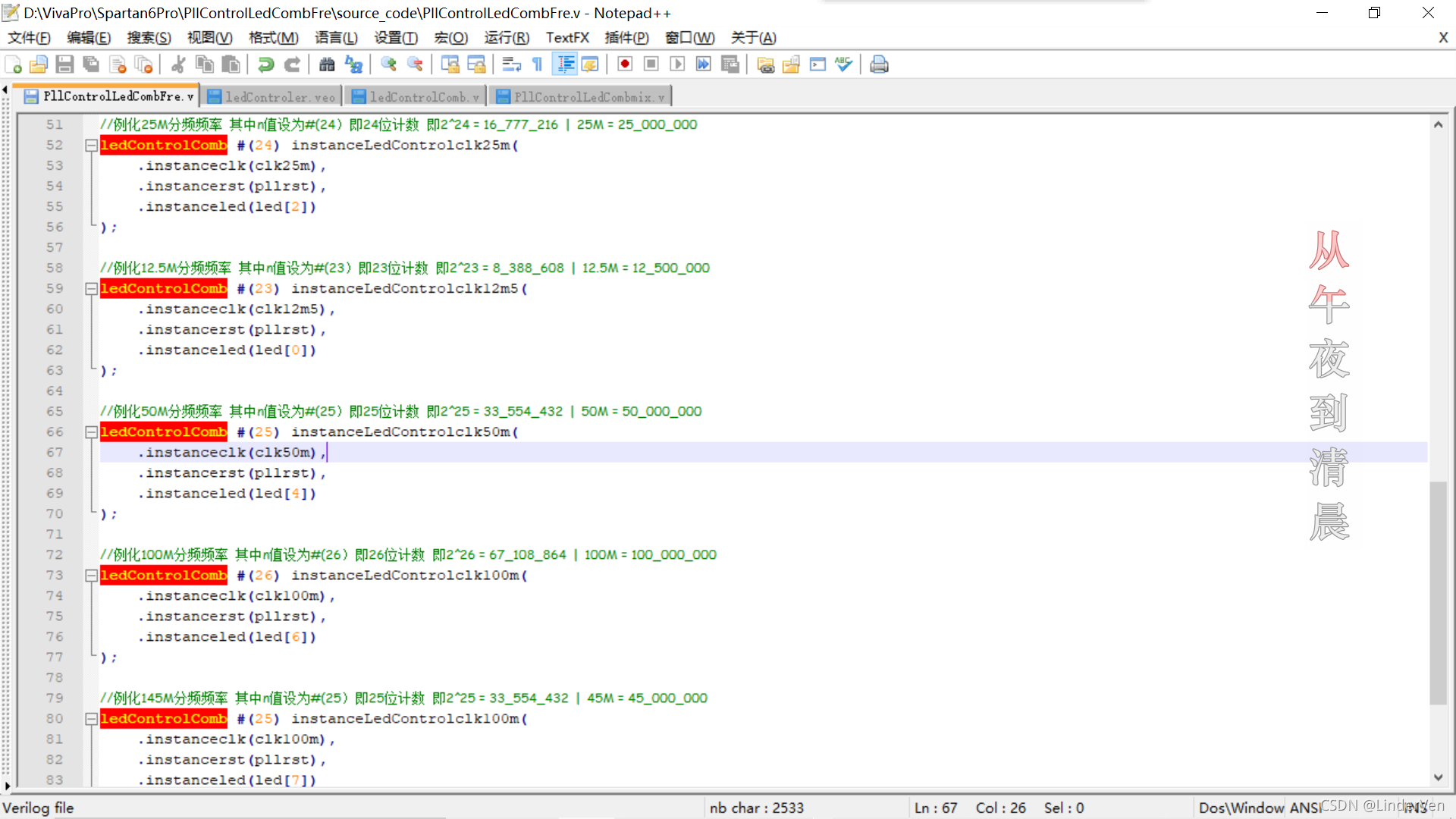

然后在主例化程序中例化,这儿也有问题,就是函数名称,因为是粘的上个文件

然后在主例化程序中例化,这儿也有问题,就是函数名称,因为是粘的上个文件

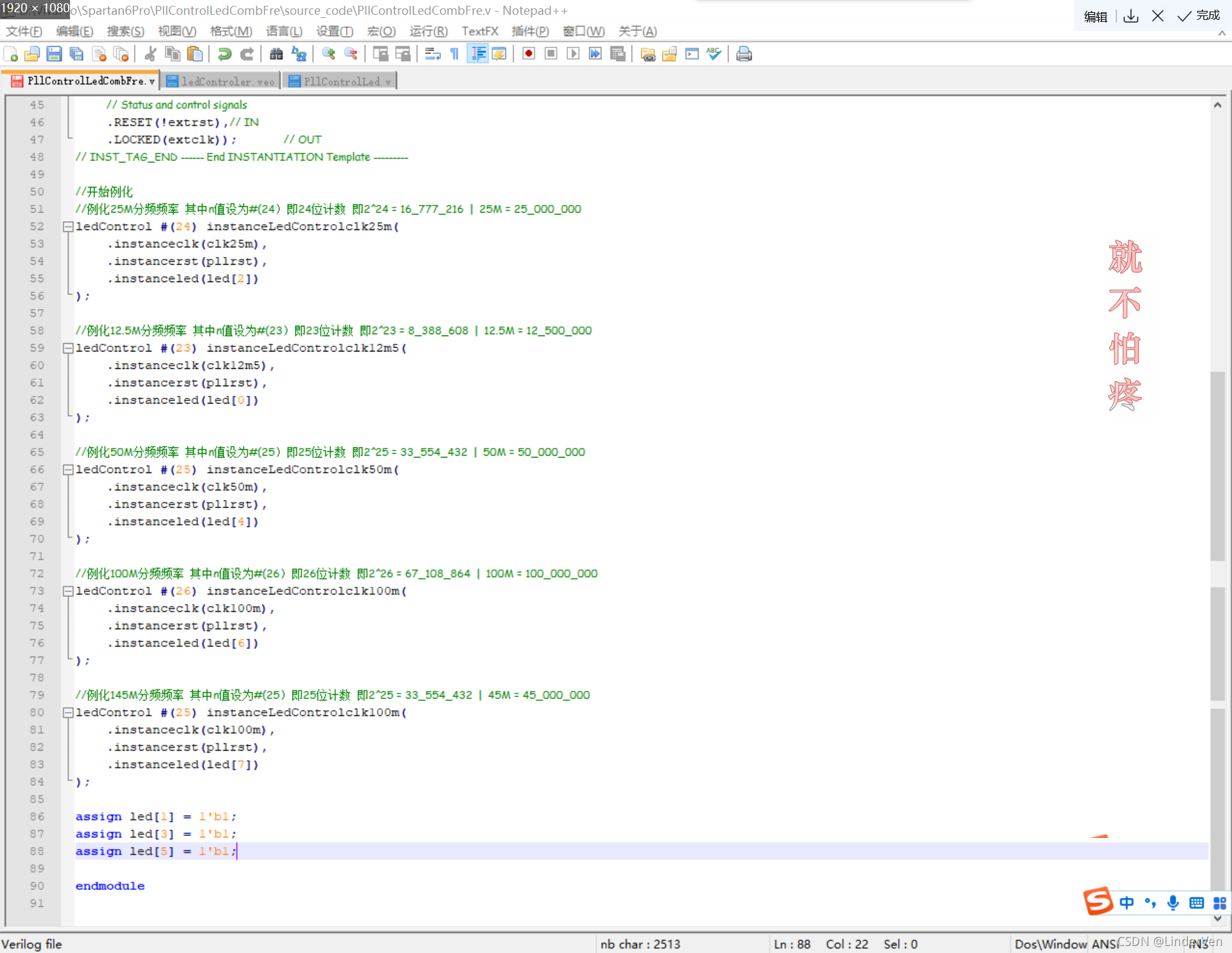

写完以后是这个样子了

写完以后是这个样子了

创建分例化文件

创建分例化文件

一样的操作,注意改名

一样的操作,注意改名

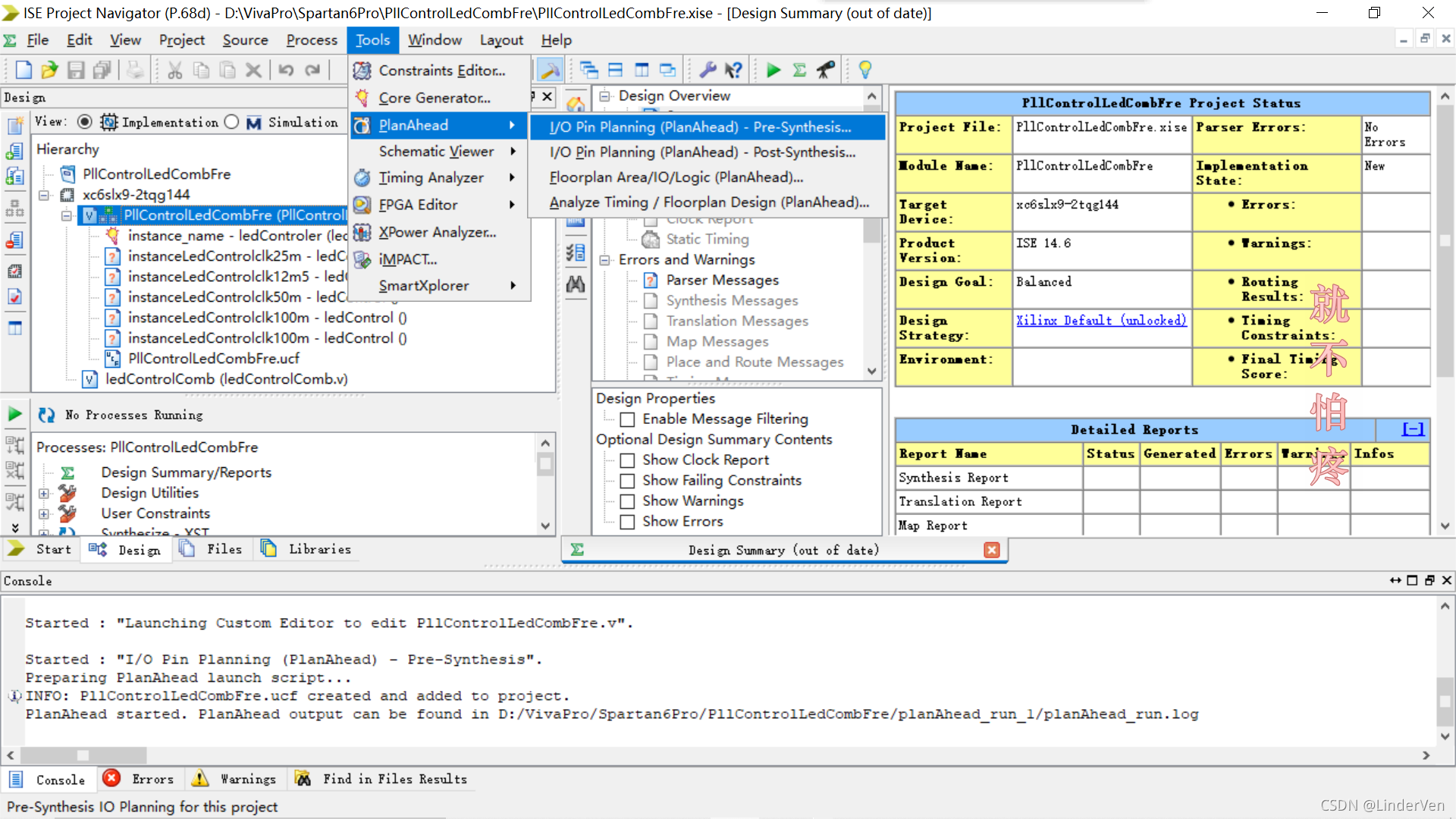

打开引脚配置

打开引脚配置

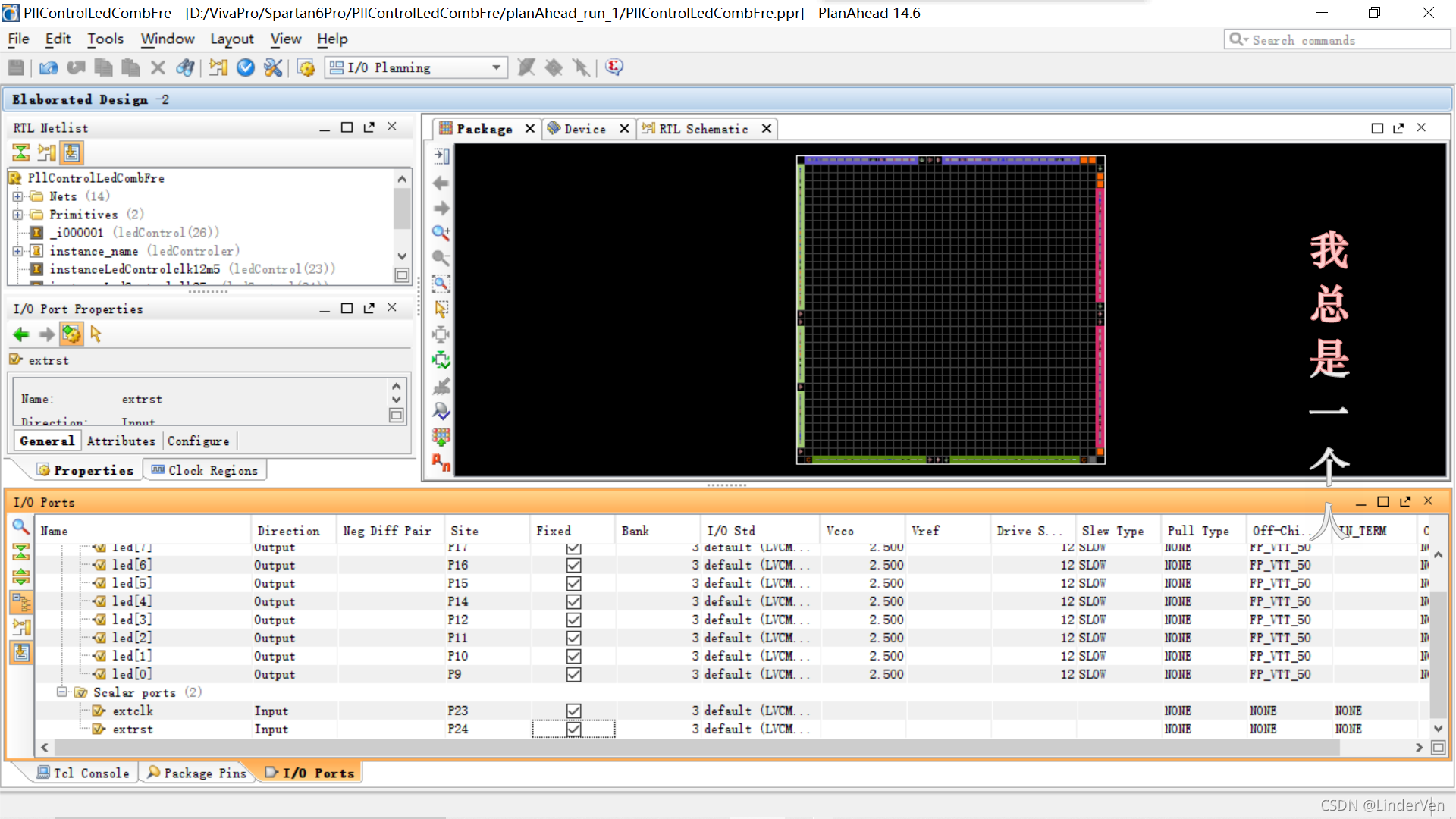

配置引脚

配置引脚

然后就变成这样了

然后就变成这样了

这是上面提到的程序名,要改成你的分例化文件名一样,不然他不知道例化哪一个

这是上面提到的程序名,要改成你的分例化文件名一样,不然他不知道例化哪一个

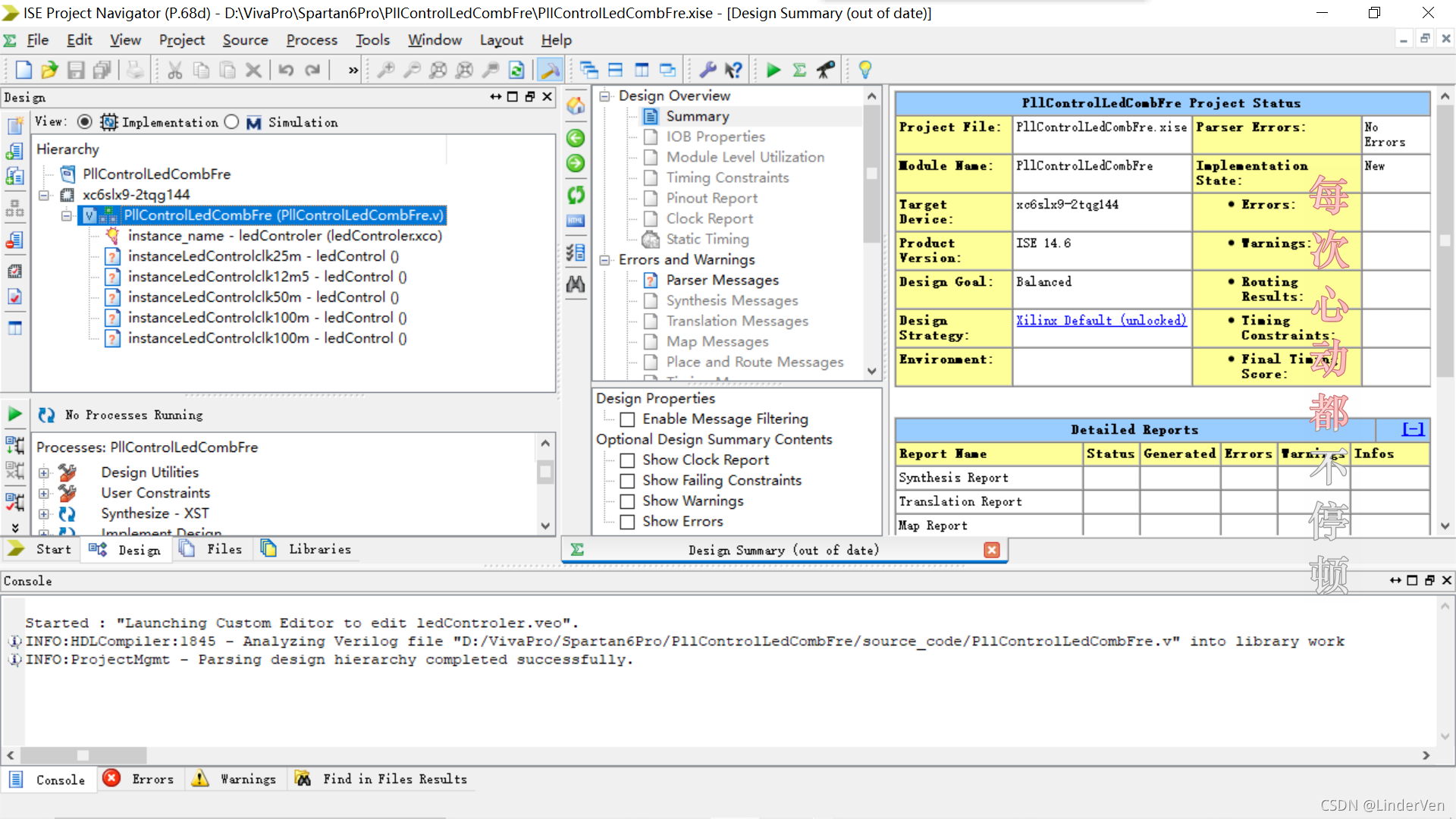

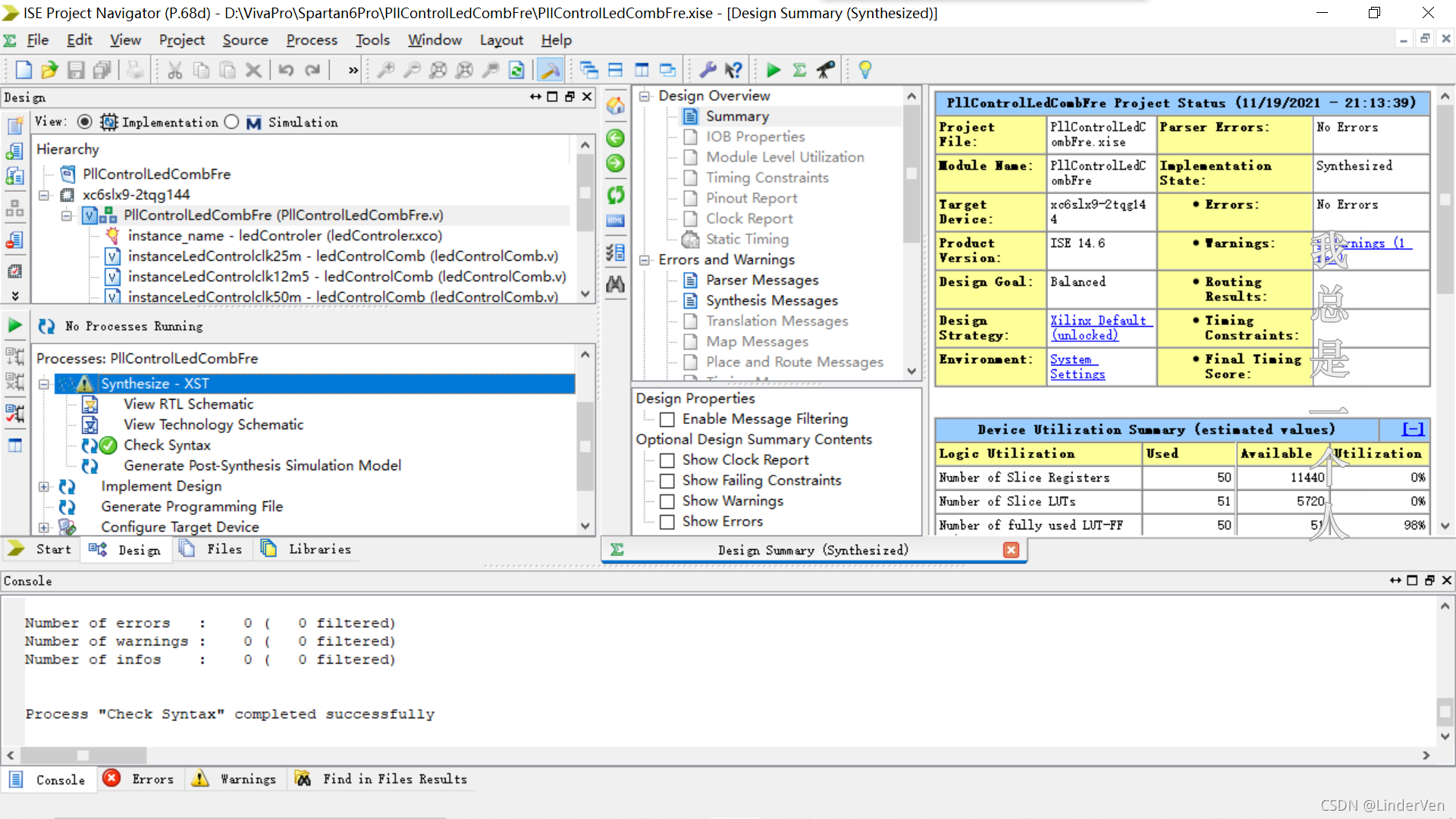

编译

相关的语法检查啥的

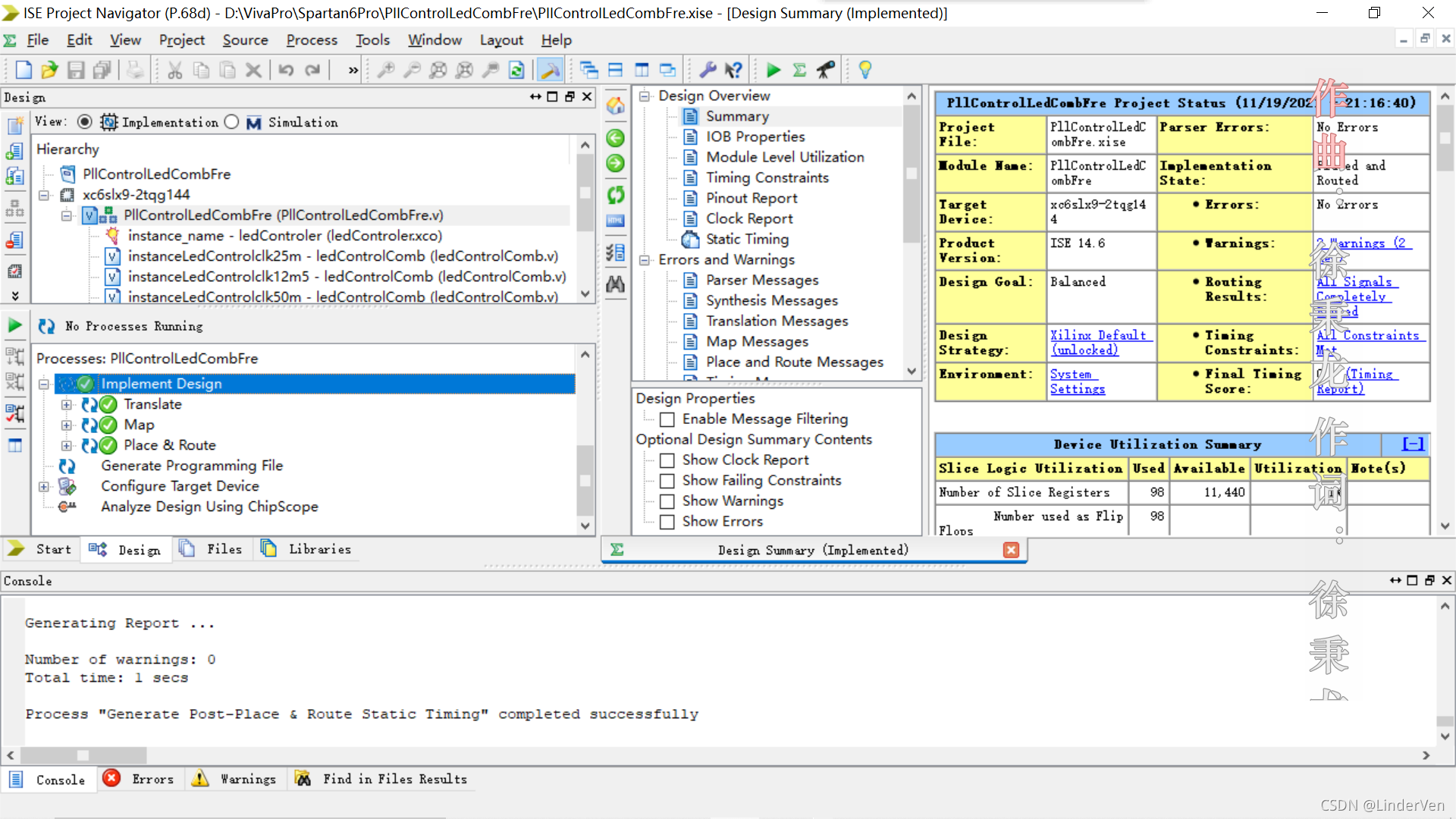

然后是编译

然后是编译

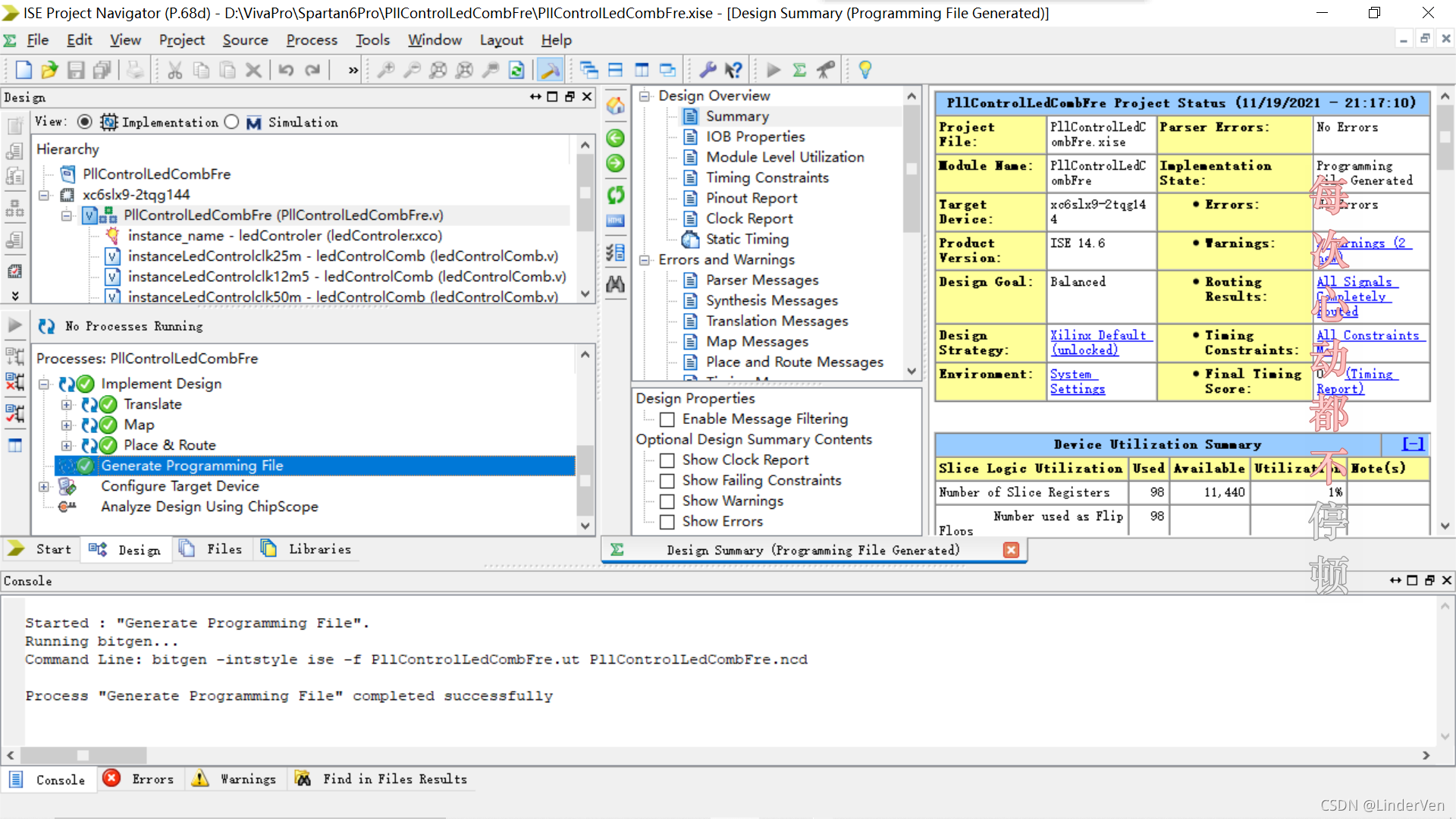

生成比特流文件

生成比特流文件

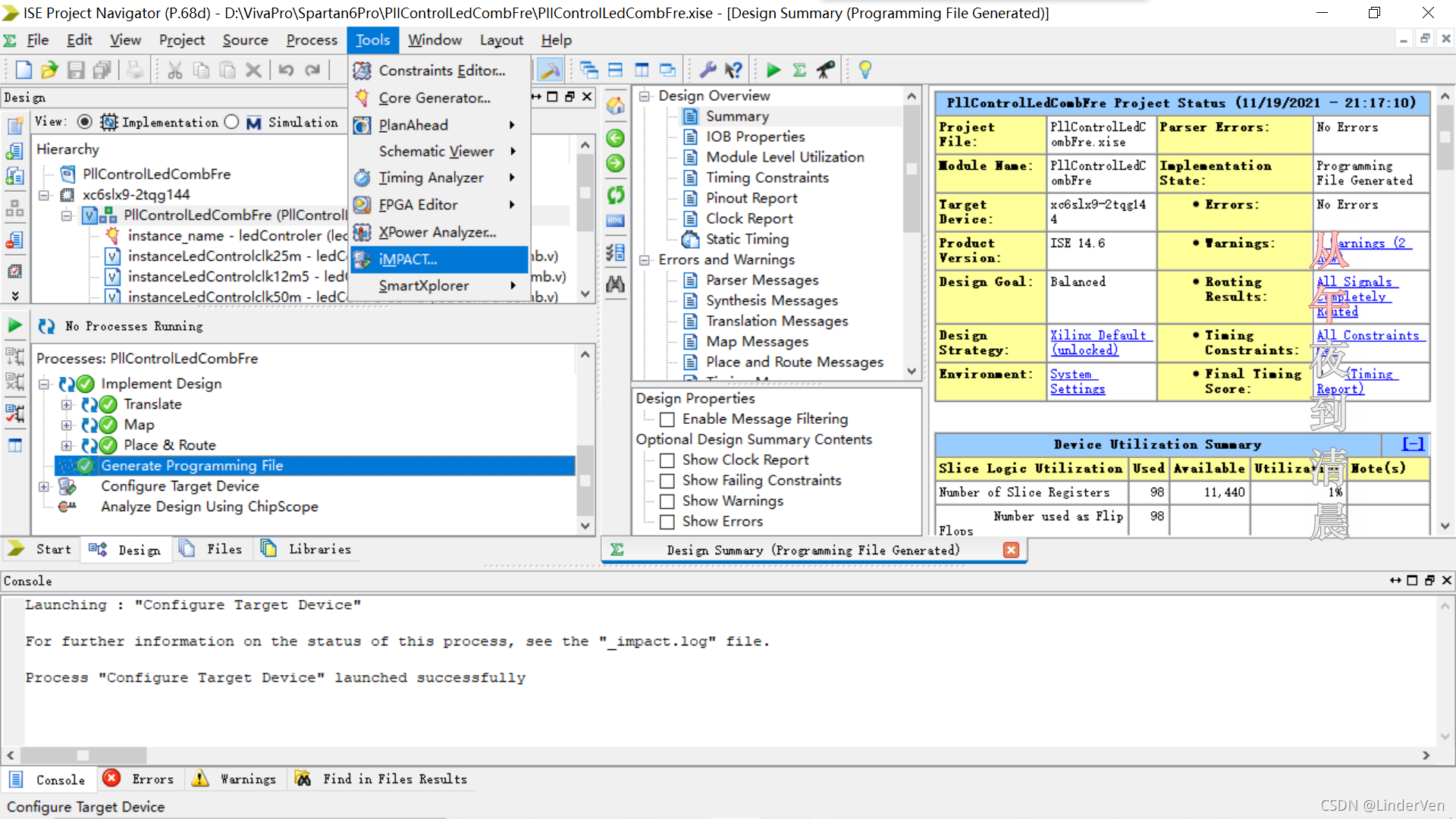

准备下载

准备下载

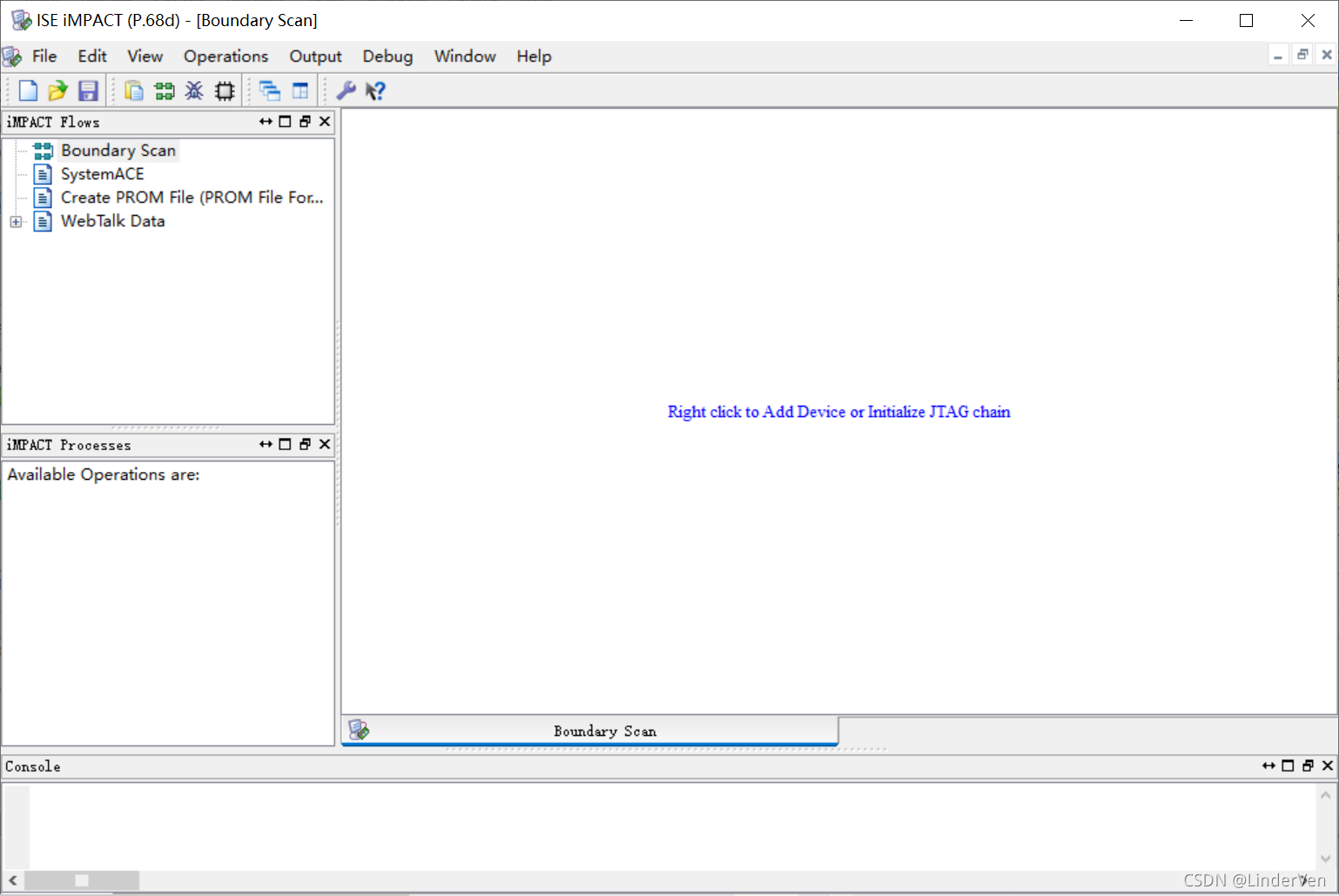

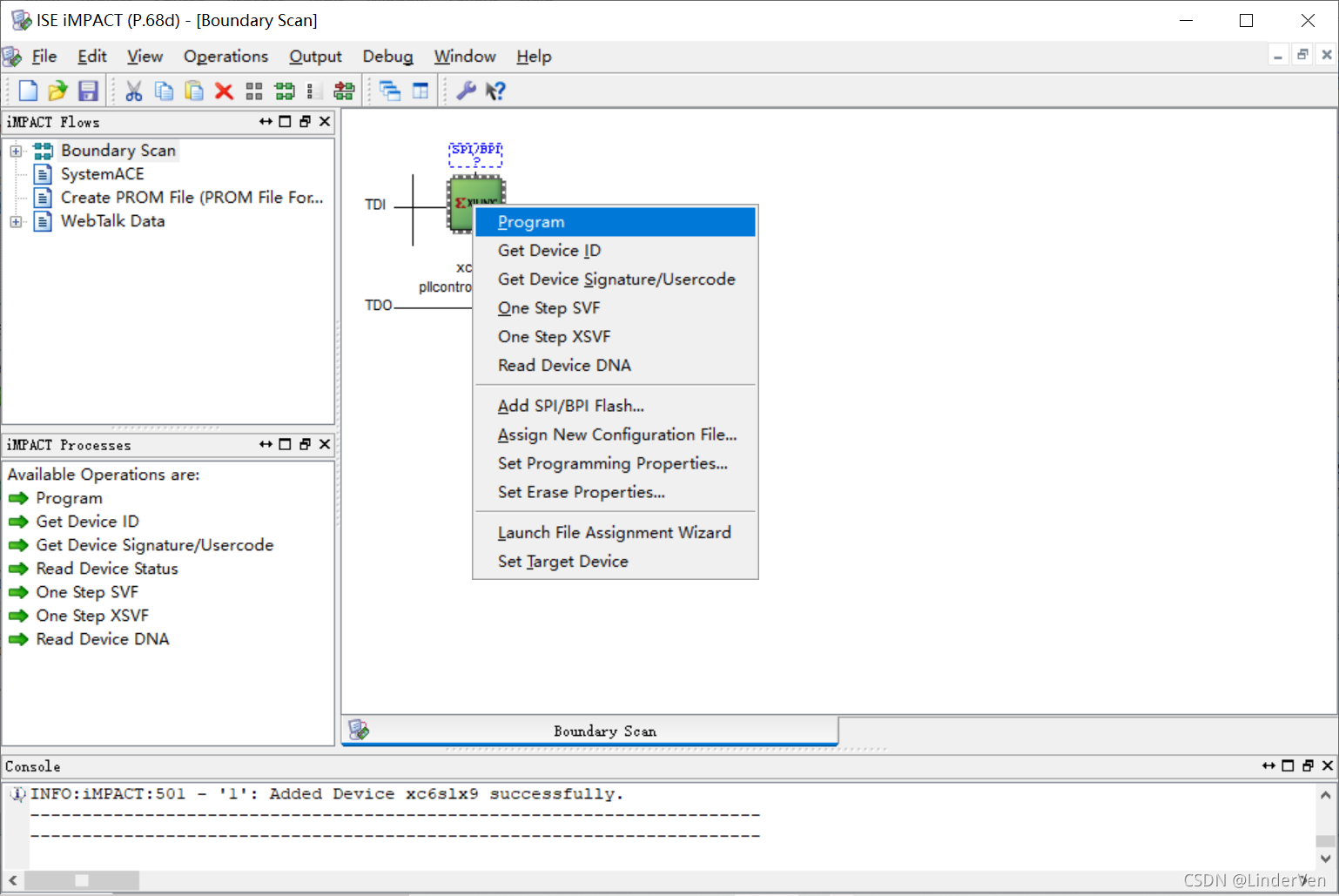

初始化连接(双击boundary scan,会出现白色屏,一开始是灰的,然后左键,右键点击 初始化连接(这句话当然是英语的啦,可惜我不会说))

初始化连接(双击boundary scan,会出现白色屏,一开始是灰的,然后左键,右键点击 初始化连接(这句话当然是英语的啦,可惜我不会说))

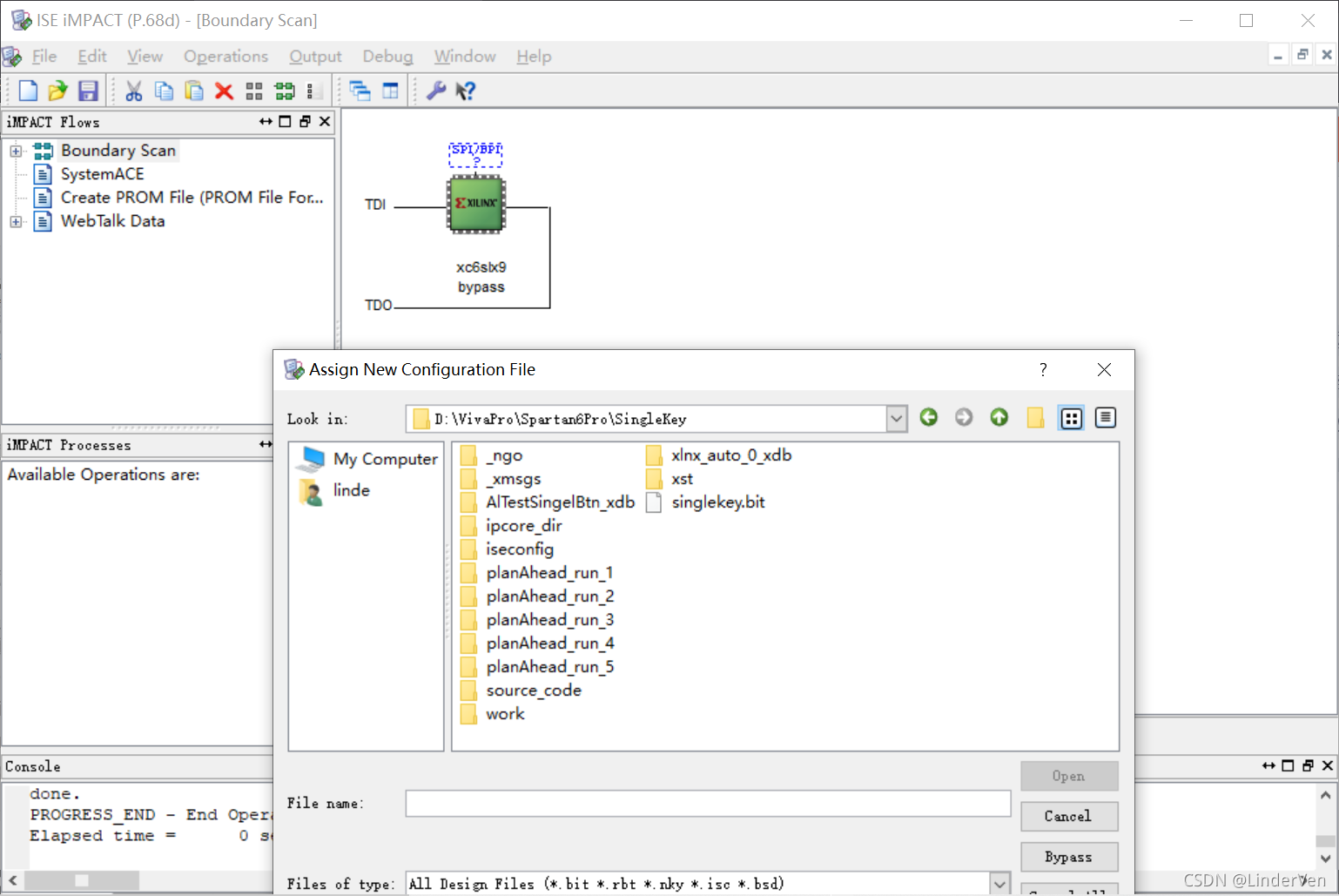

准备下载文件

准备下载文件

下载

下载

结果

不会传视频,拍了几张照片,我感觉能证明这亮灯频率不一样

不会传视频,拍了几张照片,我感觉能证明这亮灯频率不一样

大佬们再见,我要回去睡觉了

本文介绍了一项关于LED显示模式的实验,使用Xilinx Spartan6 FPGA芯片和ISE 14.6软件,验证不同频率下(包括非标准的45MHz)LED的闪烁效果。通过创建IP核并进行分频处理,实现了对多种频率的支持。

本文介绍了一项关于LED显示模式的实验,使用Xilinx Spartan6 FPGA芯片和ISE 14.6软件,验证不同频率下(包括非标准的45MHz)LED的闪烁效果。通过创建IP核并进行分频处理,实现了对多种频率的支持。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?