Questa Sim(逻辑测试)

作者:Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

知乎:https://www.zhihu.com/people/saint-80-61/columns

Questa Sim和ModelsSim是工业界最优秀的语言仿真器,两者都能用于FPGA的功能测试、性能测试、接口测试、时序测试、逻辑测试等测试类型,此节针对逻辑测试进行讨论,相同步骤查看功能测试相关描述。

逻辑测试:

1.选择覆盖范围

全选源码右键选择Properties

在Coverage下选中需要覆盖的内容,包括语句、分支、条件、表达式、状态机覆盖等

对仿真文件进行重新编译

在Simulate下Start simulation的others中选中Enable memory profiling启用内存配置、Enable code coverage启用代码覆盖

选择Design的work中的仿真顶层文件

未执行仿真前分析框中代码行显示X

执行仿真操作后,分析框中部分代码行显示√

分析框中显示X处是激励向量未进入的语句

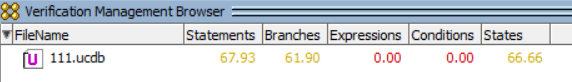

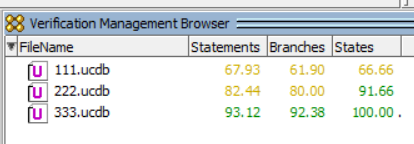

生成当前覆盖文件:在终端输入 add testbrowser 111.ucdb后保存当前覆盖文件:在终端输入fcover save 111.ucdb,在Verification Management Browser 添加ucdb覆盖文件

可以通过对Verification Management Browser 标签栏右键Change Column Visility,过滤显示覆盖项

由于激励代码没有表达式、分支语句,此处激励文件的这两项覆盖率为0

回到分析页面双击跳转至代码行得知语句未100%覆盖是由于仿真时间不够

因此调整仿真时间100000 ns至测试激励语句全覆盖

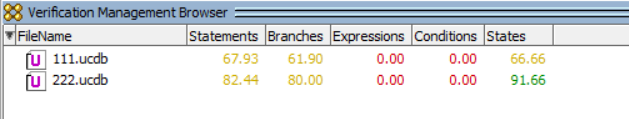

再次生成覆盖文件:在终端输入 add testbrowser 222.ucdb后保存当前覆盖文件:在终端输入fcover save 222.ucdb,在Verification Management Browser 添加ucdb覆盖文件,可以发现覆盖率提升

把源文件所有uut单元进行调试覆盖率

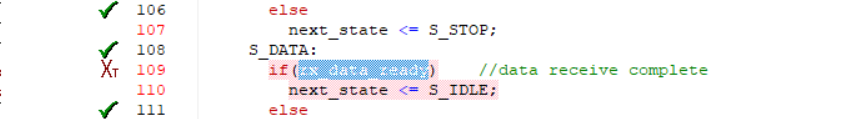

示例:

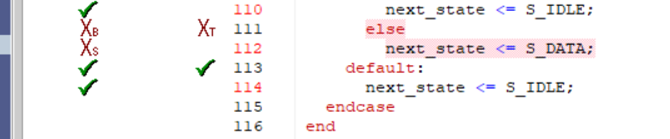

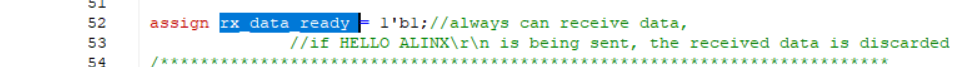

rx_data_ready 恒为1导致111行else分支进不去

再次生成覆盖文件:在终端输入 add testbrowser 333.ucdb后保存当前覆盖文件:在终端输入fcover save 333.ucdb,在Verification Management Browser 添加ucdb覆盖文件,可以发现覆盖率提升

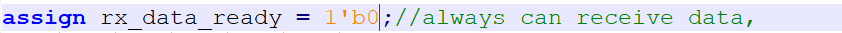

修改rx_data_ready 恒为0

再次生成覆盖文件:在终端输入 add testbrowser 444.ucdb后保存当前覆盖文件:在终端输入fcover save 444.ucdb,在Verification Management Browser 添加ucdb覆盖文件,可以发现覆盖率提升

在Verification Management Browser全选ucdb文件后merge执行覆盖率融合操作

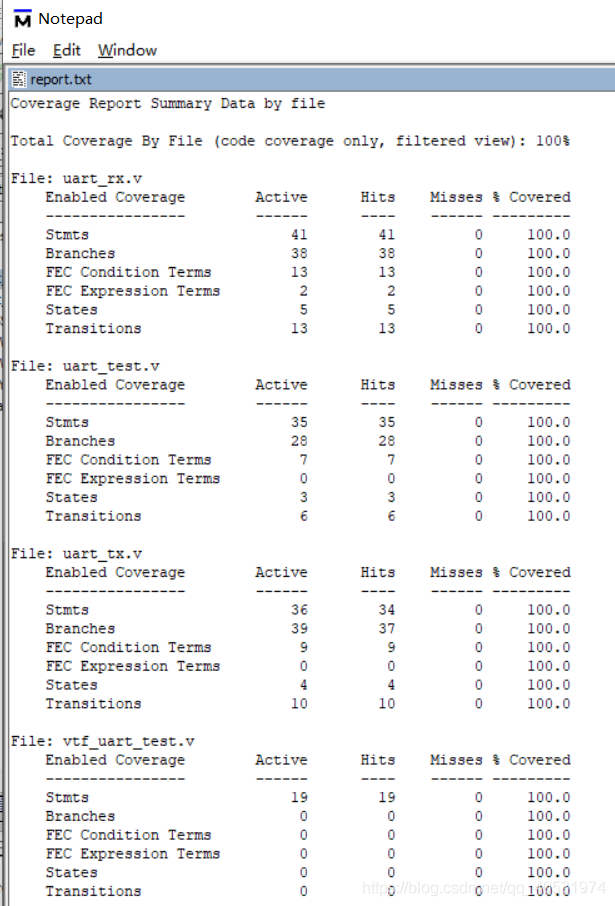

在Tools工具栏下拉选择Coverage Report 后输出Text覆盖率文本

选择各单元输出,若输出总的覆盖率应选择Total Coverage

查看覆盖率文本可知uart_rx、uart_test、uart_tx单元覆盖率尚未达到100%

因此我们需要依次对显示X的路径进行语句、分支、条件、表达式覆盖在分析界面可以选择筛查语句、分支、条件、表达式不符合项进行调试

对每次调试结果依次生成ucdb文件,直至merge后覆盖项达100%后输出覆盖率文本

2200

2200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?