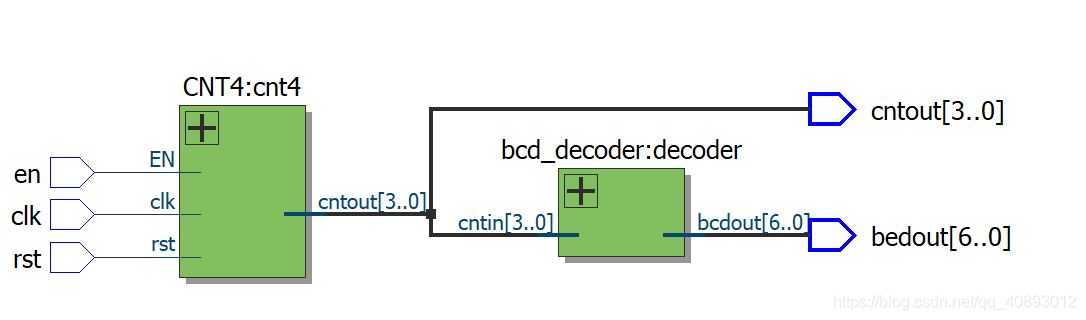

1原理电路

2计数器模块代码

module CNT4(clk,rst,EN,cntout);//4位计数器

input clk,rst,EN; //低电平使能 高电平复位

output [3:0]cntout; //高电平同步复位

reg [3:0]cntout;

always @(posedge clk)

begin

if(EN==0)

begin

if(rst==1)

begin

cntout=0;

end

else

begin

if(cntout>=15) cntout = 0;

else cntout = cntout+1;

end

end

else cntout=cntout;

end

endmodule3BCD七段译码器模块

数码管显示和BCD段码之间的关系

bcdout 的7位从左到右分别是a,b,c,d,e,f,g。

module bcd_decoder(cntin,bcdout);

input[3:0] cntin;

output reg[6:0] bcdout;

always@(cntin)

begin

case(cntin)

4'b0000:bcdout = 7'b1111110;

4'b0001:bcdout = 7'b0110000;

4'b0010:bcdout = 7'b1101101;

4'b0011:bcdout = 7'b1111001;

4'b0100:bcdout = 7'b0110011;

4'b0101:bcdout = 7'b1011011;

4'b0110:bcdout = 7'b1011111;

4'b0111:bcdout = 7'b1110000;

4'b1000:bcdout = 7'b1111111;

4'b1001:bcdout = 7'b1111001;

4'b1010:bcdout = 7'b1110111;

4'b1011:bcdout = 7'b0001111;

4'b1100:bcdout = 7'b1001110;

4'b1101:bcdout = 7'b0111101;

4'b1110:bcdout = 7'b1001111;

4'b1111:bcdout = 7'b1000111;

endcase

end

endmodule4顶层模块代码

module LED_NUM(clk,rst,en,cntout,bedout); //顶层模块

input clk,rst,en;

output [3:0]cntout;

output [6:0]bedout;

CNT4 cnt4(.clk(clk),.rst(rst),.EN(en),.cntout(cntout));

bcd_decoder decoder(.cntin(cntout),.bcdout(bedout));

endmodule5测试脚本

`timescale 1 ns/ 1 ps

module LED_NUM_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg en;

reg rst;

// wires

wire [3:0] cntout;

wire [6:0] bedout;

// assign statements (if any)

LED_NUM i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.cntout(cntout),

.en(en),

.rst(rst),

.bedout(bedout)

);

initial

begin

// code that executes only once

// insert code here --> begin

rst = 1;

clk = 0;

en = 0;

#300;

en = 0;

rst = 0;

#1000;

rst = 1;

#100;

rst = 0;

#500

en = 1;

#500;

en = 0;

#2000

$stop;

// --> end

$display("Running testbench");

end

always #40 clk = ~clk;

// optional sensitivity list

// @(event1 or event2 or .... eventn)

//begin

// code executes for every event on sensitivity list

// insert code here --> begin

//@eachvec;

// --> end

//end

endmodule

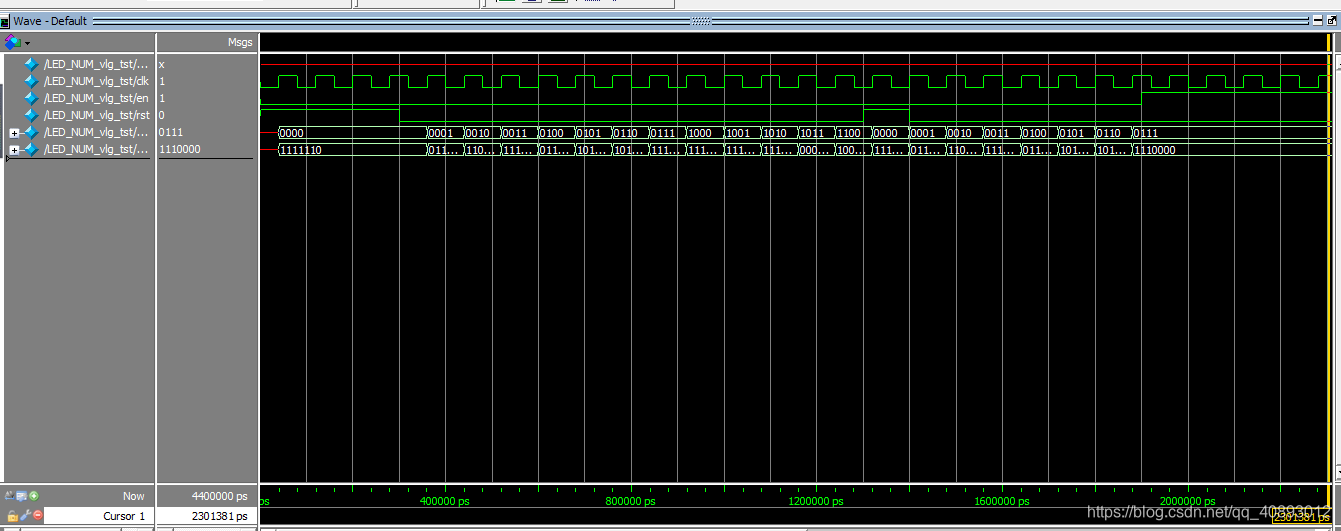

5仿真结果

本文详细介绍了使用Verilog硬件描述语言实现4位计数器和BCD七段译码器的方法。包括计数器模块代码、BCD译码器模块以及顶层模块的整合,最后通过测试脚本验证了设计的正确性。

本文详细介绍了使用Verilog硬件描述语言实现4位计数器和BCD七段译码器的方法。包括计数器模块代码、BCD译码器模块以及顶层模块的整合,最后通过测试脚本验证了设计的正确性。

2604

2604

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?