MIPI-DSI整理的资料

资料连接

接触MIPI-DSI已经接近三年的时间了,整理了下常用的基本概念,跟大家分享一下,有问题也欢迎大佬们批评指正。

先简单介绍一下MIPI-DSI

MIPI协议实际上是一系列接口的协议,包含液晶、摄像头等等。液晶中所用的MIPI接口,其专业名称叫DSI,全称Display Serial Interface。DSI支持两种基本操作模式, command mode和video mode。 Video mode无论当前显示是否有数据更新,DSI host端一直送数据给panel显示。Command mode只有当数据画面有变化时,DSI host端才送数据给panel显示。

1、通用描述

主机与显示模块之间的通信可分为两个不同的层次:

-接口级别:低级别通信

-包级:高级通信

2、接口级通信

2.1 概述

显示模块采用数据通道和时钟通道差分对进行DSI,时钟通道和数据通道均可驱动为低速(LP)或高速(HS)模式。数据通道1/2/3只支持高速模式。.

1.2.2 DSI-CLK 通道

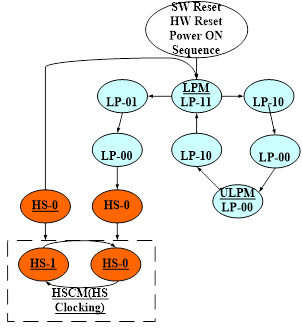

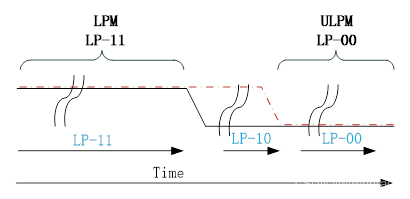

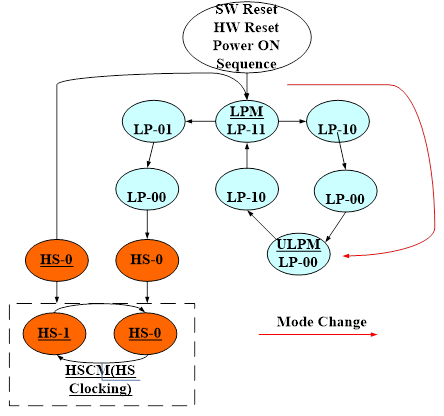

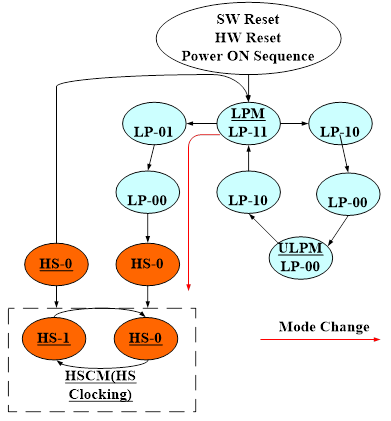

DSI-CLK+/-通道可以驱动到三种不同的电源模式:低功耗模式(LPM LP-11),超低功耗模式(ULPM)或高速时钟模式(HSCM)。

时钟通道在进入或离开低功率模式(LPM )或超低功率模式(ULPM) 模式时处于单端模式(LP = Low Power)。

当进入或退出高速时钟模式(HSCM) 时,时钟通道处于单端模式(LP = Low Power)。

这些进出协议都是在单端模式下使用时钟通道来产生进出序列。

不同时钟通道功率模式的主要流程图如下所示。

注:

- 当lane pair处于高速(HS)模式时,lane pair的低功率接收器(LP-Rx)正在检查LP-00状态码

- 如果lane pair的低功率接收器 (LP-Rx)识别出LP-11状态码,lane pair将返回到Control Mode的LP-11状态码。

1.2.2.1 超低速模式 (ULPM)

当DSI-CLK通道开始在HS-0和HS-1状态码之间工作时,DSI-CLK+/-通道可以被驱动到高速时钟模式(HSCM)。

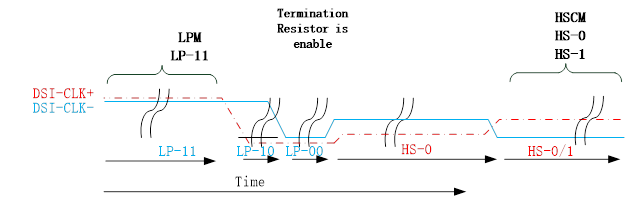

唯一的进入可能性是从低速模式(LPM, LP-11状态代码)=>LP-01 =>LP-00 =>HS-0 =>HS-0/1 (HSCM)。这个序列如下图所示。

1.2.2.2 高速时钟模式 (HSCM)

当DSI-CLK通道开始在HS-0和HS-1状态码之间工作时,DSI-CLK+/-通道可以被驱动到高速时钟模式(HSCM)。

唯一的进入可能性是从低功耗模式(LPM, LP-11状态代码)=>LP-01 =>LP-00 =>HS-0 =>HS-0/1 (HSCM)。这个序列如下图所示。

在通过DSI-Dn+/- lane发送高速数据之前,启动DSI-CLK+/-高速时钟。停止高速数据发送后,高速时钟继续计时

高速时钟的突发包括:

—偶数的转换

—启动状态为HS-0

—结束状态为HS-0

3、 DSI 数据通道

3.1 概述

DSI-Dn+/-数据通道可以在不同的模式下被驱动:

—Escape模式(只支持DSI_D0数据通道对)

—高速数据传输(支持所有数据通道对)

—总行周转请求(仅支持DSI_D0数据通道对)

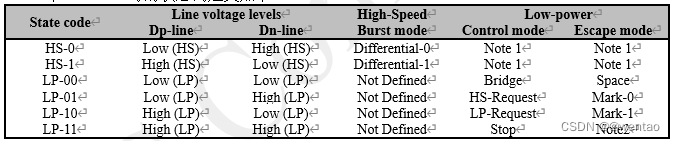

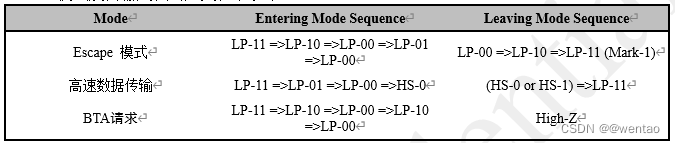

这些模式及其输入代码定义在下表中:

注:

- 采用DSI-D0+/-数据通道。

- 有关“总行周转(BTA)”部分的更多资料。

3.2 Escape模式

Escape模式是低功耗状态下数据通道的一种特殊操作模式。有了这种模式,一些额外的功能就可用了。正向和反向都应支持模式操作。

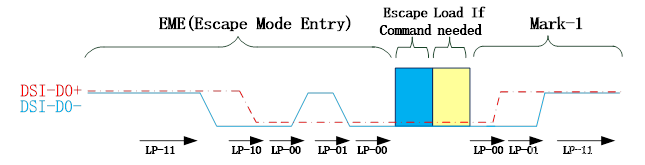

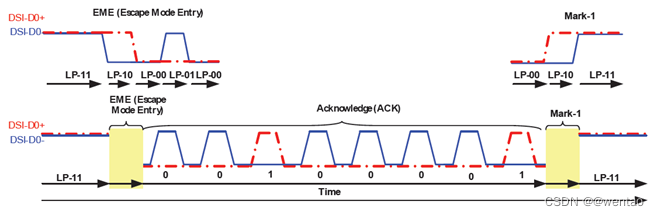

Escape模式的基本顺序如下

•起始:LP-11

•Escape模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•Escape指令,这是编码的,当其中一个数据通道从低到高到低改变时,这个改变的数据通道将呈现当前数据位的值。

•有效载荷流(如果需要的话)

•Exit Escape (Mark-1) LP-00 =>LP-10 =>LP-11

•结束:LP-11

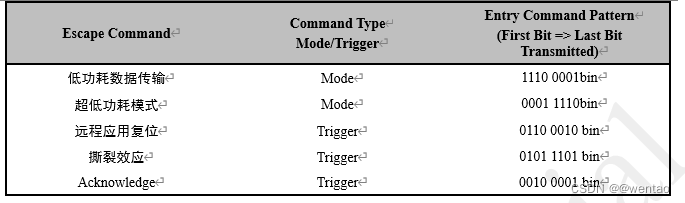

对于Data Lane0,一旦进入Escape模式,发送器将发送一个8位的入口指令来指示请求的操作。下面列出了所有当前可用的Escape模式指令和操作。

•发送或接收“低功耗数据传输”(LPDT)

•将数据通道驱动到“超低功耗状态”(ULPS)

•指示“远程应用复位”(RAR):正在复位显示模块(同S/W复位功能)

•显示“撕裂效应”(TEE),用于从显示模块到MCU的TE行事件。

•指示“Acknowledge”(ACK),用于从显示模块到MCU的非错误。

停止状态应用于退出Escape模式,并且由于Spaced-One-Hot 编码,在Escape模式操作期间不能发生。停止状态立即将车道返回到控制模式。如果输入指令与支持的指令不匹配,则忽略特定的Escape模式动作,接收端等待,直到发送端返回到停止状态。对于数据的lane1和2,只支持ULPS Escape模式指令。

•将数据通道驱动到“超低功耗状态”(ULPS)

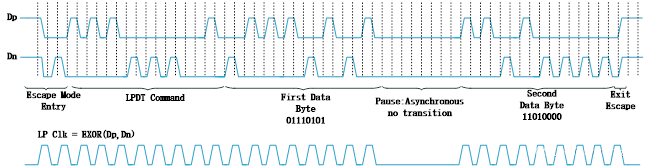

基本结构如下图所示:

不同的Escape指令数量是8。这八种不同的Escape指令可以分为两组:模式或触发。下面定义了Escape指令组。

MCU正在以模式控制数据通道(DSI-D0+/-)来通知显示模块,例如,MCU可以通知显示模块将数据通道置于低功耗模式。

MCU正在等待来自显示模块的事件信息,这是由MCU设置的,具有触发器,例如当显示模块达到新的v-synch时,如果MCU请求它,显示模块会发送给MCU一个TE触发器(TEE),

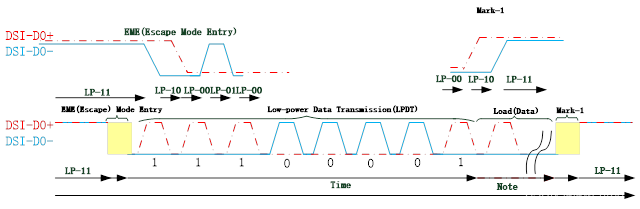

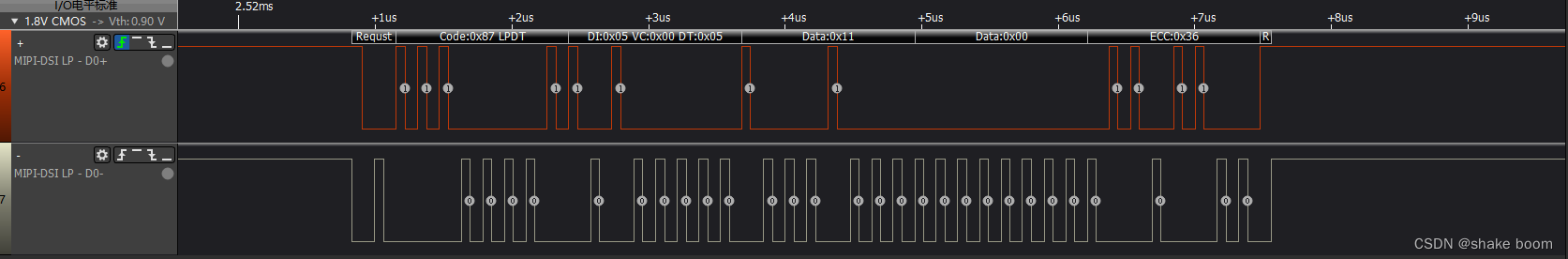

3.2.1 低功耗数据传输 (LPDT)

当数据通道进入Escape模式,且LPDT (Low-Power data Transmission)指令已经发送到显示模块时,MCU可以以LPDT (Low-Power data Transmission)模式向显示模块发送数据。显示模块在向MCU发送数据时也使用相同的顺序。

低功率数据传输(LPDT)使用以下顺序:

•起始:LP-11

•Escape模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•Escape模式下的低功率数据传输(LPDT)指令:1110 0001(从第一位到最后一位)

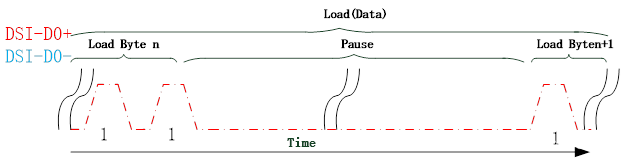

•有效载荷(数据):

—一个或多个字节

—当数据通道在字节之间停止(两个通道都是低电平)时,数据通道处于暂停模式

•Mark-1: LP-00 =>LP-10 =>LP-11

•结束:LP-11

为了便于参考,这个序列如下所示:

注意:在这个例子中,Load(Data)表示第一个位是逻辑“1”

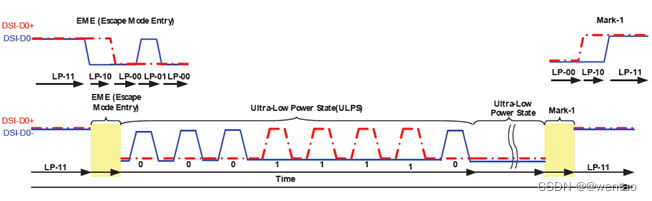

3.2.2 超低功耗状态 (ULPS)

当数据通道进入Escape模式时,MCU可以强制数据通道进入超低功耗状态(ULPS)模式。

超低功耗状态(Ultra-Low Power State, ULPS)使用以下顺序:

•起始:LP-11

•逃逸模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•Escape模式下的超低功率状态(ULPS)指令:0001 1110(从第一位到最后一位)

•超低功耗状态(ULPS),当MCU保持低数据通道时

•Mark-1: LP-00 =>LP-10 =>LP-11

•结束:LP-11

以下是这个顺序的说明,以供参考:

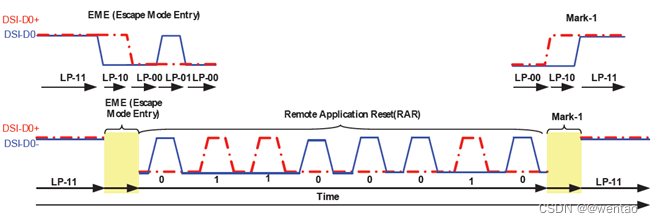

3.2.3 远程应用复位 (RAR)

当数据通道进入Escape模式时,MCU可以通知显示模块应该在远程应用复位(RAR)的触发下进行复位。远程应用程序重置使用的顺序以下:

•起始:LP-11

•Escape模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•Escape模式下的RAR (Remote Application Reset)指令:0110 0010 (First to Last bit)

•Mark-1: LP-00 =>LP-10 =>LP-11

•结束:LP-11

以下是这个顺序的说明,以供参考:

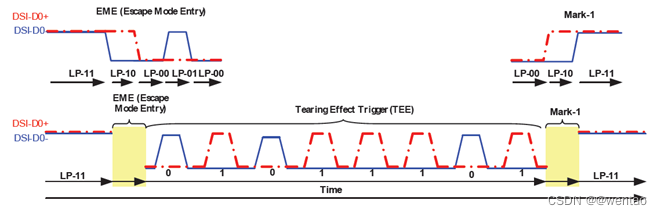

3.2.4 撕裂效应 (TEE)

当显示模块发生撕裂效应事件(New V-synch)时,显示模块可以通过撕裂效应(TEE)通知MCU。

撕裂效果(TEE)使用以下顺序:

•起始:LP-11

•Escape模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•撕裂效果(TEE)触发Escape模式:0101 1101(第一个到最后一个位)

•Mark-1: LP-00 =>LP-10 =>LP-11

•结束:LP-11

以下是这个顺序的说明,以供参考:

图:撕裂效果(TEE)

3.2.5 Acknowledgement (ACK)

当错误没有被Acknowledge(ACK)确认时,显示模块可以通知MCU。

确认(ACK)使用以下顺序:

•起始:LP-11

•逃逸模式入口:LP-11 =>LP-10 =>LP-00 =>LP-01 =>LP-00

•转义模式下的确认(ACK)指令:0010 0001(从第一位到最后一位)

•Mark-1: LP-00 =>LP-10 =>LP-11

•结束:LP-11

以下是这个顺序的说明,以供参考:

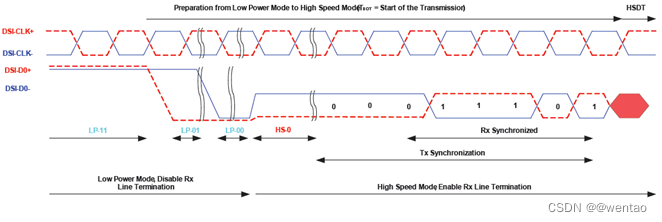

3.3 高速数据传输

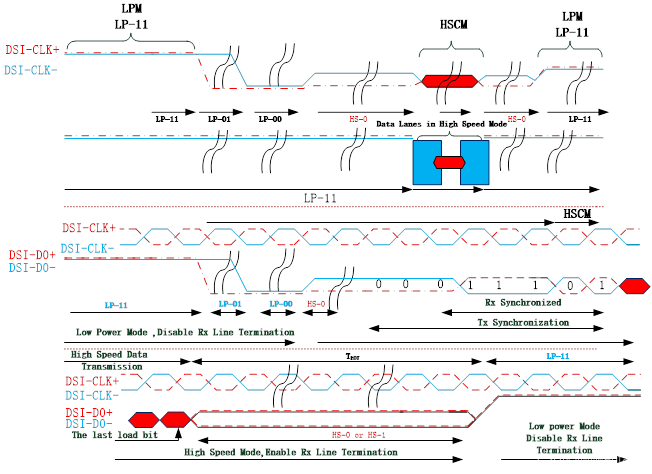

3.3.1 输入高速数据传输(Tsot of HSDT)

当DSI-CLK+/-时钟行已经由MCU进入高速时钟模式(HSCM)时,显示模块正在进入高速数据传输(HSDT)。更多信息参见“高速时钟模式(HSCM)”一章。

显示模块的数据通道DSI-D0+/-在高速数据传输(HSDT)中进入(TSOT)如下

•开始:LP-11

•HS-Request: LP-01

•HS-Settle: LP-00 =>HS-0 (Rx: Lane Termination Enable)

•Rx同步:011101 (Tx (= MCU)同步:0001 1101)

•结束:高速数据传输(HSDT) -准备接收高速数据负载

这个相同的输入高速数据传输(HSDT的TSOT)序列如下所示。

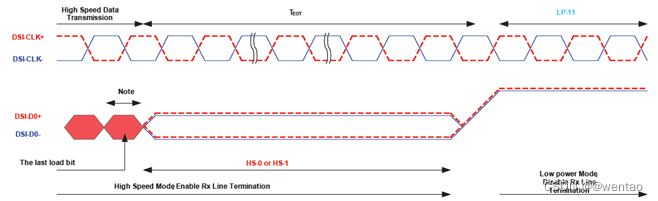

3.3.2 退出高速数据传输 (TEOT of HSDT)

当DSI- CLK+/-时钟行处于MCU的高速时钟模式(HSCM)时,显示模块离开高速数据传输(HSDT的TEOT),直到DSI- d0 +/-数据行处于LP-11模式。更多信息请参见“6.2.2.2高速时钟模式(HSCM)”章节。显示模块的DSI-D0+/-数据通道离开高速数据传输(HSDT的TEOT)的过程如下

•启动:高速数据传输(HSDT)

•停止高速数据传输

-如果最后一个烧录位为HS-0,则mcu更改为HS-1

-如果最后一个烧录位为HS-1,则mcu更改为HS-0

•结束: LP-11 (Rx: Lane Termination Disable)

这个相同的离开高速数据传输(HSDT的TEOT)序列如下所示。

如果最后一个负载位为HS0,则发射机由HS0变为HS-1

如果最后一个负载位为HS1,则发射机从HS1变为HS-0.

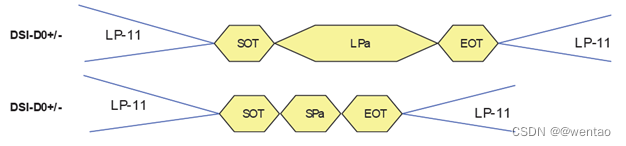

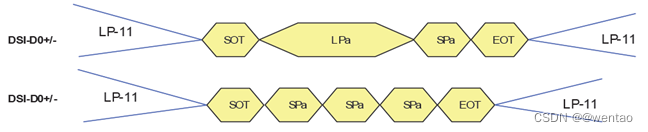

高速数据传输(HSDT)时的burst

高速数据传输(HSDT)的burst 以由一个数据包或多个数据包组成。这些数据包可以是长包(LPa)或短包(SPa)。这些包在“短包(SPa)和长包(LPa)结构”一章中定义。这些不同的高速数据传输(HSDT)的burst在下面进行了说明,以供参考。

3.4 总行方向转换

控制DSI-D0+/-数据通道的MCU或显示模块,当需要从接收端接收信息时,可以启动总行转换程序,接收端可以是MCU或显示模块。

当使用此总行转换程序时,MCU和显示模块使用相同的顺序。

此顺序描述仅供参考,当MCU要做总行转到显示模块的程序时,如下所示。

•启动(MCU):LP-11

•周转请求(MCU): LP-11 =>LP-10 =>LP-00

•MCU等待,直到显示模块开始控制DSI-D0+/-数据通道,MCU停止控制DSI-D0+/-数据通道(= High-Z)

•显示模块切换到停止模式:LP-00 =>LP-10 =>LP-11

相同的总行转换过程(从MCU到显示模块)如下图所示.

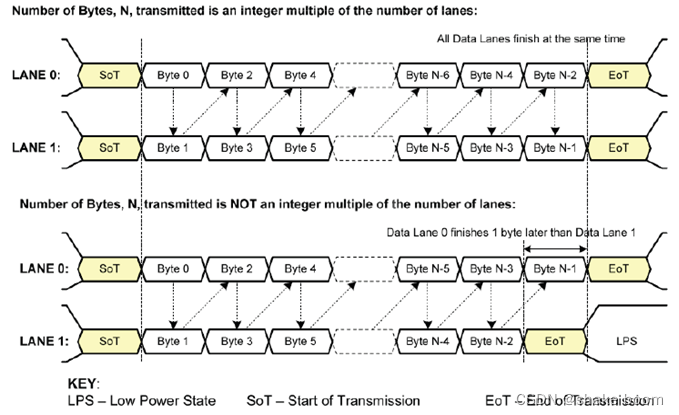

3.5 双数据通道高速传输

由于HS传输是由任意数量的字节组成的,这些字节可能不是通道数的整数倍,因此一个通道可能比另一个通道先用完数据。因此,当通道管理层缓冲最后一组小于2字节的数据时,将其“有效数据”信号释放到所有没有进一步数据的通道中。虽然所有的通道都是通过并行的SoTs同时开始的,但每个通道都是独立运行的,可以在另一个通道之前完成HS传输,提前一个周期(字节)发送EoT。

链路接收端的两个物理层并行地收集字节并将它们馈送到lane management层。通道管理层在传输过程中重建原始的字节序列。如图显示了一个HS传输可以终止两个数据通道HS传输的方式。.

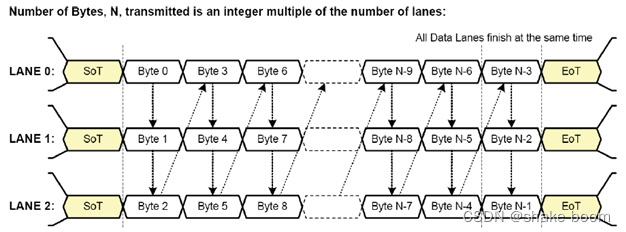

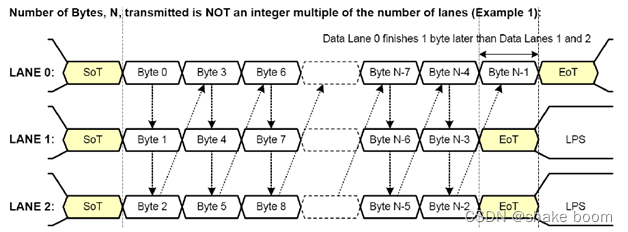

3.6 三数据通道高速传输

由于HS传输是由任意数量的字节组成的,这些字节可能不是lane数的整数倍,因此一些lane可能会在其他lane之前耗尽数据。因此,Lane Management层在缓冲最后一组小于n字节的数据时,将其“有效数据”信号释放到没有进一步数据的所有Lane中。

虽然所有的Lane都同时启动于并行的SoTs,但每条Lane都是独立运行的,可以在其他Lane之前完成HS传输,提前一个周期(字节)发送EoT。链路接收端的N个物理层并行收集字节,并将其馈送到Lane Management层。Lane Management层重构传输中的原始字节序列。

下图说明了不同的通道数和数据包长度的HS传输可以终止的各种方式

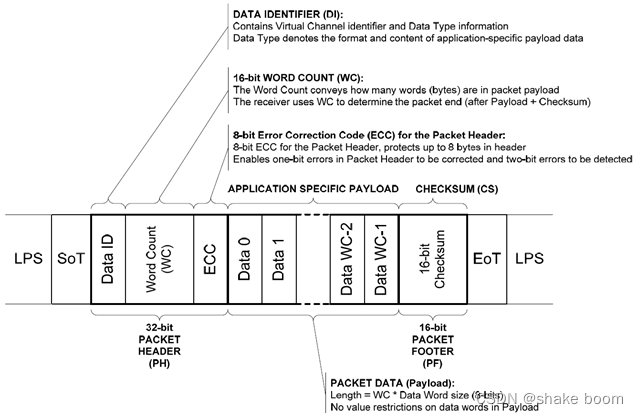

4、 数据包级的信息

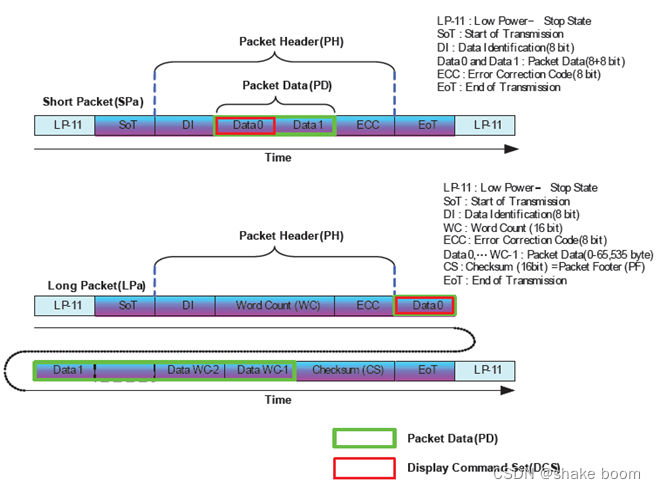

4.1 短数据包和长数据包结构

在低功耗数据传输(LPDT)或高速数据传输(HSDT)模式下进行数据传输时,通常使用短包(SPa)和长包(LPa)。

包的长度为

—SPa (Short Packet): 4字节

—LPa (Long Packet):长度为6 ~ 65535字节

数据包的类型(SPa或LPa)可以通过其包头(PH)来识别。

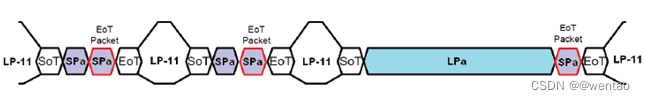

注:“短包(SPa)结构”和“长包(LPa)结构”表示单个包发送的(=包括每个包发送的LP-11, SoT和EoT)。

另一种可能性是,如果数据包以多种数据包格式发送,则数据包之间不需要SoT, EoT和LP-11。例如:

• LP-11 =>SoT =>SPa =>LPa =>SPa =>SPa =>EoT =>LP-11

• LP-11 =>SoT =>SPa =>SPa =>SPa =>EoT =>LP-11

• LP-11 =>SoT =>LPa =>LPa =>LPa =>EoT =>LP-11

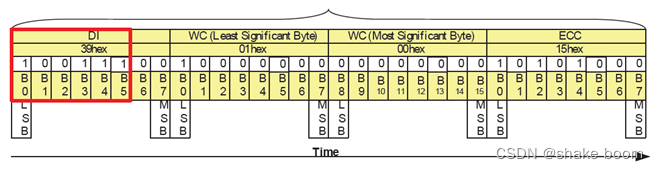

4.1.1 数据包上字节的位顺序

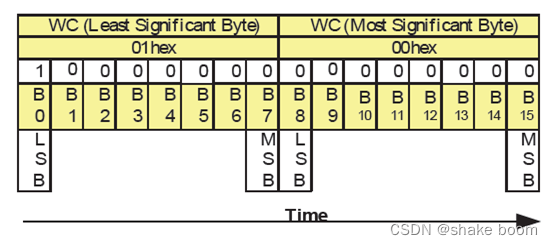

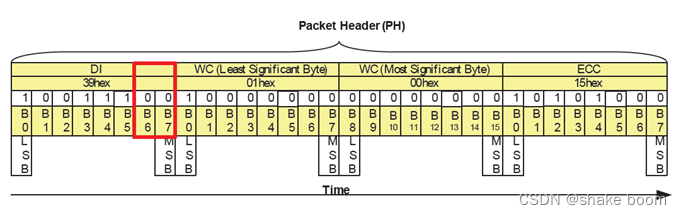

所有包数据都以字节的形式通过接口。发送器按顺序先发送LSB数据,后发送MSB数据。对于具有多字节字段的数据包,除非另有规定,否则应首先传输最低有效字节。图6.2.26显示了一个完整的长包数据传输。注意,该图以标准位置表示法显示了字节值,即MSB在左边,LSB在右边,而位是按时间顺序显示的,LSB在左边,MSB在右边,时间从左到右递增。

4.1.2 数据包中多字节信息的字节顺序

包中使用的多字节信息的字节顺序是:LS (Least Significant)字节在第一个发送,MS (Most Significant)字节在最后发送。例如,单词计数(WC)由2字节(16位)组成,其中LS字节在第一个字节中发送,MS字节在最后一个字节中发送。

下面以同样的顺序进行说明,以供参考。

4.1.3 数据包开头 (PH)

数据包开头总是由4个字节组成。这4个字节的内容在用于短数据包(SPa)和长数据包(LPa) 时是不同的。

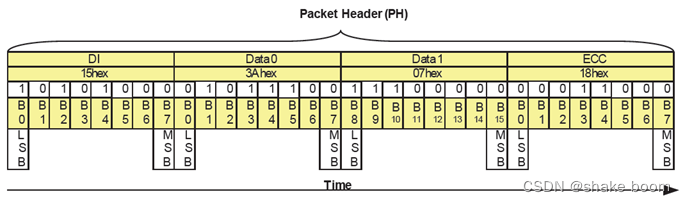

短数据包(SPa):

•第1个字节:数据识别(DI) =>标识这是短数据包(SPa)

•第2和第3字节:数据包数据(PD),数据0和1

•第4字节:纠错码(ECC)

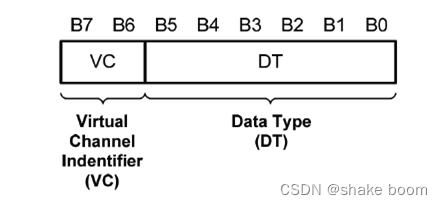

4.1.4 数据识别

数据识别(DI)是数据包开头(PH)的一部分,它由两部分组成:

•虚拟通道(VC), 2位,DI[7…6]

•数据类型(DT), 6位,DI[5…0]

数据标识(DI)结构如下表所示。

数据识别(DI)在数据包开头(PH)中进行了说明,以供下文参考。

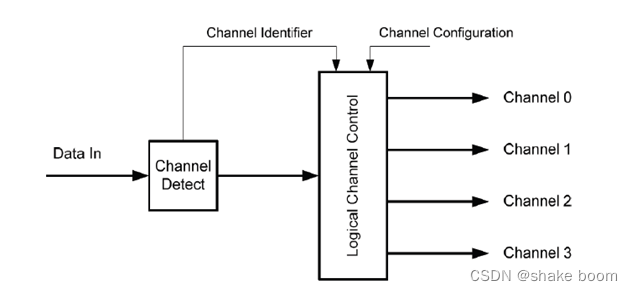

4.1.5 虚拟通道 (VC)

一个处理器最多可以用带标签的指令或数据块服务四个外设,使用针对不同外设的数据包报头的虚拟通道ID字段。

虚拟通道(VC)是数据识别(DI[7…6])结构的一部分,它用于寻址数据包从MCU发送到哪里。下面给出了虚拟通道(VC)的位作为参考。

有些IC 只支持VC代码=00,与其他VC代码包(01/10/11)将被过滤掉。

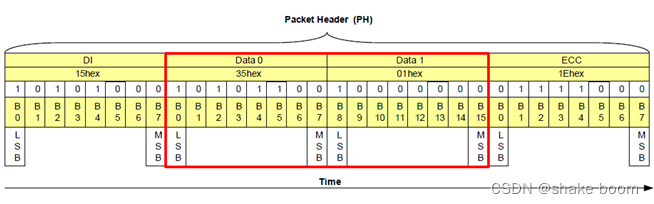

4.1.6 短数据包上的数据

短数据包(Spa)的数据包(PD)是在DI (Data Identification)的DT (Data Type)表示需要发送SPa (Short Packet)后定义的。SPa (Short Packet)的PD (Packet Data)由两个数据字节组成:Data 0和Data 1。PD (Packet Data)的发送顺序是先发送数据0,后发送数据1。如果信息长度为1字节,则数据1的位设置为00h。当信息长度为1或2字节时,短数据包(SPa)的分组数据(PD)将在下面进行说明,以供参考。

• Data 0: 10hex

• Data 1: 00hex (Null)

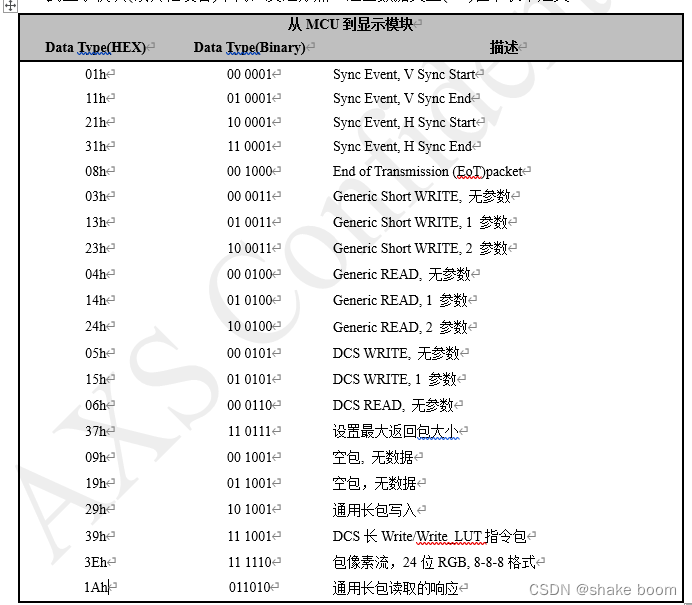

4.1.7 数据类型 (DT)

数据类型(DT)是数据识别(DI[5…0])结构的一部分,用于定义数据包上使用的数据的类型

数据类型(DT)的位在下面进行了说明,以供参考。

此数据类型(DT)还定义了使用的数据包是短数据包(SPa)还是长数据包(LPa)。数据类型(DT)从MCU到显示模块(或其他设备)不同,反之亦然。这些数据类型(DT)在下表中定义。

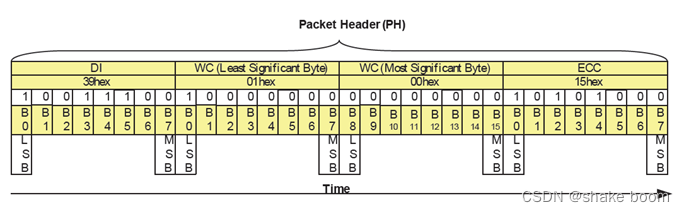

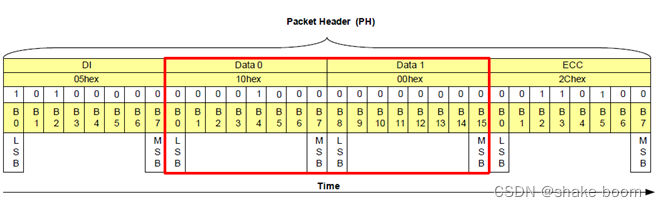

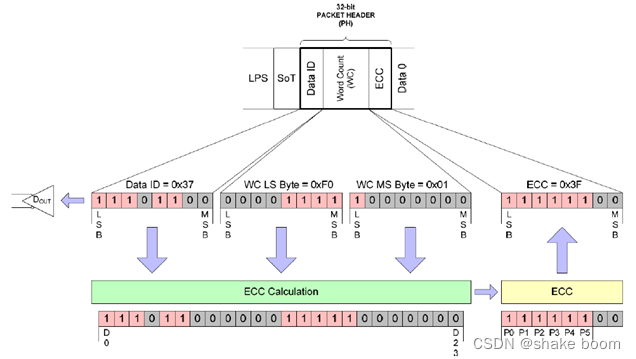

4.1.8 长数据包中的字数统计

Word长包的字数WC (Word Count)是在DI (Data Identification)的数据类型DT (Data Type)指示要发送长包之后定义的。字数(WC)表示在包头(PH)与短包(SPa)的包数据(PD)放置在包头(PH)之后想要发送的包数据(PD)的数据字节数。LPa (Long Packet)的WC (Word Count)由2字节组成。

单词计数(WC)的这两个字节的发送顺序是,最少有效字节(LS)在第一个发送,最多有效字节(MS)在最后发送。

长数据包(LPa)的字数统计(WC)在下面进行了说明,以供参考。

4.1.9 纠错码(ECC)

是包头(PH)的一部分,其目的是识别错误:

•短数据包(SPa):数据识别(DI)和数据包数据(PD)字节(24位:D[23…0])

•长数据包(LPa):数据识别(DI)和单词计数(WC)字节(24位:D[23…0])

D[23…0]如下图所示,以供参考。

![图:短包上的D[23:0]和P[7:0]](https://i-blog.csdnimg.cn/blog_migrate/e0d2cbb96a339564ffbbec4e6c6ce663.png)

![图:长包上的D[23:0]和P[7:0]](https://i-blog.csdnimg.cn/blog_migrate/abc9794d906f918064cd4c483604bbee.png)

纠错码(ECC)可以识别一个错误、多个错误,并在一个比特错误的情况下进行纠错。

定义纠错码(ECC)的位(P[7…0]),其中符号“^”表示异或函数(“1”为奇数时Pn为“1”,“1”为偶数时Pn为“0”),如下:

ecc_parity = {P7,P6,P5,P4,P3,P2,P1,P0};;

• P7 = 0

• P6 = 0

• P5 = D10D11D12D13D14D15D16D17D18D19D21D22D23

• P4 = D4D5D6D7D8D9D16D17D18D19D20D22D23

• P3 = D1D2D3D7D8D9D13D14D15D19D20D21D23

• P2 = D0D2D3D5D6D9D11D12D15D18D20D21D22

• P1 = D0D1D3D4D6D8D10D12D14D17D20D21D22^D23

• P0 = D0D1D2D4D5D7D10D11D13D16D20D21D22^D23

P7和P6被设置为“0”,因为纠错码(ECC)是基于64位值([D63…0]),但这个实现是基于24位值(D[23…0])。因此,纠错码(ECC)只需要6比特(P[5…0])。

c++实现校验:

//check

U8 Helpers::CalculateECC(U8 *ptr)

{

U8 D[24] = { 0 };

U8 count = 0;

U8 ECC[8] = { 0 };

for (U8 i = 0; i < 3; i++) {

for (U8 j = 0; j < 8; j++) {

D[count] = *ptr & 0x01;

U8 data = *ptr;

*ptr = data >> 1;

count++;

}

ptr++;

}

ECC[7] = 0;

ECC[6] = 0;

ECC[5] = D[10] ^ D[11] ^ D[12] ^ D[13] ^ D[14] ^ D[15] ^ D[16] ^ D[17] ^ D[18] ^ D[19] ^ D[21] ^ D[22] ^ D[23];

ECC[4] = D[4] ^ D[5] ^ D[6] ^ D[7] ^ D[8] ^ D[9] ^ D[16] ^ D[17] ^ D[18] ^ D[19] ^ D[20] ^ D[22] ^ D[23];

ECC[3] = D[1] ^ D[2] ^ D[3] ^ D[7] ^ D[8] ^ D[9] ^ D[13] ^ D[14] ^ D[15] ^ D[19] ^ D[20] ^ D[21] ^ D[23];

ECC[2] = D[0] ^ D[2] ^ D[3] ^ D[5] ^ D[6] ^ D[9] ^ D[11] ^ D[12] ^ D[15] ^ D[18] ^ D[20] ^ D[21] ^ D[22];

ECC[1] = D[0] ^ D[1] ^ D[3] ^ D[4] ^ D[6] ^ D[8] ^ D[10] ^ D[12] ^ D[14] ^ D[17] ^ D[20] ^ D[21] ^ D[22] ^ D[23];

ECC[0] = D[0] ^ D[1] ^ D[2] ^ D[4] ^ D[5] ^ D[7] ^ D[10] ^ D[11] ^ D[13] ^ D[16] ^ D[20] ^ D[21] ^ D[22] ^ D[23];

return ECC[7] << 7 | ECC[6] << 6 | ECC[5] << 5 | ECC[4] << 4 | ECC[3] << 3 | ECC[2] << 2 | ECC[1] << 1 | ECC[0];

}

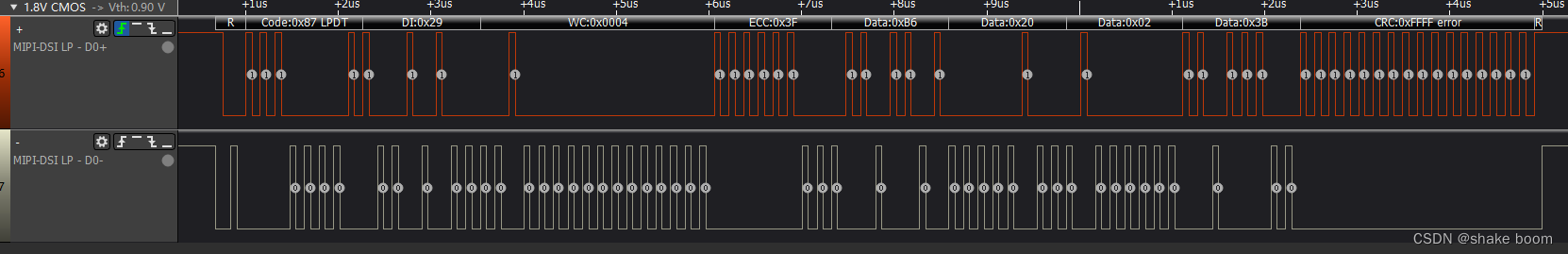

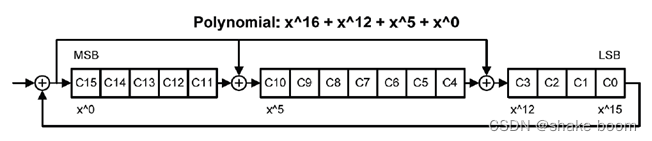

4.1.10 长包封包的结尾

长包(LPa)的封包结尾 (PF)定义在数据包的数据(PD)之后。封包结尾(PF)是一个校验和值,它是从长包(Lpa)的数据包数据中计算出来的。

校验和使用16位循环冗余校验(CRC)值,该值由多项式X16+X12+X5+X0生成,如下所示。

在计算前,将16位循环冗余检查(CRC)生成器初始化为FFFFh。数据包数据(PD)数据字节中最重要的一点(MSB)是第一点,在16位循环冗余检查中被输入到的。接收方从接收数据包数据(PD)计算出自己的校验和值。接收者比较自己的校验和发送器发送的数据包封包结尾。接收数据包数据(PD)和封包结尾(PF)是正确的,如果接收方和封包结尾(PF)的校验和相等,反之亦然,如果接收方和封包结尾(PF)的自己的校验和不相等,则接收数据包数据(PD)和封包结尾值(PF)是不正确的。

4.2 数据包传输

4.2.1 从MCU到显示模块的数据包

显示指令集(DCS),在“指令”一章中定义,用于从MCU到显示模块。这个显示指令集(DCS)

总是定义在包数据(PD)的数据0上,它包含在短包(SPa)和长包(LPa)中,如下所示。

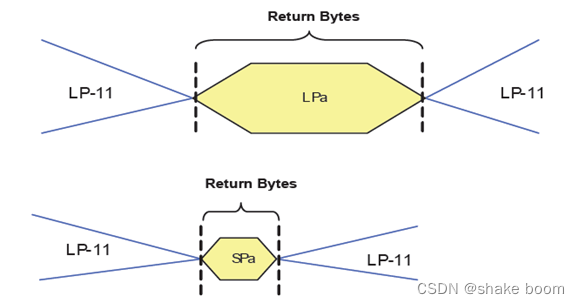

4.2.2 数据包从显示模块到MCU

使用包

当MCU向显示模块请求信息后,显示模块将信息返回给MCU时,显示模块总是使用短数据包(SPa)或长数据包(LPa)。该信息可以是显示指令集(DCS)的响应。

使用的包类型由Data Type (DT)定义。

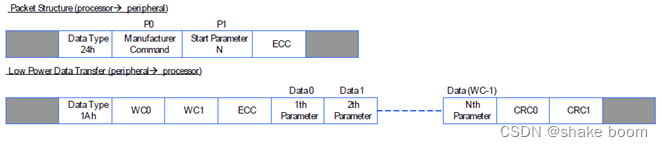

5、 客户定义通用读数据类型格式

数据类型14h (Generic READ, 1个参数)的短包指定要读取的寄存器内容和将开始读取的第n个参数。接收到数据类型14h后,执行BTA。然后,第n个参数成为第一个数据,输出WC(单词计数)值的数据个数。

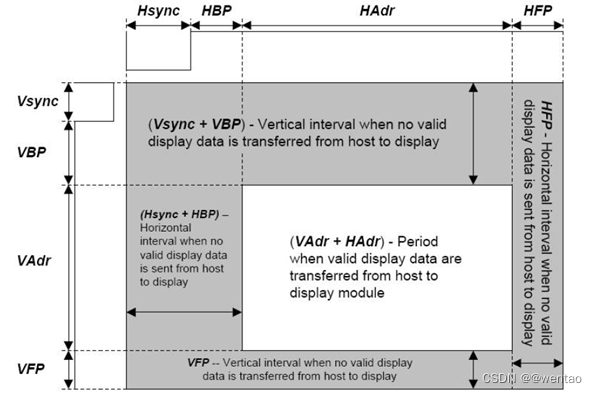

6、MIPI Video 参数

In MIPI视频模式中,帧作为像素序列从主机处理器传输到显示模块,图像数据的每个水平行作为一组连续像素发送。

Vsync (VS)表示显示图像的每一帧的开始。

Hsync (HS)表示像素的每个水平行的开始。

每个像素值(16位、18位、24位数据)在一个像素周期内从主机处理器传输到显示模块。显示模块利用PCLK的上升沿捕获像素数据。由于PCLK是连续运行的,因此需要控制信号DE来指示何时在像素数据信号上传输有效的像素数据。

5399

5399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?