目录

时钟无缝切换(Clock Switching Glitch Free)

FPGA系统设计时可能遇到多个时钟频率输入而需要选择的情况,因此时钟切换电路是必要的,好的切换电路应做到无缝(Glitch Free),对此需要特殊设计。

参考文档:Intel(Altera)《Techniques to Make Clock Switching Glitch Free》

Xilinx ug472《7Series FPGAs Clocking Resources User Guide》

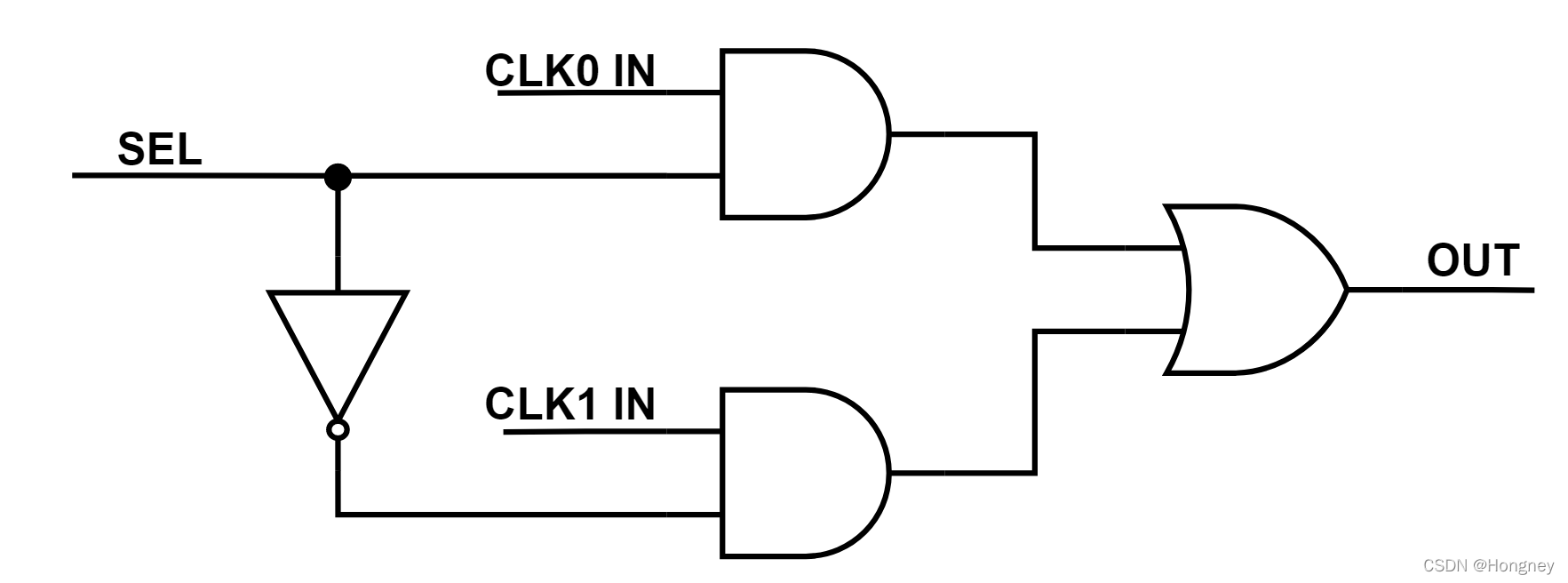

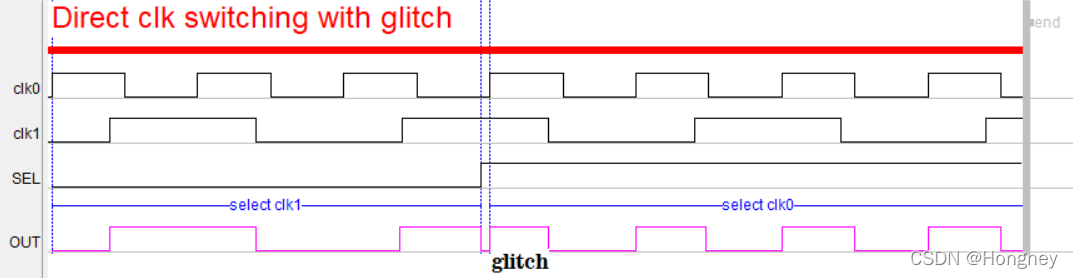

一、直接时钟切换电路

如上图是最简单的时钟切换电路,切换的时序图如下,但是因为组合逻辑电路的无保护性,十分容易产生glitch。

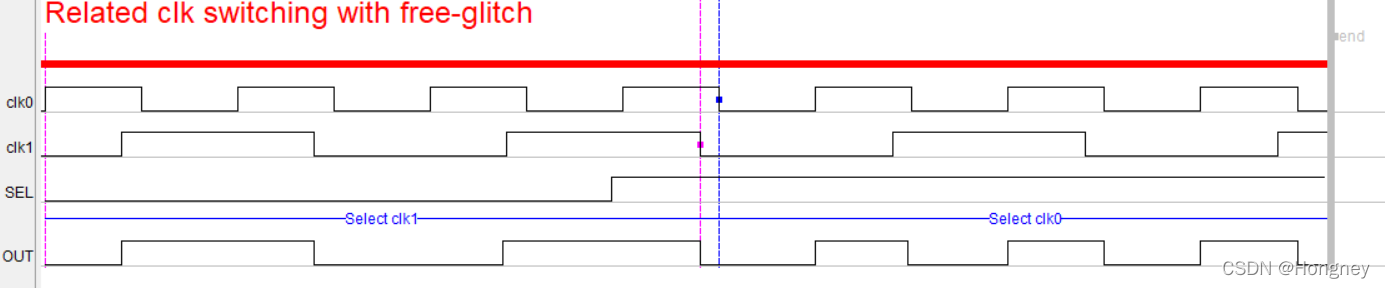

二、一种时钟无缝切换电路(Related clk switching with free-glitch)

1.实现思路:

想实现时钟的无缝切换,就必须先关断当前时钟,再开启新的时钟。“先…,再…”显然纯组合逻辑电路无法实现,因此采用时序逻辑电路结构是必要的,这也是用到D触发器和引入两个反馈线的原因。(原理类似RS触发器)

2.切换时序分析:

1.切换前:SEL为低电平,AND0和DFF0的Q输出始终均为0,CLK0无法达到输出端。DFF0的Q’为始终高电平,SEL过反相器后为高,使DFF1输出始终为高,使后级与门导通,CLK1输出。

2.切换后原时钟关断<

本文介绍时钟切换电路的设计,重点讨论无缝切换电路的实现方法及其改进,并分析Xilinx FPGA时钟资源的应用。

本文介绍时钟切换电路的设计,重点讨论无缝切换电路的实现方法及其改进,并分析Xilinx FPGA时钟资源的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1561

1561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?