时序分析模型

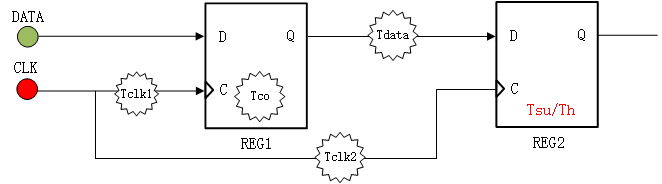

典型的寄存器之间的时序分析模型如下图所示:

FPGA中的时序分析就是分析时钟和数据之间的关系。上图中,展示的是时序分析中最基本的模型,寄存器与寄存器之间的时序分析模型。

建立时间分析

数据从输入到第一级寄存器到输入到第二级寄存器所需要经过的延时由触发器内部延时Tco、寄存器之间数据路径的走线延时Tdata和数据相较于扇出源时钟的延时Tclk1;

所以数据从第一级寄存器到达第二季寄存器的实际的到达时间可以表示为:data_arrival_time = Tclk1 + Tdata + Tco;

由于在这值中需要满足建立时间的要求,要求数据在采样沿时钟到达之间就稳定下来,因此有一个数据要求到达时间:data_arrival_require_time = Tcycle + Tclk2 - Tsu

由此可以推算出建立时间的余量 slack_of_setup = data_arrival_require_time - data_arrival_time

通过绘制时序分析图可以帮助理解。

pad_clk是扇出节点的时钟;

data_in_reg1是数据传输到寄存器1的D端数据,其相较于扇出节点时钟有Tclk1的延时;

Reg1_Q是从寄存器1的Q端输出的数据,其经历了在寄存器内部的延时Tco;

Reg2_D是传输到寄存器2D端的数据,其经历了Tdata的数据走线传输延时;

由此可以看出,数据从扇出节点到寄存器2的D端经历的延时总共为:data_arrival_time = Tclk1 + Tdata + Tco;

再看寄存器2的采样时钟:寄存器2的采样时钟,相较于扇出节点时钟有Tclk2的延时,在寄存器2的采样沿相较于扇出节点的发射沿的时间为:Tcycle + Tclk2

因为要满足建立时间,所以要求数据达到的时间可以表示为:data_arrival_require_time =Tcycle + Tclk2 - Tsu

由此可以计算出建立时间的余量:slack_of_setup = data_arrival_require_time - data_arrival_time = (Tcycle + Tclk2 - Tsu) - (Tclk1 + Tdata + Tco)

保持时间分析

保持时间的分析与建立时间相似,与建立时间不同的是,建立时间需要注意的是数据到达寄存器2的时间,而保持时间注意的是数据结束时间与采样沿的关系。简单来讲就是数据结束的时间不能在采样沿到后的某一段时间之前。这一段时间就是保持时间。

数据的结束时间在前面建立时间的分析上再加上一个时钟周期即使实际结束的时间,也即数据实际结束的时间是数据实际到达的时间加上一个时钟周期:data_finish_time = data_arrival_time + Tcycle

因为要满足保持时间的约定,所以要求的结束时间应该为,寄存器2采样沿到达后再经过一个保持时间,也即:数据要求结束的时间为寄存器2的采样沿后还需加上一个保持时间:data_require_finish_time = Tclk2 + Tcycle + Th

因此保持时间余量可以求得为:slack_of_hold =data_finish_time - data_require_finish_time = (Tcycle + Tclk1 + Tdata + Tco) - (Tcycle + Tclk2 + Th)

647

647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?