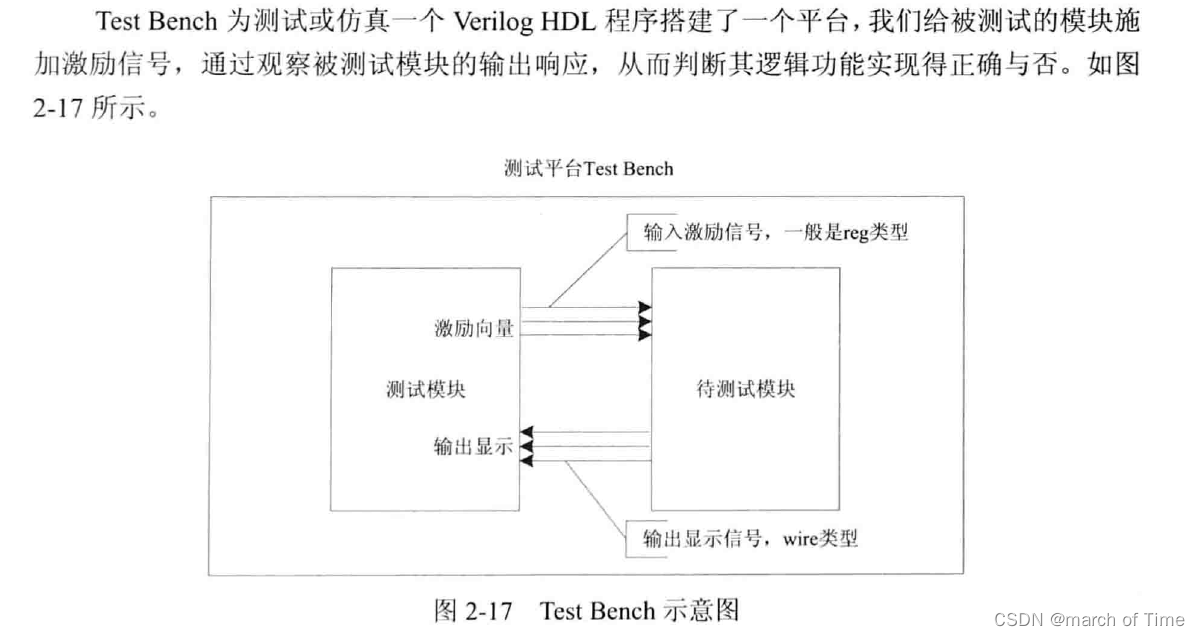

testbench介绍:

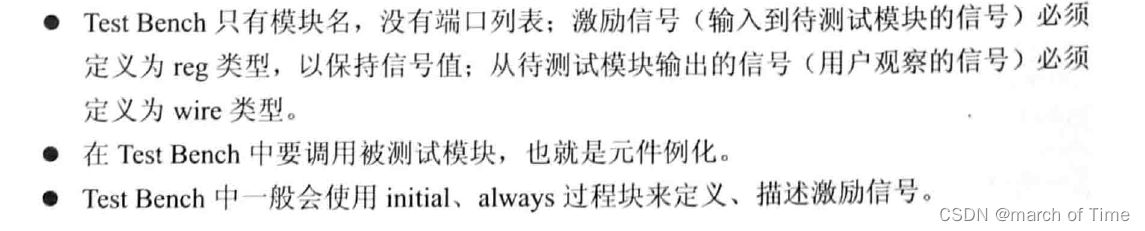

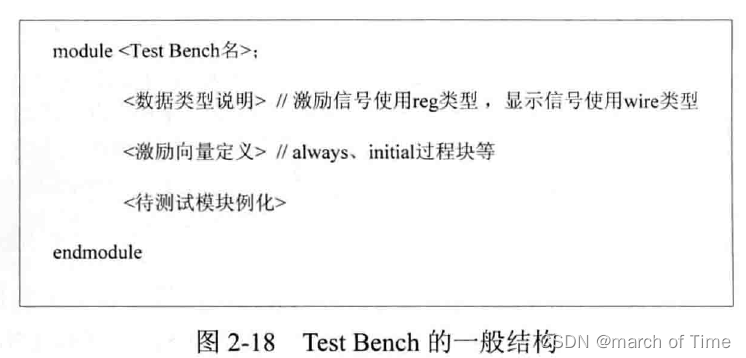

testbench的特点:

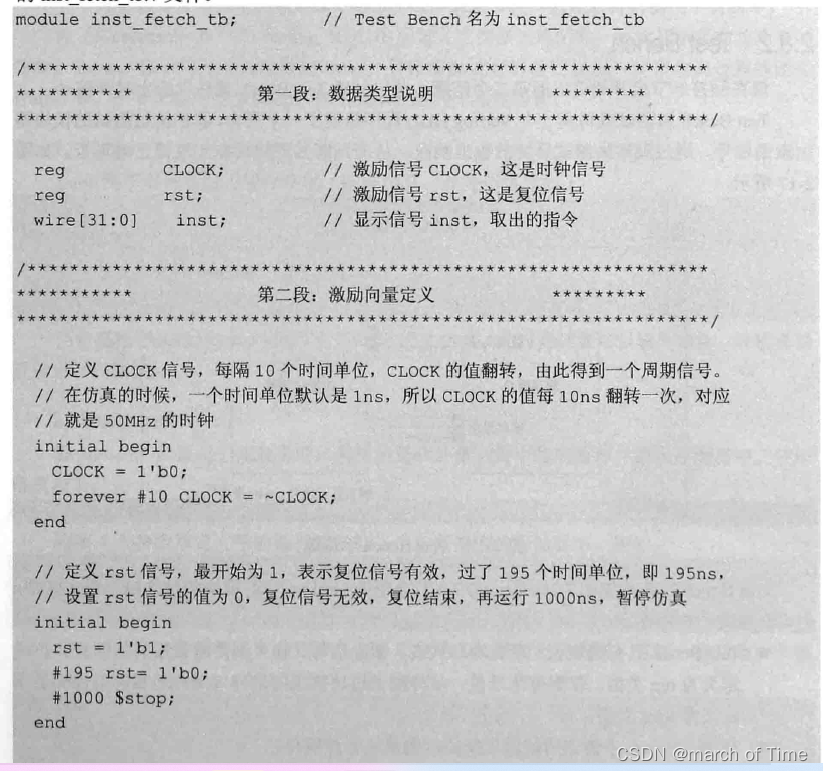

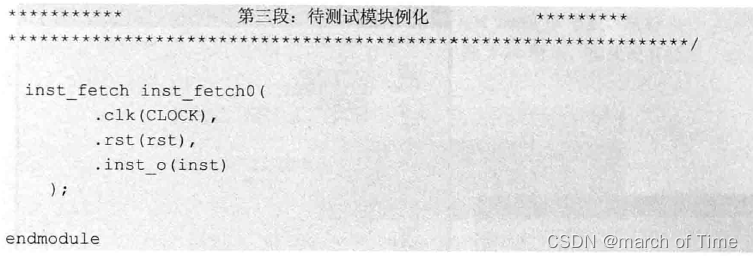

为简单取指指令设计的test bench:

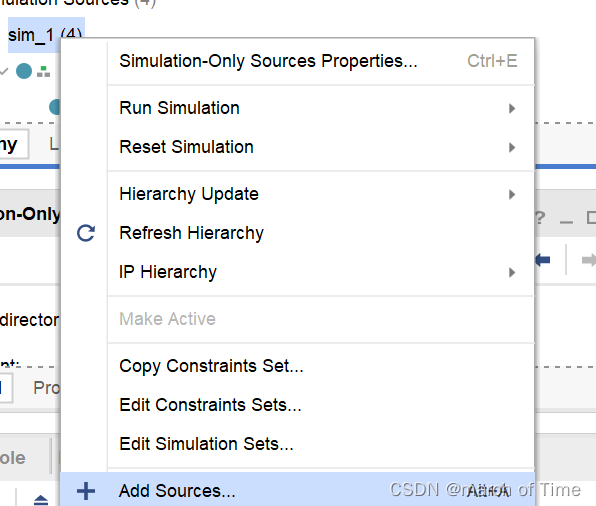

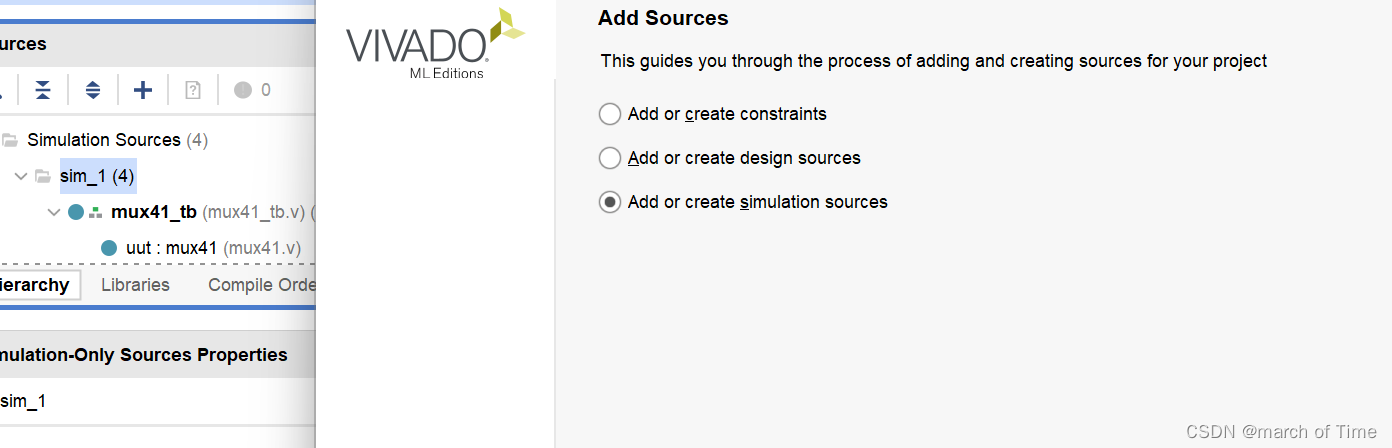

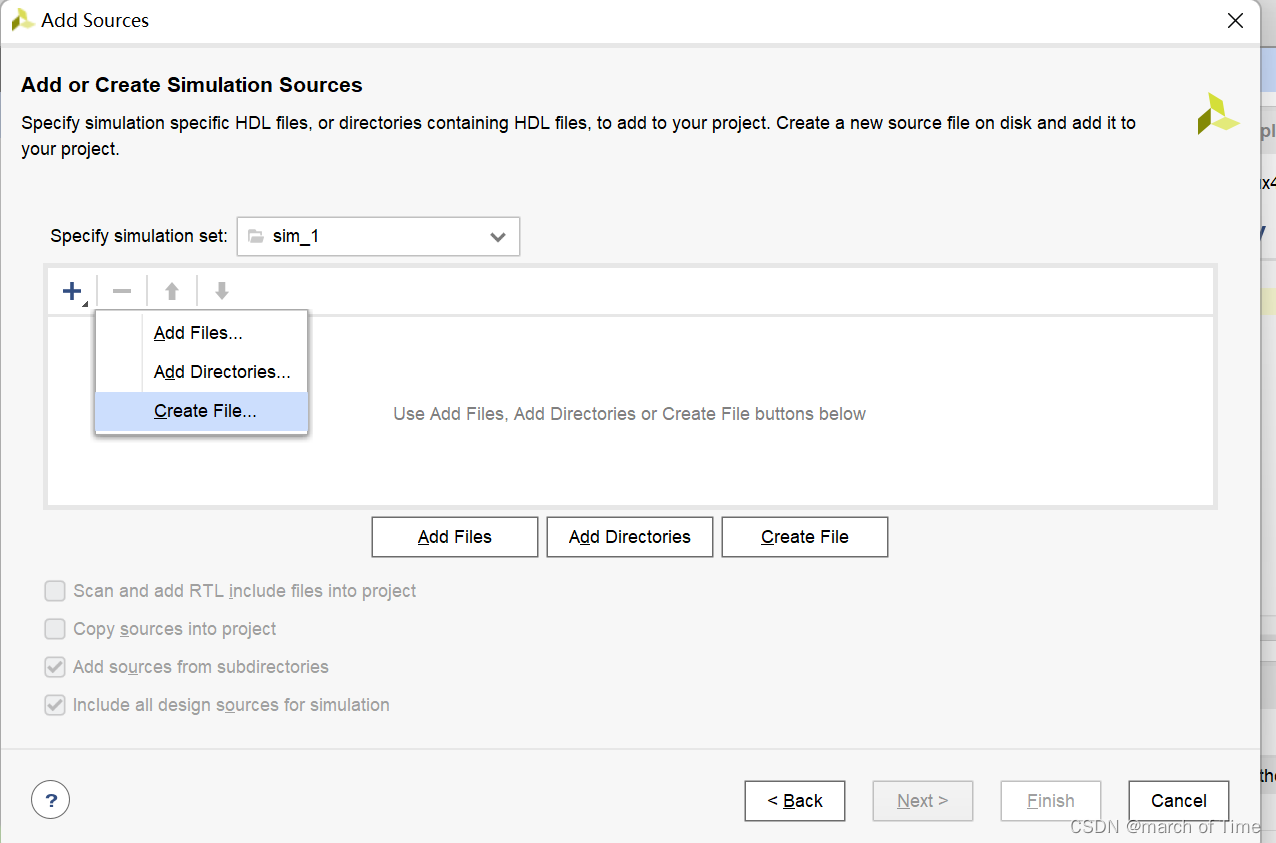

在vivado中创建testbench:

一个testbench的例子:

design sourse:

module mux41(

input wire [3:0] in1,in2,in3,in4,

input wire [1:0] select,

output reg [3:0] out

);

always@* begin

case (select)

2'b00: out=in1;

2'b01: out=in2;

2'b10: out=in3;

2'b11: out=in4;

default: out = 4'bx;

endcase

end

endmodule

testbench文件:

`timescale 1ns / 1ps

module mux41_tb;

reg [3:0] in1,in2,in3,in4;

reg [1:0] select;

wire [3:0] out;

initial begin

in1=4'b0001;

in2=4'b0011;

in3=4'b0111;

in4=2'b1111;

select=2'b00;

#10 select=2'b01;

#10 select =2'b10;

#10 select = 2'b11;

#10 $stop;

end

mux41 uut(

.in1(in1), .in2(in2), .in3(in3), .in4(in4),

.select(select),

.out(out)

);

endmodule

5157

5157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?