#学习记录#

1 四选一数据选择器简述

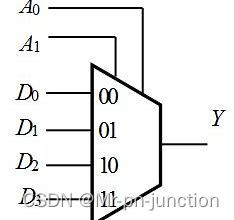

数据选择器的逻辑功能:在地址选择信号的控制下,从多路数据中选择一路作为输出。数据选择器的符号如图1所示,真值表如图2所示。

图1 四选一数据选择器符号

图2 四选一数据选择器真值表

2 mux_41的Verilog描述

2.1 代码

`timescale 1ns / 1ps

// Create Date: 2023/09/24 08:06:19

// Design Name: Mr-pn-junction

// Module Name: mux_41

// Project Name:

module mux_41(

input wire [3:0] d,

input wire [1:0] sel,

output reg data_out

);

always @(*) begin

if(sel == 2'b00)

data_out = d[0];

else if(sel == 2'b01)

data_out = d[1];

else if(sel == 2'b10)

data_out = d[2];

else

data_out = d[3];

end

endmodule2.2 testbench

`timescale 1ns / 1ps

// Create Date: 2023/09/24 08:50:59

// Design Name: Mr-pn-junction

// Module Name: mux_tb

// Project Name:

module mux_tb( );

reg [3:0] d;

reg [1:0] sel;

wire data_out;

mux_41 tb(

.d(d),

.sel(sel),

.data_out(data_out)

);

initial begin

sel = 2'b00;d = 4'b1010;

#10

sel = 2'b01;d = 4'b1010;

#10

sel = 2'b10;d = 4'b1010;

#10

sel = 2'b11;d = 4'b1010;

#10

$stop;

end

endmodule

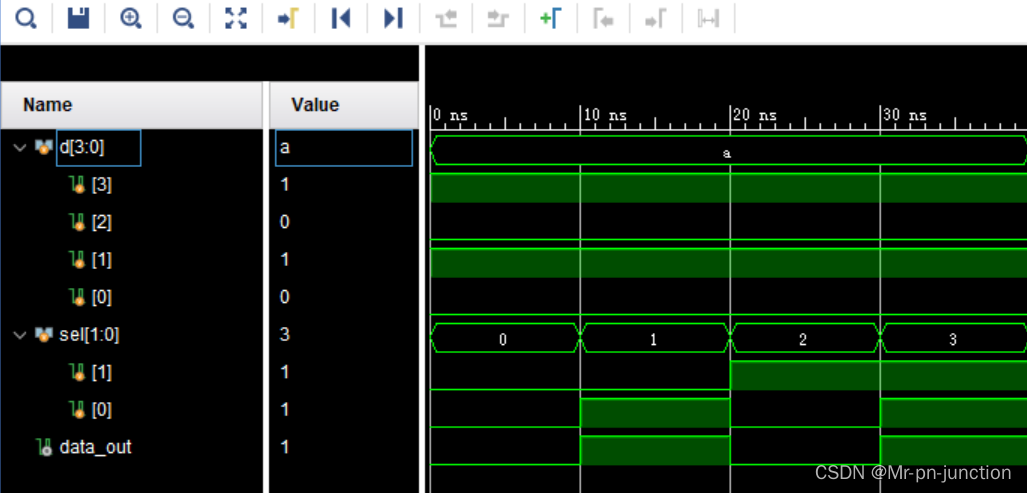

3 仿真结果

图3 仿真结果

参考文献

[1] 四选一数据选择器. 百度百科. 数据选择器_百度百科 (baidu.com)

3780

3780

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?