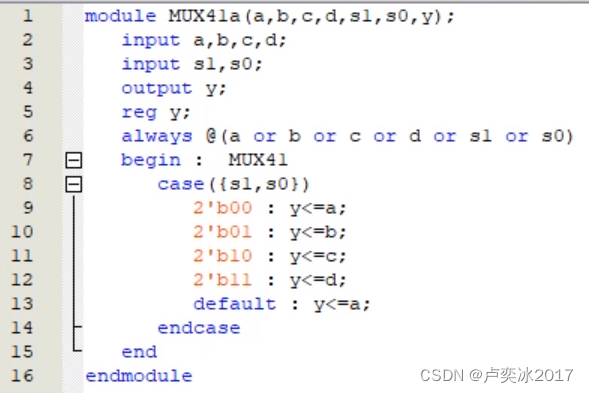

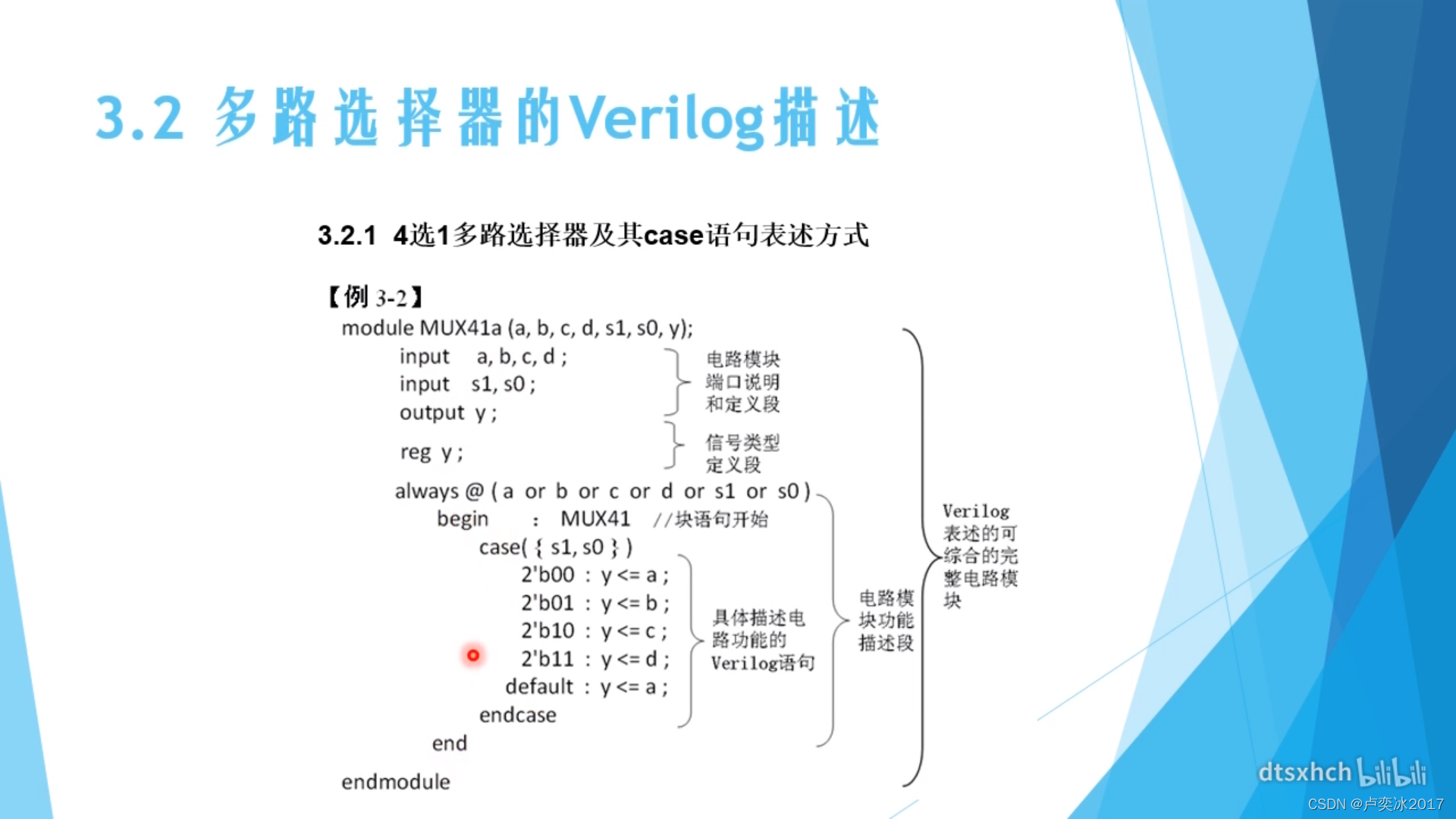

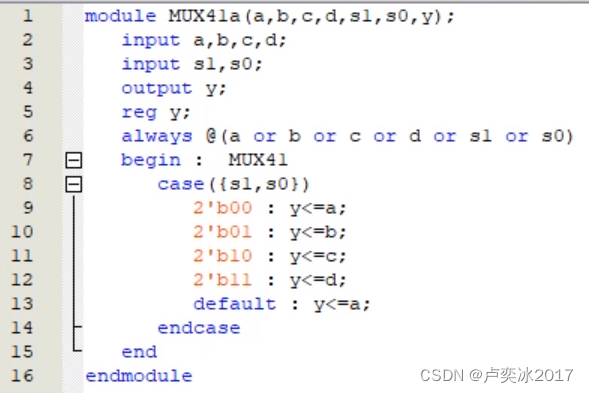

四选一多路选择器的代码如下,保存路径不能有中文!!

文件名保存为模块名。

(Cyclone III-----EP3C40Q240C8)

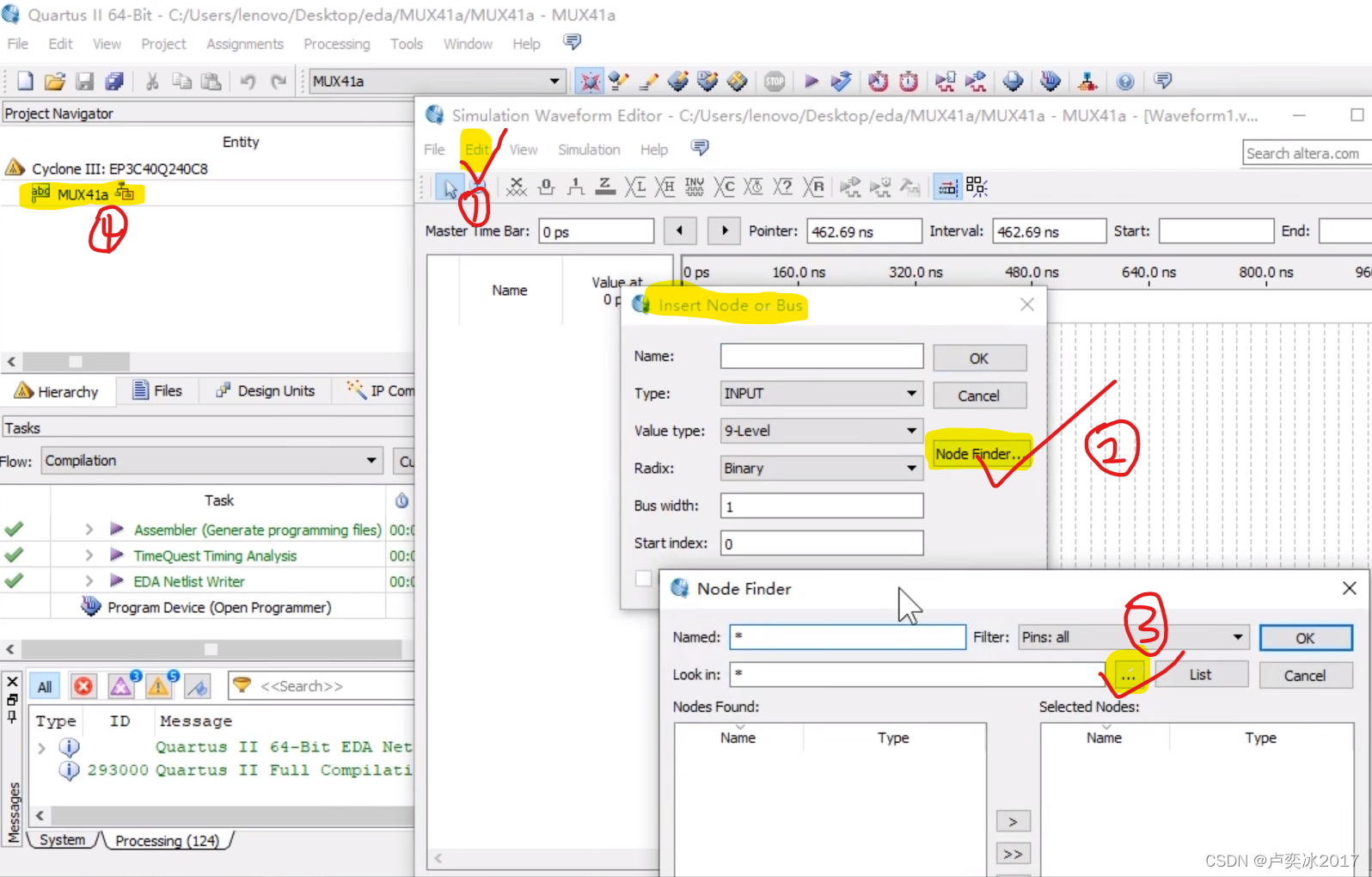

编译无错误后:

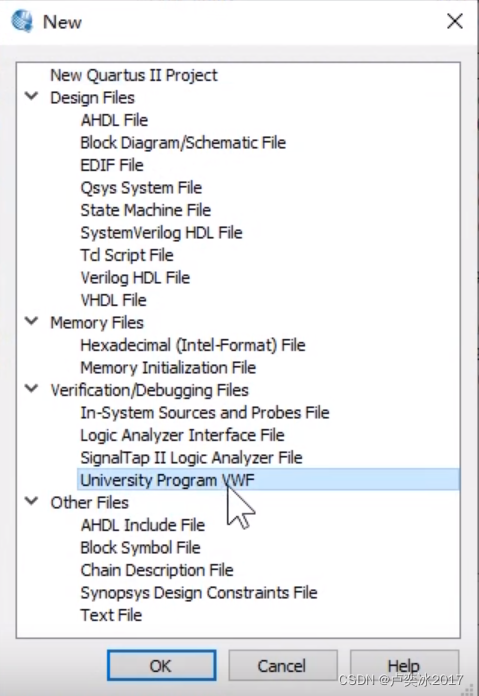

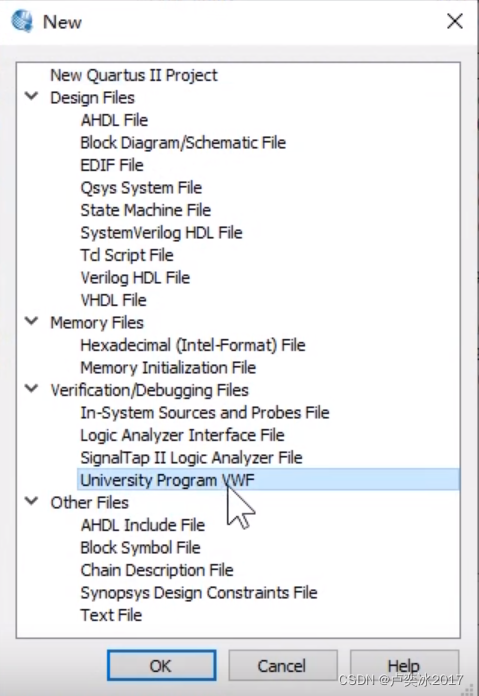

File-New-VMF

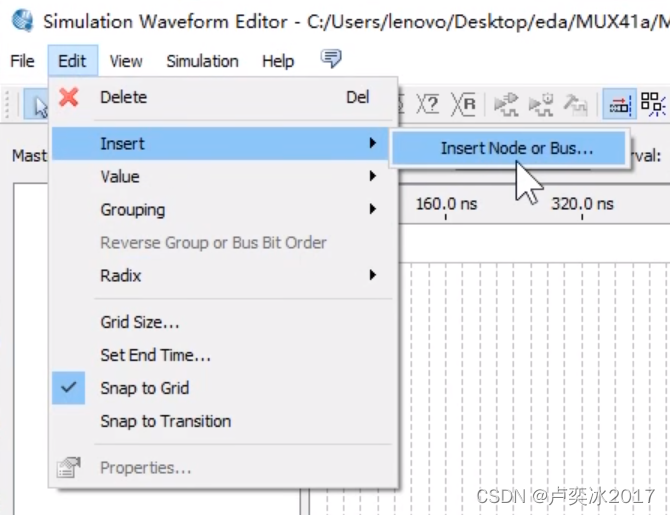

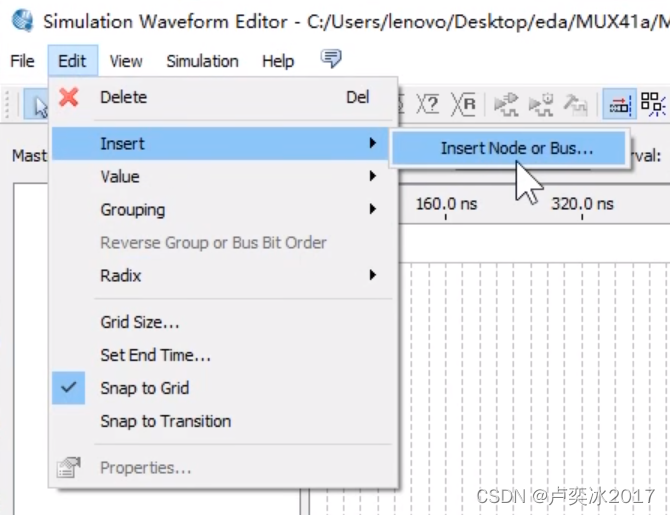

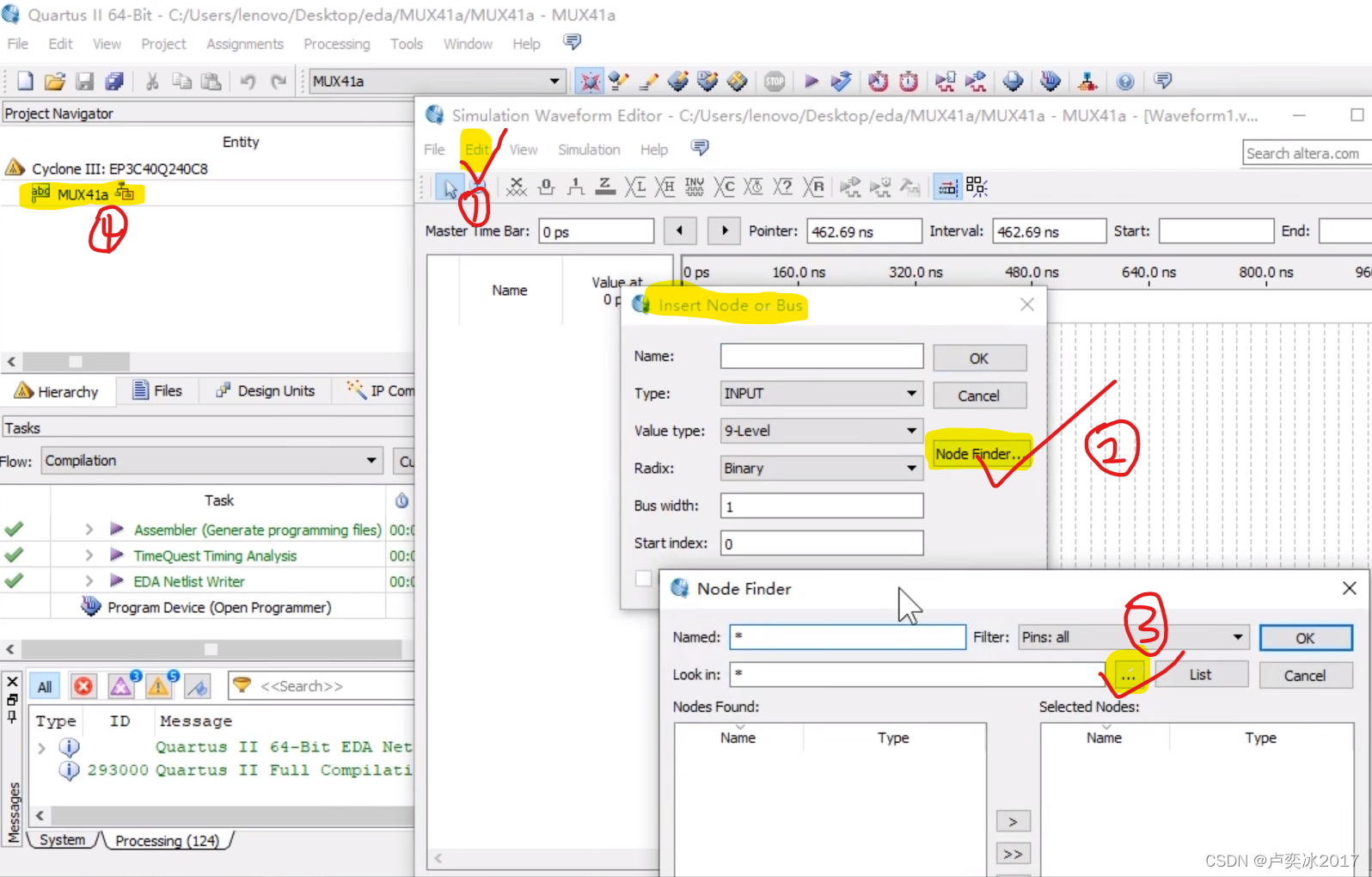

Edit--Insert--

Node Finder

List,全部移入

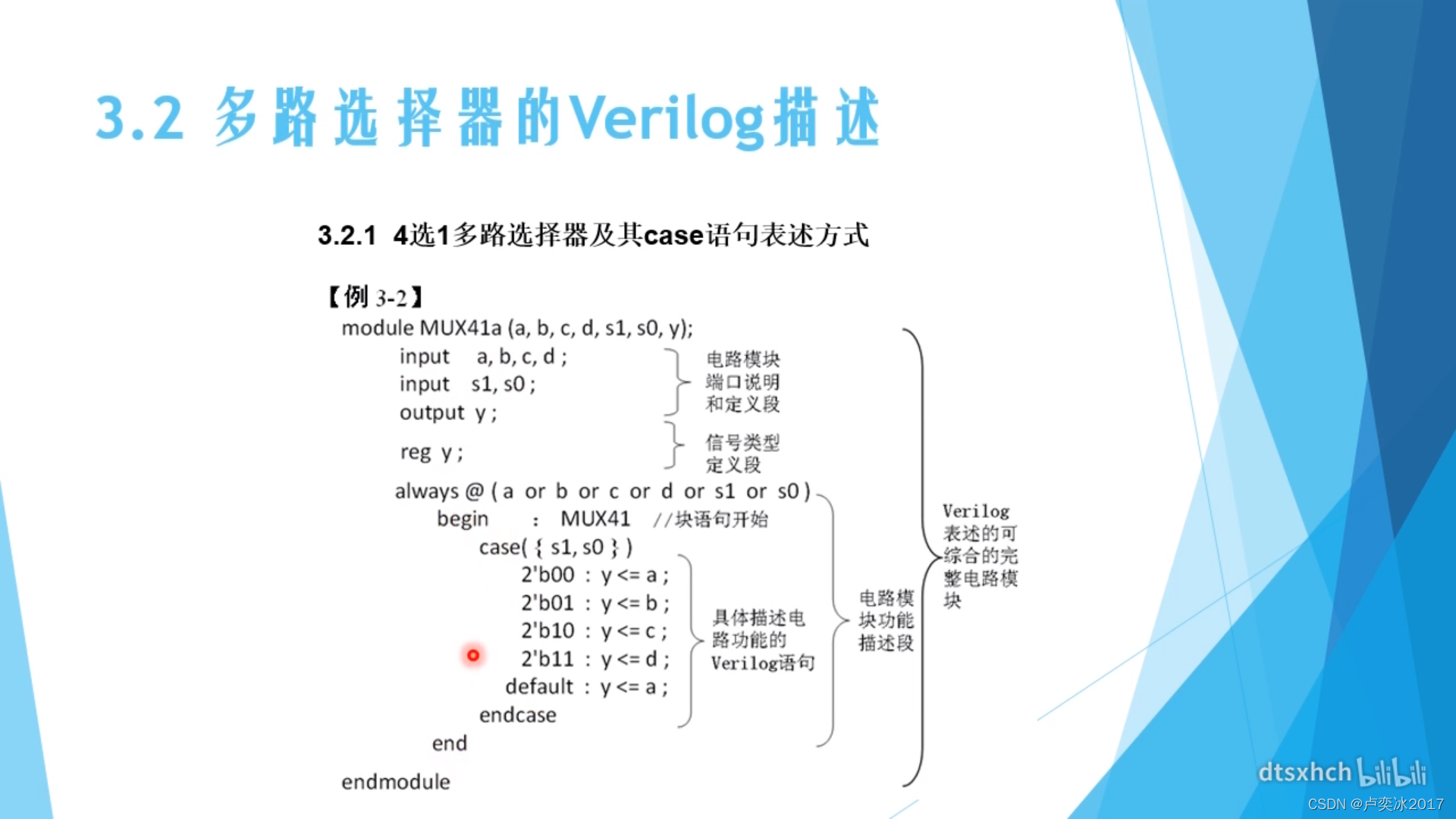

四选一多路选择器Verilog仿真与QuartusII使用教程

四选一多路选择器Verilog仿真与QuartusII使用教程

该博客介绍了如何使用QuartusII软件进行四选一多路选择器的Verilog代码实现,并详细阐述了仿真过程。包括设置信号参数,如a、b、c、d的占空比,以及设置时钟s0和b。在完成设置后,进行了仿真,得到00对应a,10对应c,01对应b,11对应d的运行波形。同时提醒读者注意文件命名规范,确保无中文,并强调软件需正确安装及包含仿真模块。

该博客介绍了如何使用QuartusII软件进行四选一多路选择器的Verilog代码实现,并详细阐述了仿真过程。包括设置信号参数,如a、b、c、d的占空比,以及设置时钟s0和b。在完成设置后,进行了仿真,得到00对应a,10对应c,01对应b,11对应d的运行波形。同时提醒读者注意文件命名规范,确保无中文,并强调软件需正确安装及包含仿真模块。

四选一多路选择器的代码如下,保存路径不能有中文!!

文件名保存为模块名。

(Cyclone III-----EP3C40Q240C8)

编译无错误后:

File-New-VMF

Edit--Insert--

Node Finder

List,全部移入

2536

2536

624

624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?