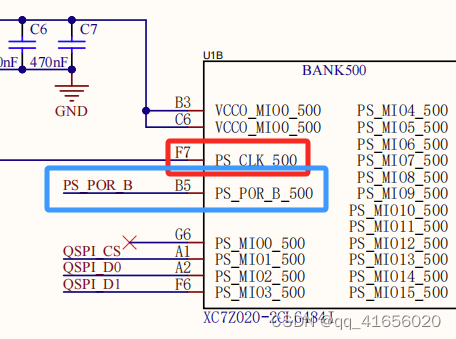

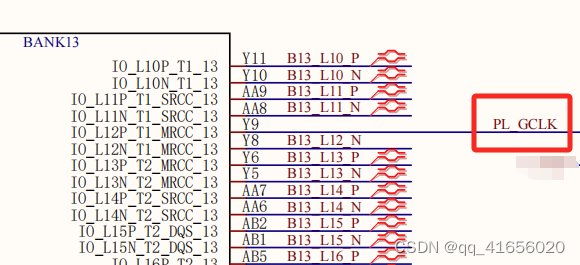

一、时钟、复位引脚

根据Xilinx原理图,搞清楚了PS端和PL端的clk引脚,以及PS端的复位信号(PL端没有设置按键复位)

PS(Processing System):包括bank500、bank501、bank502

PL(Programmable Logic):包括bank13、bank33、bank34、bank35

Xilinx芯片型号:XC7Z020-2CLG484I

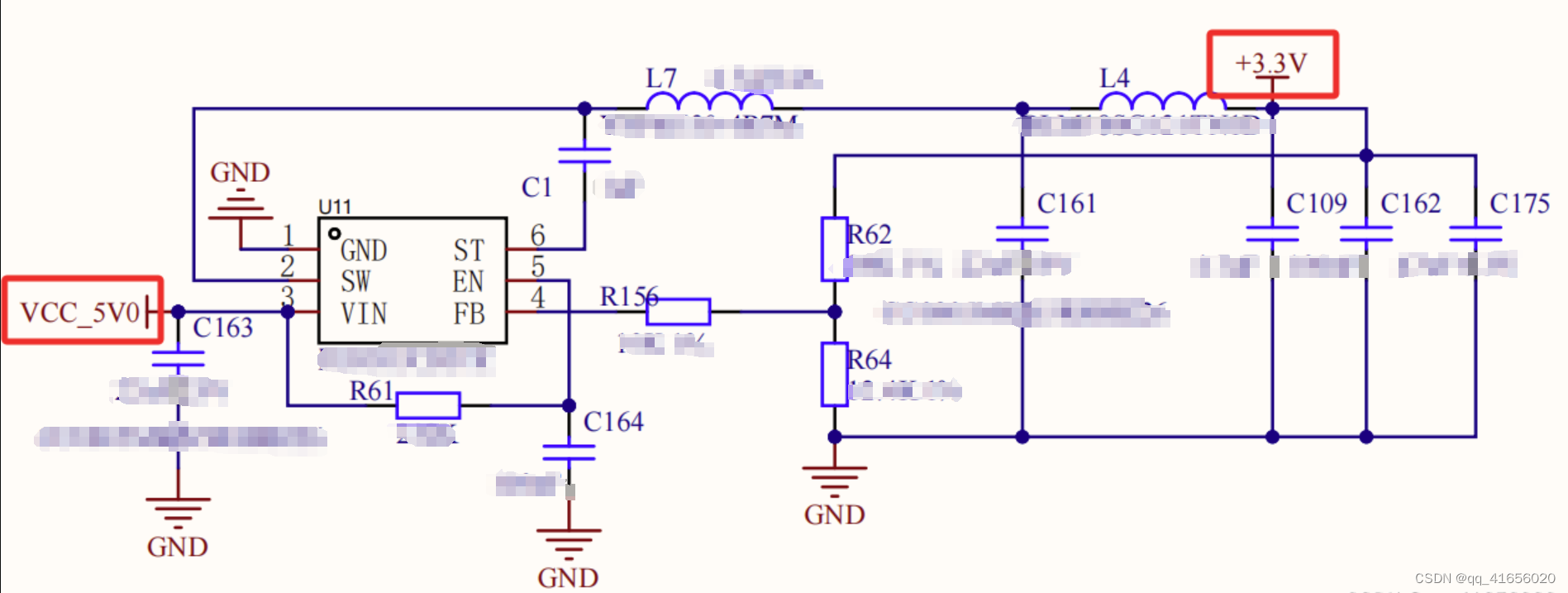

二、供电引脚

在原理图中,1.0V、1.8V、1.5V、3.3V均由VCC_5V0产生,下图为3.3V电压产生的原理图:

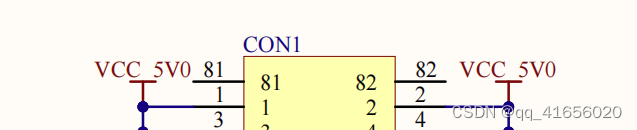

查找VCC_5V0,发现接到连接器上(核心板):

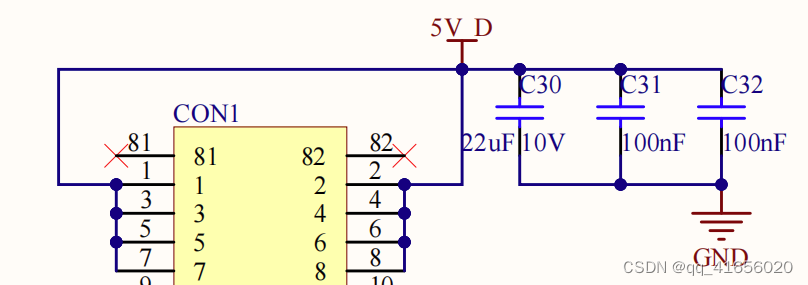

找到对应连接器的对应接线,发现来源于5V_D(底板):

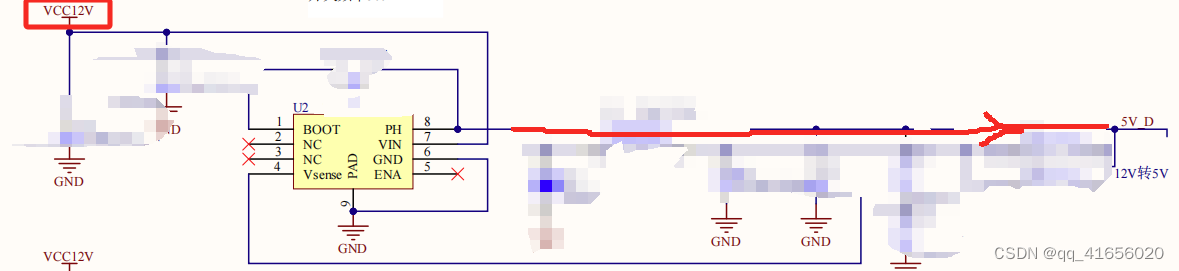

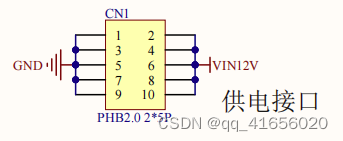

而5V_D是由VCC12V产生的,VCC12V与GND接到2*5PIN的排针上。

因此开发板为12V供电。

本文详细解释了XilinxXC7Z020-2CLG484I芯片中PS和PL部分的时钟和复位引脚,以及供电线路的追踪,从PS的VCC_5V0到核心板再到底板的12V供电过程。

本文详细解释了XilinxXC7Z020-2CLG484I芯片中PS和PL部分的时钟和复位引脚,以及供电线路的追踪,从PS的VCC_5V0到核心板再到底板的12V供电过程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?