转载自http://blog.sina.com.cn/s/blog_7cacaa5e0102v0f9.html

建立时间——寄存器触发沿来临之前,数据保持稳定的时间。

保持时间——寄存器触发沿来临之后,数据保持稳定的时间。

光看定义可能不太清楚,我们就从寄存器的结构来分析所谓的建立时间和保持时间。

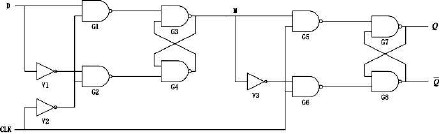

先上图寄存器的建立时间和保持时间详解

寄存器的建立时间和保持时间详解

上图为一种D触发器结构图,下面分析其工作原理。

整个结构划分成左右两部分,每部分4个与非门。其中G3、G4、G7、G8构成了RS锁存器。M为值保持点。

当CLK=0时,G5、G6门的输出为1,Q保持不变;G1、G2门输出~D、D,M值为D。

当CLK=1时,G1、G2门的输出为1,M值保持不变;G5、G6门输出~M、M,Q值为M,从而完成了一次数据锁存。

现假设一个情况,数据信号D要从0变为1,等时钟触发沿来临之后,锁存1这个值。分析:

触发沿来临之前即CLK仍为0时,左半部分的与非门的输出都依赖于数据信号D,即M的值跟随D而变化。M值原来为0,这时D要从0变为1,这个信号经过V1反相器和G1、2、3、4四个与非门的延迟才到达M点,使其变为1。如果在这个延迟时间之前,触发沿变为了1,M值没有发生变化,而Q是依赖于M值的,则Q输出仍然为0。所以,必须等D信号进过了那些门的延迟, M值基于D改变了才能使输出正确,这个延迟就是建立时间。

触发沿来临之后即CLK为1时,CLK会经过V2反相器的延迟变为0,使左半部分进入保持原值的状态。但是在反相器V2的延迟之前,进入G1、G2门的CLK信号仍然为1,这时的左半部分的与非门输出还是依赖于D信号,如果D信号有跳变,M值就会发生变化,从而Q输出也发生变化。所以,D信号得保持稳定直到CLK经过了V2的延迟,输出才不会变化。这个延迟就是保持时间。

注:D触发器的结构多种多样,但是其建立时间和保持时间的分析是一样。

903

903

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?