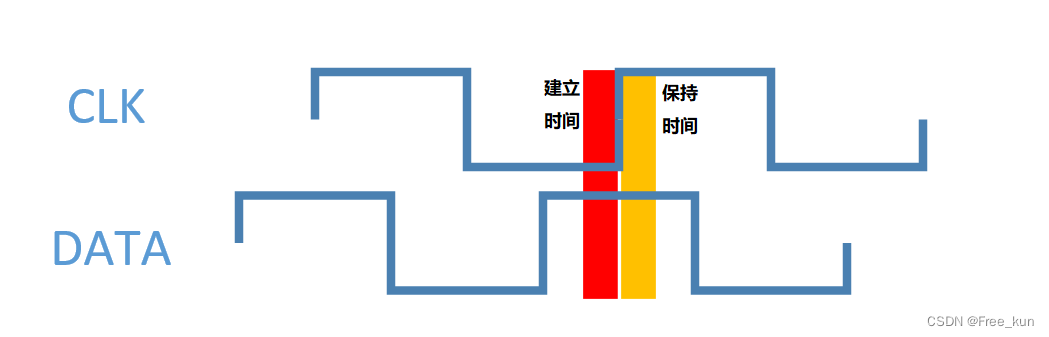

什么是建立时间?什么是保持时间?

建立时间(Tsetup)是指时钟上升沿到来之前数据保持稳定的时间,指明数据需要提前到来;

保持时间(Thold) 是指时钟上升沿到来之后数据保持稳定的时间,指明数据需要稳定一段时间;

相关说明

建立时间与保持时间是时序分析的重要概念,通常采用静态时序分析进行时序违例的查找,即两个寄存器之间为同步时钟。

同步时钟与异步时钟

同步时钟并非是指两个时钟完全相同,而是指两个时钟有确定相位关系;

异步时钟是指两个时钟之间无法确定相位关系;

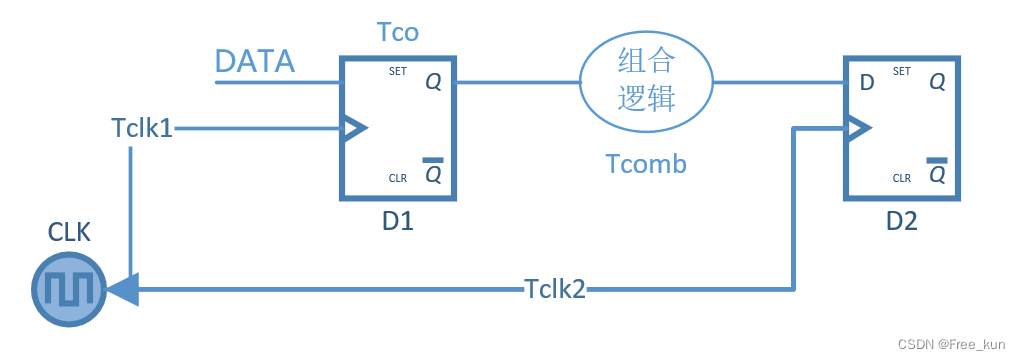

图示说明

D1与D2为两个寄存器,使用同步时钟,从时钟源到达D1的时间为Tclk1,从时钟源到达D2的时间为Tclk2,且Tclk2>Tclk1;

记两个时钟间得偏斜为Tskew = Tclk2 - Tclk1

数据经过D1的D端到达Q端需要经过内部锁存器电路,花费的时间为Tco;

两个寄存器之间通常含有一定的组合逻辑电路,经过该路段花费的时间为Tcomb;

建立时间:

满足建立时间,需要在D2上升沿到来时,D2的数据输入端口已经准备好数据;

数据路径:数据经过一个周期(可看作两拍,一个上升沿到另一个上升沿),经过了Tco时间,再经过组合逻辑的时间Tcomb,才到达D2的输入端,共花费Tco+Tcomb;

时钟路径:D2的时钟比D1慢Tskew(Tclk2-Tclk1),因此一个周期中,D2上升沿到来的时间为(T+ Tskew)

以上可知,数据路径花费的时间一定要比时钟路径花费的时间少,至少少一个建立时间Tsetup,可满足建立时间,表达式如下:

需要注意的是,这里是两拍与周期相关,并且这个周期包含了时钟的抖动(Jitter)

Jitter指不同周期时间长短变化,例如周期1Hz的时钟,可能在某个周期内为1.001s,可能另一个周期内为0.9999s。

解决方法:

1.增加周期(即降低频率)

2.优化组合逻辑,降低Tcomb

3.增加Tskew(布局布线)

保持时间:

满足保持时间,需要在D2上升沿到来后,D2的数据依然能挺一个保持时间,防止下一个数据刷新D2的数据输入端口;

下一个数据到来的时间是:Tco+TcombD2端口数据会在D2端口上升沿到来时刷新,上升沿刷新即为两个时钟之间的偏移Tskew

以上可知,下一个数据到来需要花费的时间一定要比上升沿刷新花费的时间至少多一个保持时间,即:

需要注意的是,这里是在一个周期内发生的事情,所以与频率无关

解决方法:

1.增加周期(即降低频率)

2.优化组合逻辑,降低Tcomb

3.减小Tskew(布局布线)

6508

6508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?