第七章 中规模通用集成电路及其应用

大纲:

- 常用电路:二进制并行加法器、译码器、编码器、多路选择器、电路分配器、双时针4位二进制同步可逆计数器74193及转换成模小于16的计数器(书上例题)、集成定时器555的三个应用多谐振荡器

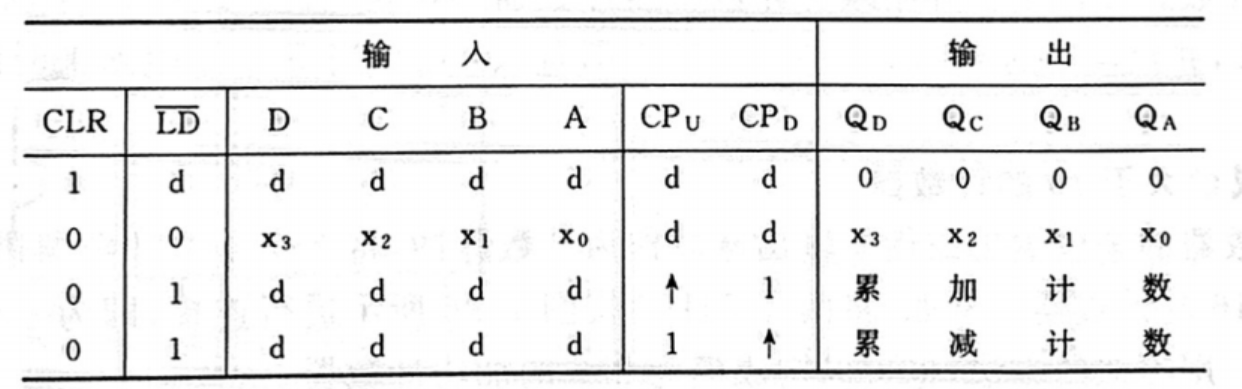

(中规模时序电路只考74193 注意:1.异步清零 存储 暂态过渡 D是高位 2.其他转换 任意进制的计数器)

(组合逻辑中规模:加法器(超前进位 全加器串行 ) 74138译码器 带优先级的编码器74142? 数据选择器 数据分配器 要注意主线:函数发生器)

三个 35电路??

中规模组合逻辑电路

加法器

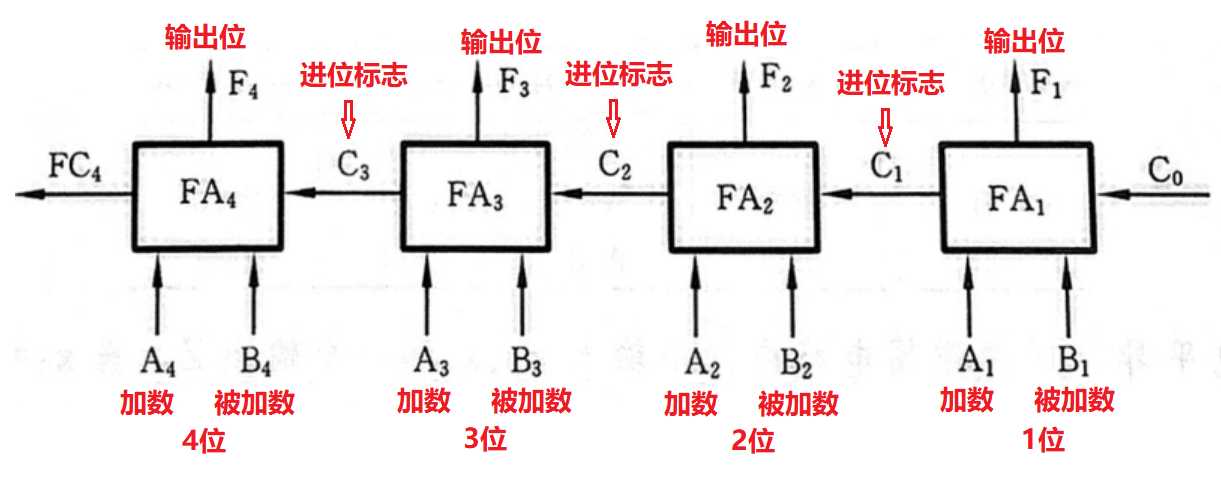

串行进位二进制并行加法器

考虑二位加法

0

1

⟶

1

0

0\space1\longrightarrow1\space0

0 1⟶1 0

在这个过程中,个位向十位发送了“进1”的信号,由此十位进了1,这就是串行加法的原理

超前进位二进制并行加法器

在串行加法器中,4位的计算必须等3位的进位标志才能计算,而3位的又需要2位,2位要等1位,这样非常慢,所以考虑涉及一个能四个位并行计算的加法器。

设计这种加法器的思想是把每一位的加法全展开然后化简,首先先列出第

i

i

i 位的加法表达式

C

i

=

A

i

‾

B

i

C

i

−

1

+

A

i

B

i

‾

C

i

−

1

+

A

i

B

i

C

i

−

1

‾

+

A

i

B

i

C

i

−

1

=

(

A

i

⊕

B

i

)

C

i

−

1

+

A

i

B

i

\begin{aligned} & C_i=\overline{A_i} B_i C_{i-1}+A_i \overline{B_i} C_{i-1}+A_i B_i \overline{C_{i-1}}+A_i B_i C_{i-1} \\ & =\left(A_i \oplus B_i\right) C_{i-1}+A_i B_i \end{aligned}

Ci=AiBiCi−1+AiBiCi−1+AiBiCi−1+AiBiCi−1=(Ai⊕Bi)Ci−1+AiBi

这个表达式分别列举了四种情况,考虑了加数和被加数在有无进位标志下,输出函数的值,在化简合并后,把这两部分拆成进位产生函数和进位传递函数

A

i

⊕

B

i

→

P

i

(进位传递函数)

A

i

B

i

→

G

i

(进位产生函数)

\begin{array}{ll} \mathrm{A}_{\mathrm{i}} \oplus \mathrm{B}_{\mathrm{i}} \rightarrow \mathrm{P}_{\mathrm{i}} & \text { (进位传递函数) } \\ \mathrm{A}_{\mathrm{i}} \mathrm{B}_{\mathrm{i}} \rightarrow \mathrm{G}_{\mathrm{i}} & \text { (进位产生函数) } \end{array}

Ai⊕Bi→PiAiBi→Gi (进位传递函数) (进位产生函数)

于是

C

i

=

P

i

C

i

−

1

+

G

i

C_i=P_i C_{i-1}+G_i

Ci=PiCi−1+Gi

考虑4位并行运算,则可以列出四位的输出函数表达式

C

1

=

P

1

C

0

+

G

1

C

2

=

P

2

C

1

+

G

2

=

P

2

P

1

C

0

+

P

2

G

1

+

G

2

C

3

=

P

3

C

2

+

G

3

=

P

3

P

2

P

1

C

0

+

P

3

P

2

G

1

+

P

3

G

2

+

G

3

C

4

=

P

4

C

3

+

G

4

=

P

4

P

3

P

2

P

1

C

0

+

P

4

P

3

P

2

G

1

+

P

4

P

3

G

2

+

P

4

G

3

+

G

4

\begin{aligned} & \mathrm{C}_1=\mathrm{P}_1 \mathrm{C}_0+\mathrm{G}_1 \\ & \mathrm{C}_2=\mathrm{P}_2 \mathrm{C}_1+\mathrm{G}_2=\mathrm{P}_2 \mathrm{P}_1 \mathrm{C}_0+\mathrm{P}_2 \mathrm{G}_1+\mathrm{G}_2 \\ & \mathrm{C}_3=\mathrm{P}_3 \mathrm{C}_2+\mathrm{G}_3=\mathrm{P}_3 \mathrm{P}_2 \mathrm{P}_1 \mathrm{C}_0+\mathrm{P}_3 \mathrm{P}_2 \mathrm{G}_1+\mathrm{P}_3 \mathrm{G}_2+\mathrm{G}_3 \\ & \mathrm{C}_4=\mathrm{P}_4 \mathrm{C}_3+\mathrm{G}_4=\mathrm{P}_4 \mathrm{P}_3 \mathrm{P}_2 \mathrm{P}_1 \mathrm{C}_0+\mathrm{P}_4 \mathrm{P}_3 \mathrm{P}_2 \mathrm{G}_1+\mathrm{P}_4 \mathrm{P}_3 \mathrm{G}_2+\mathrm{P}_4 \mathrm{G}_3+\mathrm{G}_4 \end{aligned}

C1=P1C0+G1C2=P2C1+G2=P2P1C0+P2G1+G2C3=P3C2+G3=P3P2P1C0+P3P2G1+P3G2+G3C4=P4C3+G4=P4P3P2P1C0+P4P3P2G1+P4P3G2+P4G3+G4

将其全部展开,会发现虽然说

C

4

\mathrm{C_4}

C4 虽然由

C

3

\mathrm{C_3}

C3 得出,但因为

C

3

\mathrm{C_3}

C3 是可展开的,同时

C

2

\mathrm{C_2}

C2 和

C

1

\mathrm{C_1}

C1 也是可展开的,也就是说,只需要知道

A

i

,

B

i

,

C

0

\mathrm{A_i,B_i,C_0}

Ai,Bi,C0 就能一次性把四位全部算出来,我觉得这是一种进步

但其实说了那么多并没有什么卵用,我只是那么一说,考试不会让你列数学原理的。

芯片改造

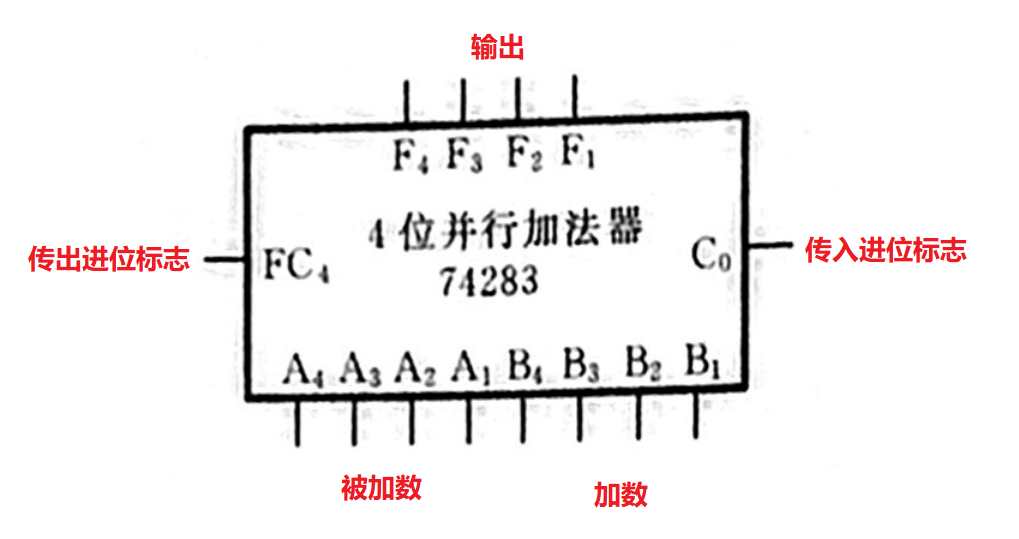

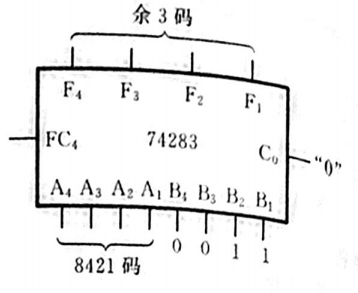

最常用的4位并行加法器是74283芯片

加法器一般规范 A \mathrm{A} A 为被加数, B \mathrm{B} B 为加数, F \mathrm{F} F 为输出

【例】设计一个8421码转余3码的代码转换电路

【解】余3码是由8421码加3形成的代码,所以直接在被加数里面加“0011” 就完事了

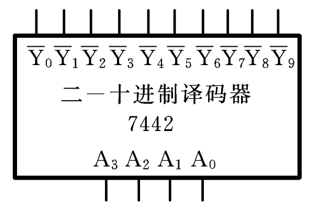

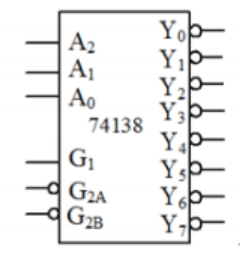

译码器

译码器是一个能将 n n n 个输入变量变换成 2 n 2^n 2n 个变量的多输出组合电路,比如实现 ( 110 ) 2 ⟶ ( 6 ) 10 (110)_2\longrightarrow(6)_{10} (110)2⟶(6)10 的译码器长这样

其中A为输入端,Y为输出端,比如输入 ( 0100 ) (0100) (0100) 会输出 ( 000001000 ) (000 001 000) (000001000) 代表6

上面的译码器只是为了引入这个概念,了解了解就行,考试不考,考试考的是74138芯片,

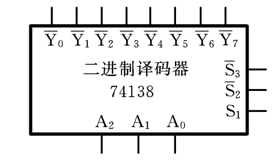

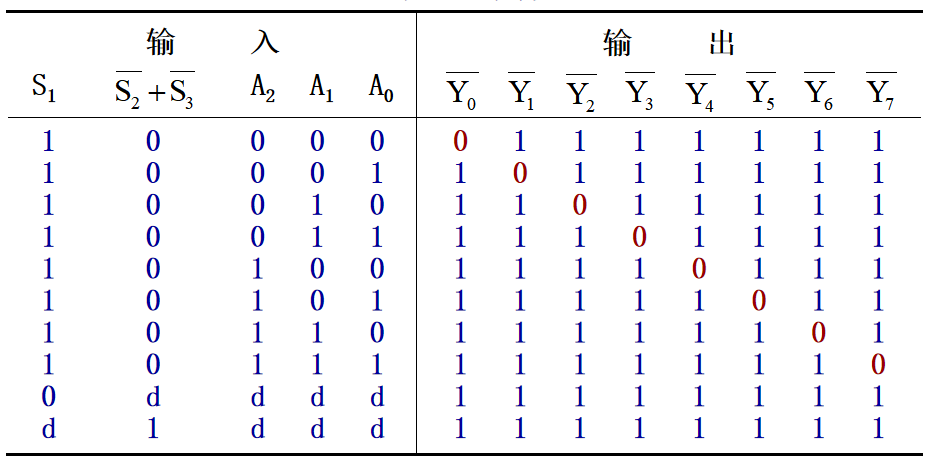

74138型3-8线译码器有三个使能端,分别是G1、G2A和G2B。这三个使能端的作用是控制译码器的工作状态。当这三个使能端的电平满足特定条件时,译码器才会工作。

- S1(使能端1):这是一个高电平有效的使能端。也就是说,当G1为高电平(1)时,译码器才会工作。如果G1为低电平(0),则译码器不工作。

- S2和S3(使能端2和3):这两个使能端都是低电平有效。也就是说,当S2和S3都为低电平(0)时,译码器才会工作。如果S2或S3中任何一个为高电平(1),则译码器不工作。

通过给使能端通电可以自由的开关译码器

芯片改造

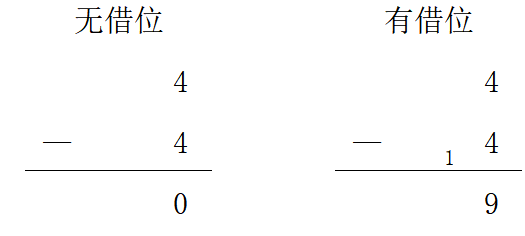

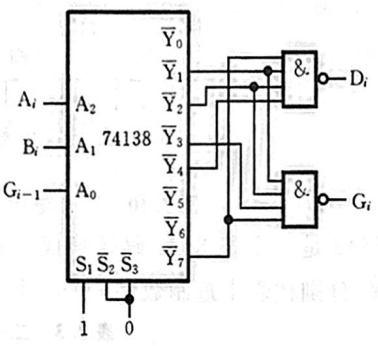

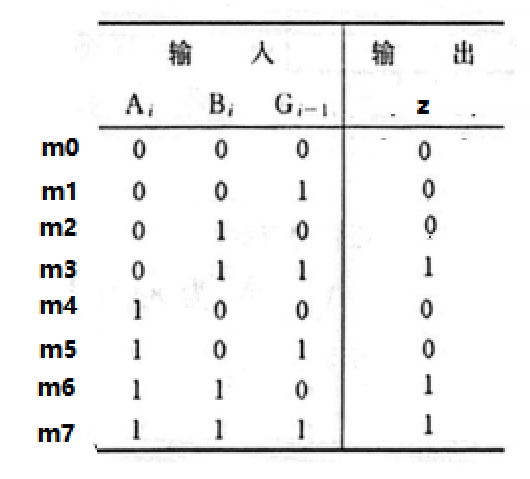

【例】使用74138和与非门实现全减器

【解】要解本题,思路跟加法是一样的,减法是本质全减器是处理某一位的结果,然后再拼在一起(串行or并行),但本题重点不是让你怎么拼,而是问你怎么设计某一位的全减器

首先我们要理解某一位减法是怎么实现的,先从十进制开始说,假设你在计算这个式子:

如果数不够减,那就要借位,所以如果要计算某一位的减法,你至少需要三个东西:被减数A,减数B,是否被借位,刚好74138就是3位输入

同时我们要处理输出,原式的输出是8位,结果(二进制下的输入的值)是多少,对应位的值就是0,那我们得到的结果肯定不能是这个,我们期望的结果应该是两个,一个是结果 D \mathrm{D} D 一个是是否要借上一位 G i \mathrm{G_i} Gi ,在不知道怎么画电路的时候可以先写出真值表

根据真值表可以写出

D

i

,

G

i

\mathrm{D_i,G_i}

Di,Gi 的表达式,然后根据与非门的要求进行转换

D

i

(

A

i

,

B

i

,

G

i

−

1

)

=

m

1

+

m

2

+

m

4

+

m

7

=

m

‾

1

⋅

m

‾

2

⋅

m

‾

4

⋅

m

‾

7

‾

G

i

(

A

i

,

B

i

,

G

i

−

1

)

=

m

1

+

m

2

+

m

3

+

m

7

=

m

‾

1

⋅

m

‾

2

⋅

m

‾

3

⋅

m

‾

7

‾

\begin{aligned} & D_i\left(A_i, B_i, G_{i-1}\right)=\mathrm{m}_1+\mathrm{m}_2+\mathrm{m}_4+\mathrm{m}_7=\overline{\overline{\mathrm{m}}_1 \cdot \overline{\mathrm{m}}_2 \cdot \overline{\mathrm{m}}_4 \cdot \overline{\mathrm{m}}_7} \\ & \mathrm{G}_i\left(\mathrm{~A}_i, \mathrm{~B}_i, \mathrm{G}_{i-1}\right)=\mathrm{m}_1+\mathrm{m}_2+\mathrm{m}_3+\mathrm{m}_7=\overline{\overline{\mathrm{m}}_1 \cdot \overline{\mathrm{m}}_2 \cdot \overline{\mathrm{m}}_3 \cdot \overline{\mathrm{m}}_7} \end{aligned}

Di(Ai,Bi,Gi−1)=m1+m2+m4+m7=m1⋅m2⋅m4⋅m7Gi( Ai, Bi,Gi−1)=m1+m2+m3+m7=m1⋅m2⋅m3⋅m7

由于74138的输出天然带“非门”,所以只需要把它们穿在一起穿一个与非门就行了

编码器

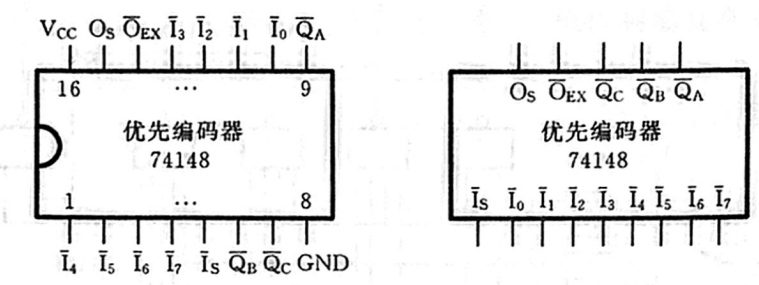

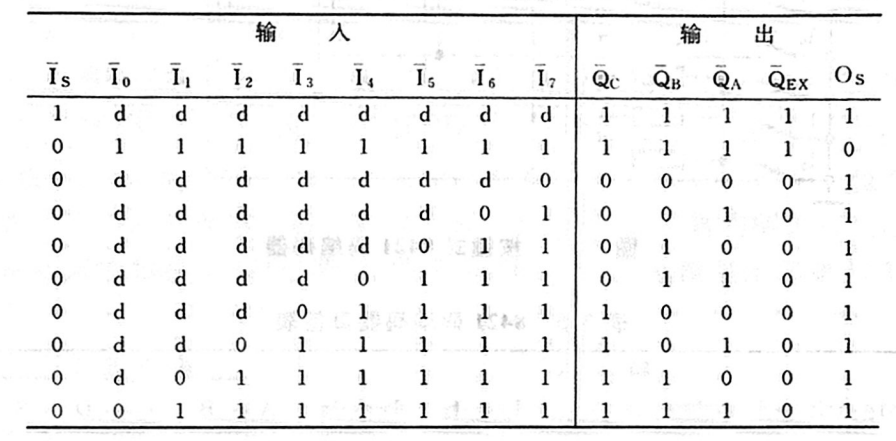

编码器就是译码器反过来,多变1,这里不再给出示例,但介绍一个新东西:优先编码器74148

让我们来详细认识一下这个编码器: I s ‾ \mathrm{\overline{I_s}} Is 是一个选通输入,当他置1时代表整个编码器无效(其实就是开关),所谓优先,意思就是数字越大的越优先,即在 I 0 ‾ − I 7 ‾ \mathrm{\overline{I_0} -\overline{I_7}} I0−I7 中, I 7 ‾ \overline{I_7} I7 的优先级最高,谁先置0,输出结果就是什么,例如,当 I 5 ‾ = 0 \mathrm{\overline{I_5}} =0 I5=0 而其他都为1时,结果是 010 010 010 ,注意这里输出的不是 I \mathrm{I} I 的下标5,而是优先级3

【例】输出为 Y ˉ 2 , Y ˉ 1 , Y ˉ 0 \bar{Y}_2, \bar{Y}_1, \bar{Y}_0 Yˉ2,Yˉ1,Yˉ0 。当使能输入 S ˉ = 0 \bar{S}=0 Sˉ=0, 编入为 I ˉ 1 = I ˉ 5 = I ˉ 6 = 0 \bar{I}_1=\bar{I}_5=\bar{I}_6=0 Iˉ1=Iˉ5=Iˉ6=0, 其余编码输入全为 1 时, 则输出 Y ˉ 2 Y ˉ 1 Y ˉ 0 \bar{Y}_2 \bar{Y}_1 \bar{Y}_0 Yˉ2Yˉ1Yˉ0 应为?

【解】 I ˉ 6 = 0 , I ˉ 6 \bar{I}_6=0, \bar{I}_6 Iˉ6=0,Iˉ6 的优先级最高, ∴ Y 2 ‾ Y ˉ 1 Y 0 ‾ = 001 \therefore \overline{Y_2} \bar{Y}_1 \overline{Y_0}=001 ∴Y2Yˉ1Y0=001

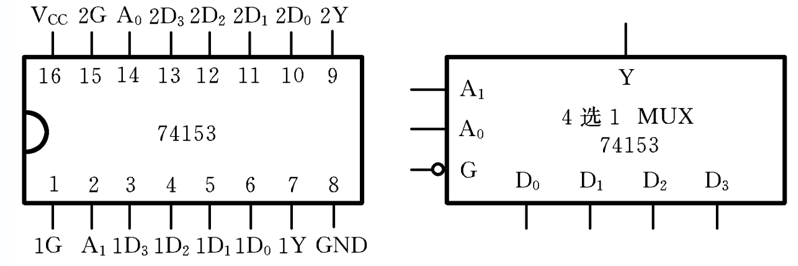

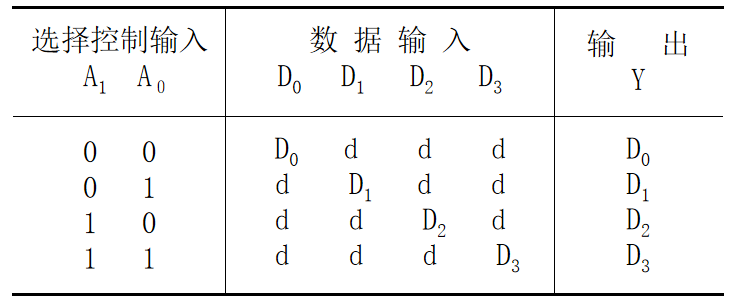

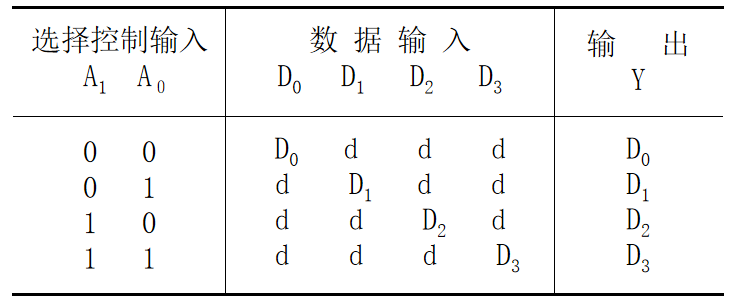

多路选择器

选择器就是,你输入了一些数据 D \mathrm{D} D 然后你告诉我哪一个( A \mathrm{A} A)要输出,我就输出哪一个

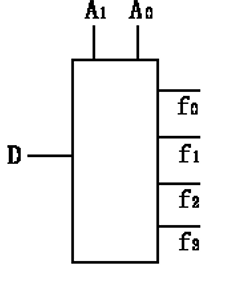

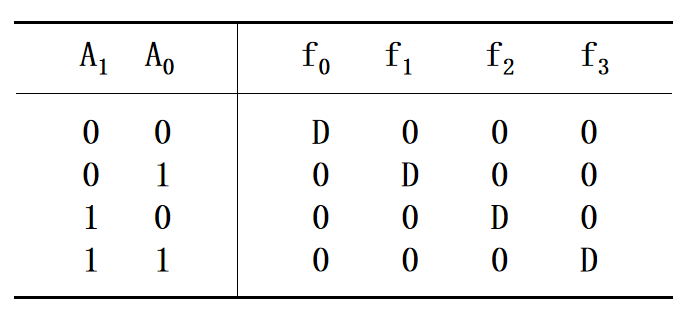

多路分配器

分配器就是,你输入一个数据 D \mathrm{D} D 然后你告诉我你要分给谁( A \mathrm{A} A)我就分给谁( f \mathrm{f} f)

中规模时序逻辑电路

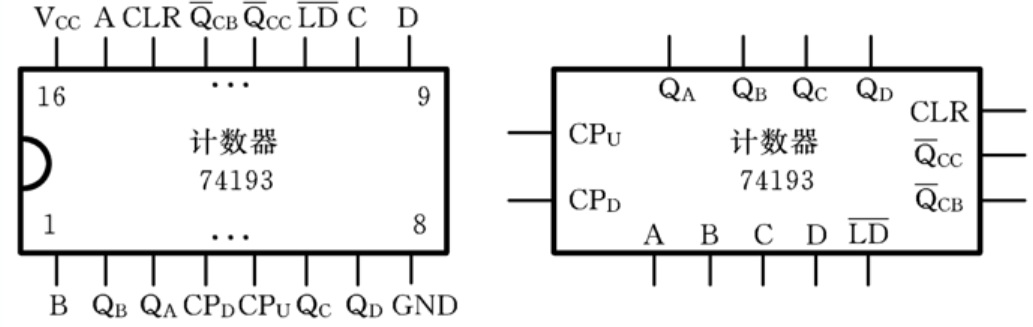

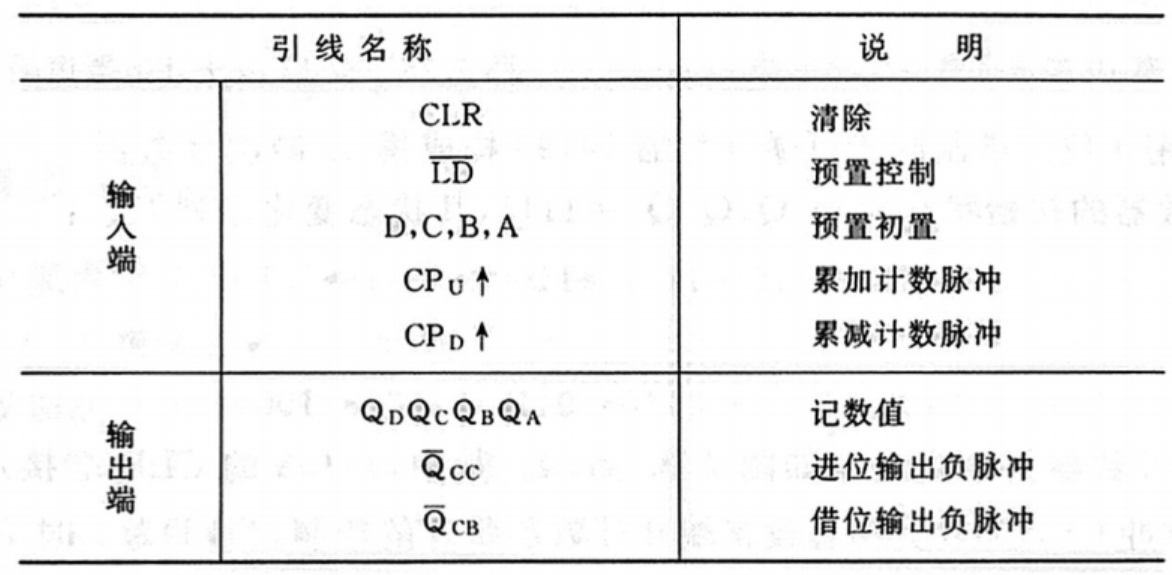

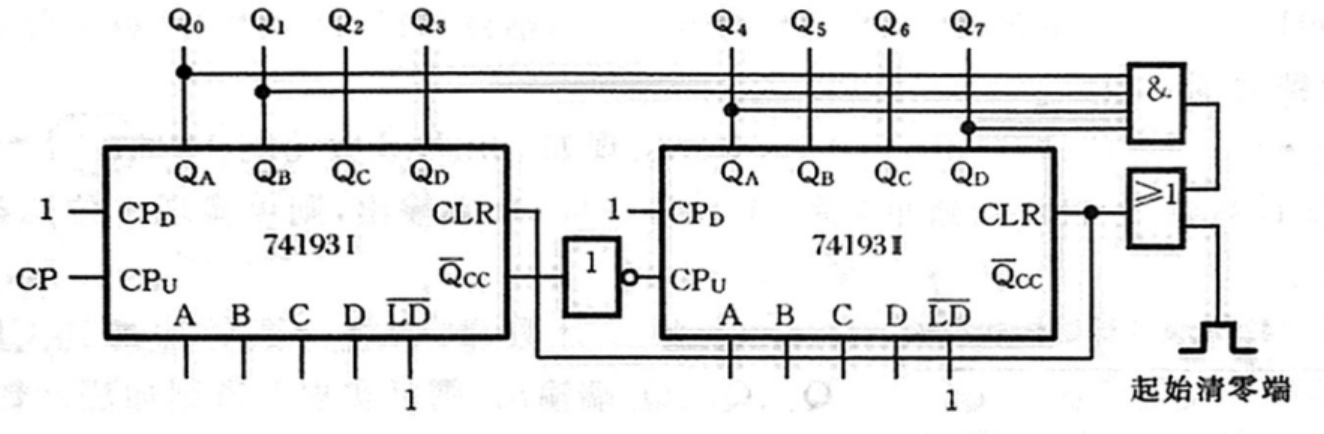

数字系统中最典型的时序逻辑电路是计数器和寄存器。这些在第四第五章都有设计,这里我们只讲一个74193芯片

74193芯片是一个异步清零的同步计数器

异步清零(Asynchronous Clear)是一种电子电路的功能,特别是在数字逻辑电路和计数器中。在SN74LS193这种四位二进制可逆计数器中,异步清零功能允许用户在任何时候立即将计数器的输出清零,而不需要等待下一个时钟脉冲。

这个功能被称为“异步”,是因为它不需要与时钟信号同步。只要清零输入被激活(在SN74LS193中,这是通过将CLEAR输入拉低来实现的),计数器的输出就会立即清零,无论时钟信号的状态如何。

当 C L R \mathrm{CLR} CLR 置为1时,不管发生什么,直接清零, L D ˉ \mathrm{\bar{LD}} LDˉ 置0表示要预设值,此时会把ABCD输入的值作为内部存储的值,置1表示要进行计数,此时如果 C P D \mathrm{CP_D} CPD 置1表示累加计数,此时如果往 C P D \mathrm{CP_D} CPD 输入一个脉冲,内部就会进行一次累加,累减同理

74193转其他模的计数器

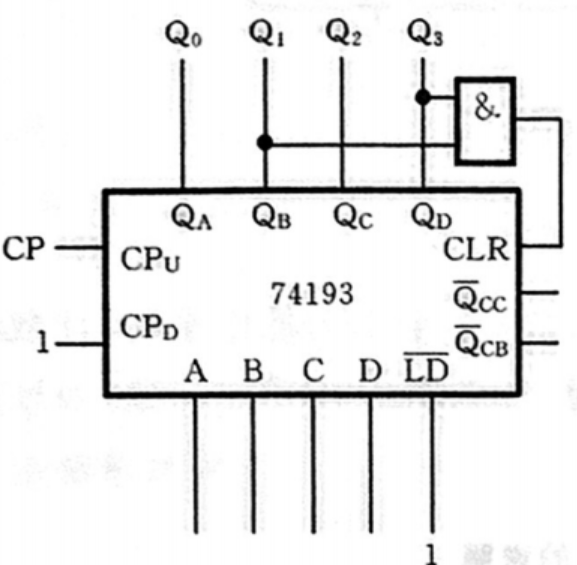

构成模10加法计数器

首先我们要明确初值和最大值是多少。初值可以设置为 0000 0000 0000 ,对于模10来说,最多能有0—9 ,10个数,因此在 1001 1001 1001的时候,如果再进1,会变成 1010 1010 1010 ,此时要直接调用CLR归零,实现方法是用一个与门接到 $\mathrm{Q_B,Q_D} $ 上

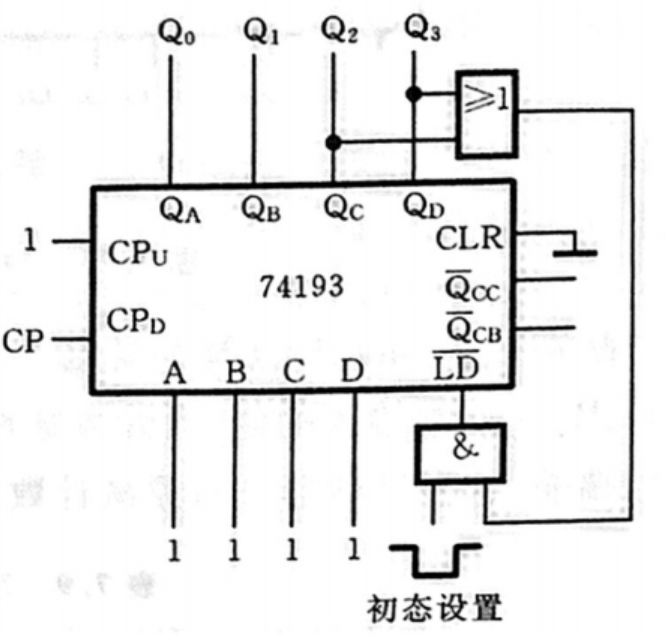

构成模12减法计数器

如果是减法,则永远不需要归零,所以CLR接地,可以自己选一个大于12的初值,这里可以选择 1111 1111 1111 作为初值,如果减到了“0”,说明如过到了 0100 0100 0100 再减一,到了 0011 0011 0011 这时候必然在前两位均为0,因此可以用 Q C , Q D \mathrm{Q_C,Q_D} QC,QD 接一个与门跟初始脉冲接个与门连 L D ‾ \mathrm{\overline{LD}} LD 上,初始脉冲就是有一个低电平的脉冲,因为 L D ‾ \mathrm{\overline{LD}} LD 为0时代表设初值

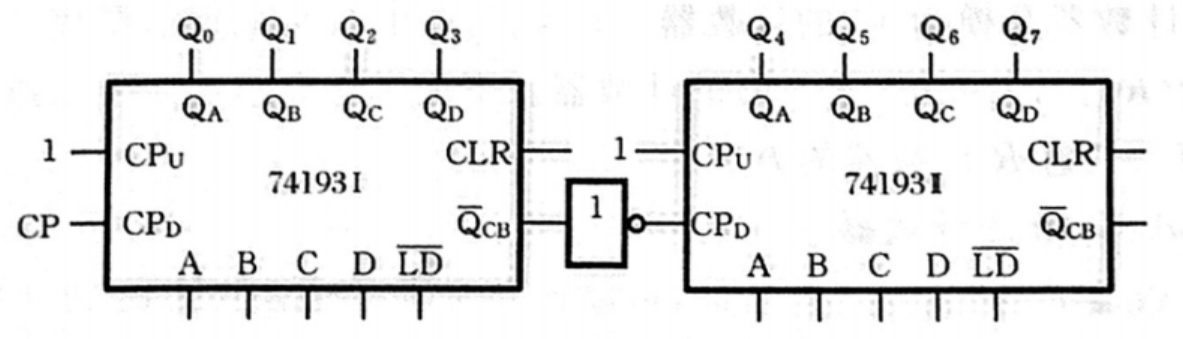

构成模256的加法计数器

256刚好是16的两倍,可以用两个计数器实现,当计数器(1)满16时,计数器(2)进一,实现方法是用一个非门接输出的 Q ‾ C B \overline{\mathrm{Q}}_{\mathrm{CB}} QCB 上,当进一时会发出一个向上的脉冲,刚好传给 C P D \mathrm{CP_D} CPD

构成模147的计数器

同样适用两个计数器实现,方法同"构成模12减法计数器" ,我们要确定到底是什么状态的时候满147然后归零,因此要写出147的二进制

(

147

)

10

=

(

10010011

)

2

(147)_{10}=(10010011)_2

(147)10=(10010011)2

然后只需要判断对应位上同时为1即可,用与门实现

知识迁移

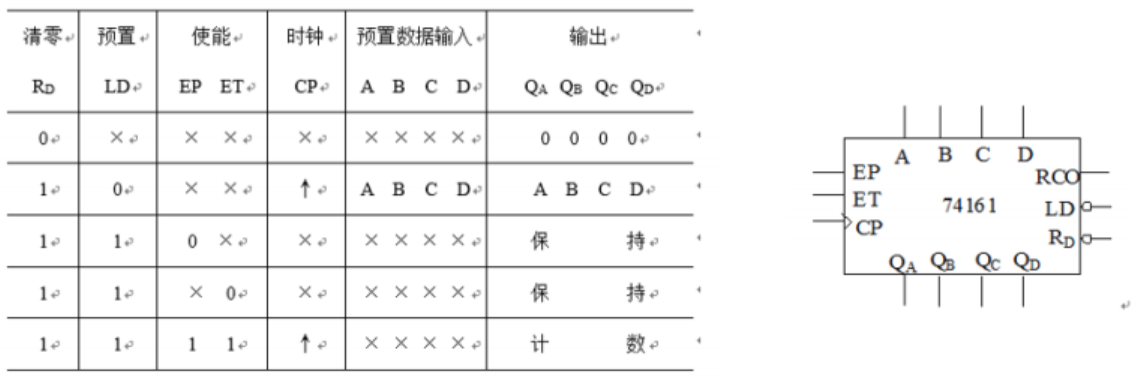

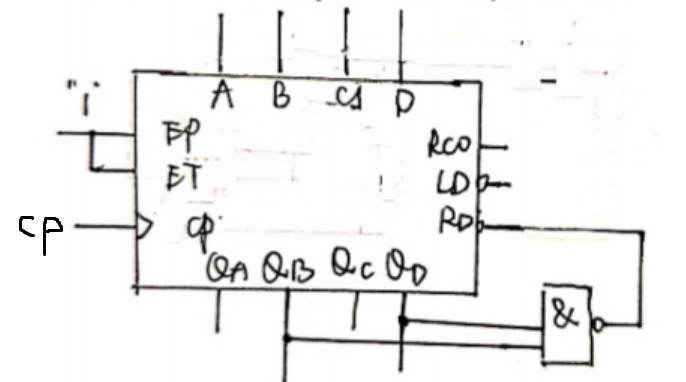

考试还真不一定会给你一块74193芯片,他可能会给你一块新的芯片,再告诉你他的功能,让你设计,其实道理是一样的

【例】试用四位二进制加计数器74161构成十进制计数器,用反馈清零法。

先分析这块板,累加结果是 Q \mathrm{Q} Q 用 A B C D \mathrm{ABCD} ABCD 设置初值,但本题不需要设置初值,所以不用管,然后来看使能端,我们需要用到的是计数功能和清零功能,而清零功能对使能端没有要求,所以直接通一个恒1的信号就行,再来看时钟是上边沿触发,所以给一个正常的CP信号就行,最后看怎么清零

初始是 0000 0000 0000 最大值是1001(9),一旦到了1010(10) 就要归0,所以在 Q A , Q C \mathrm{Q_A,Q_C} QA,QC 加一个与门,一旦这个成立了就给 R D \mathrm{R_D} RD 置零,一开始恒1,要给他置0,那就拿个非门,最终用与非门来完成这个需求

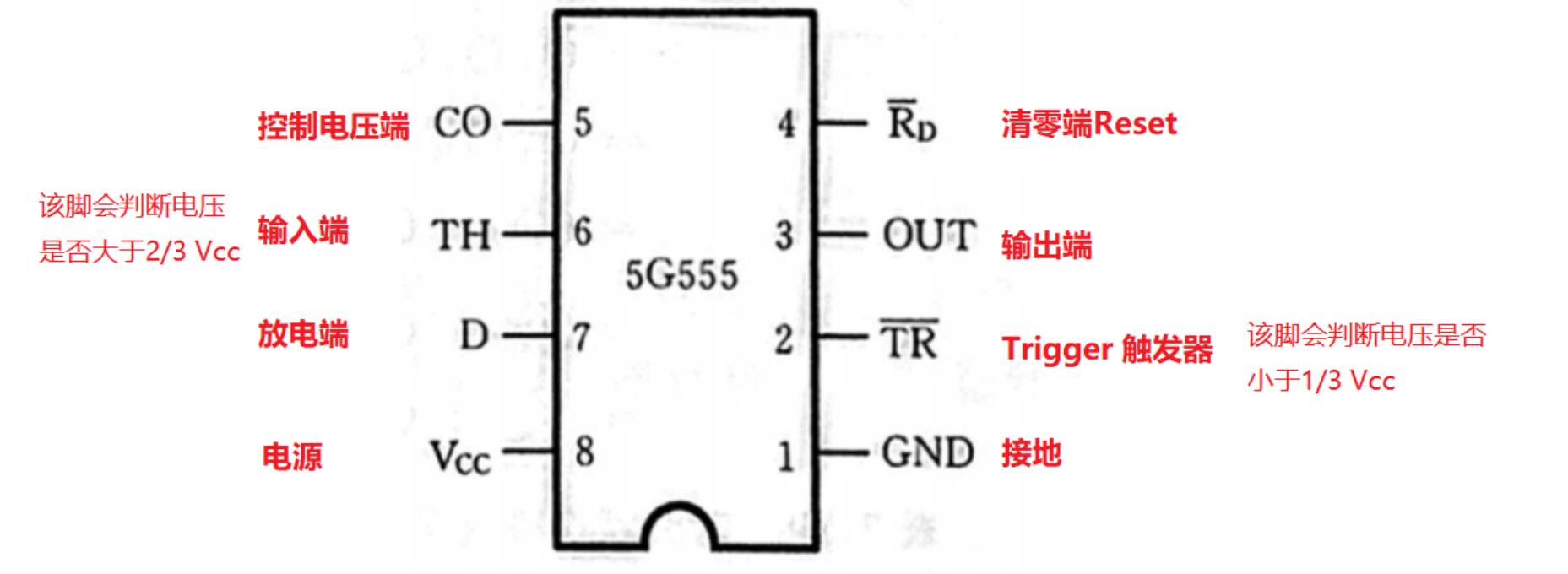

中规模信号产生与变换电路

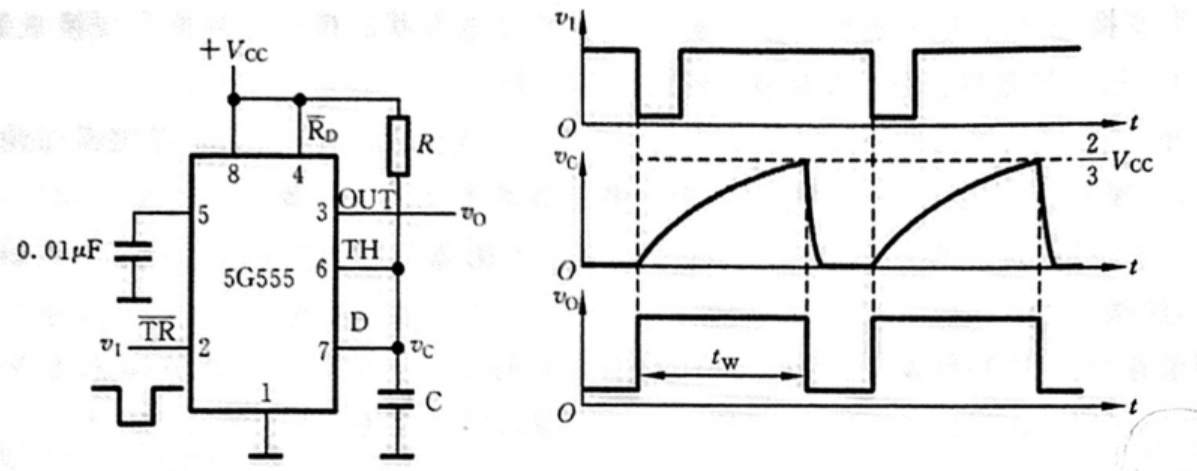

本篇只介绍5G555集成定时器

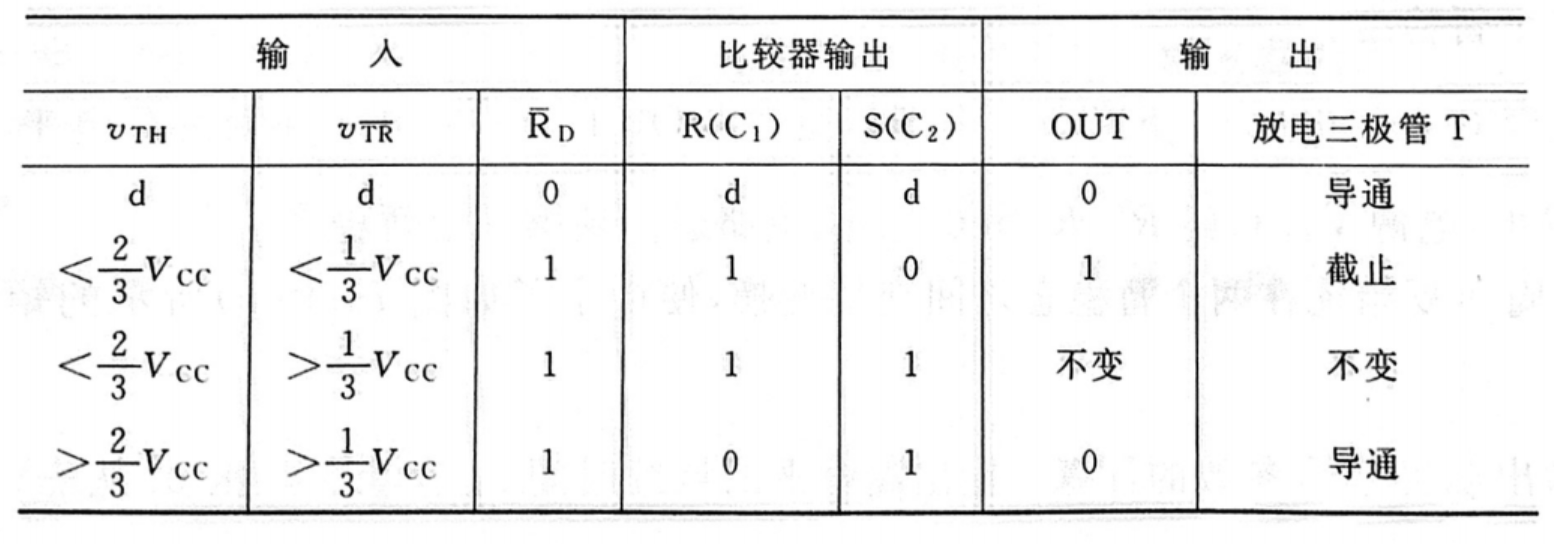

如果不想了解具体的工作原理,只需要知道以下几点即可:

- 1脚接地,8脚接电源,4脚大部分情况下也接电源

- 5脚通过一个0.01μF电容接地,也可以悬空(不建议)

- 2、6、7脚根据不同应用有不同接法

- 3脚是输出

想到一个记忆技巧,"D"是电,所以是放电端(雾)

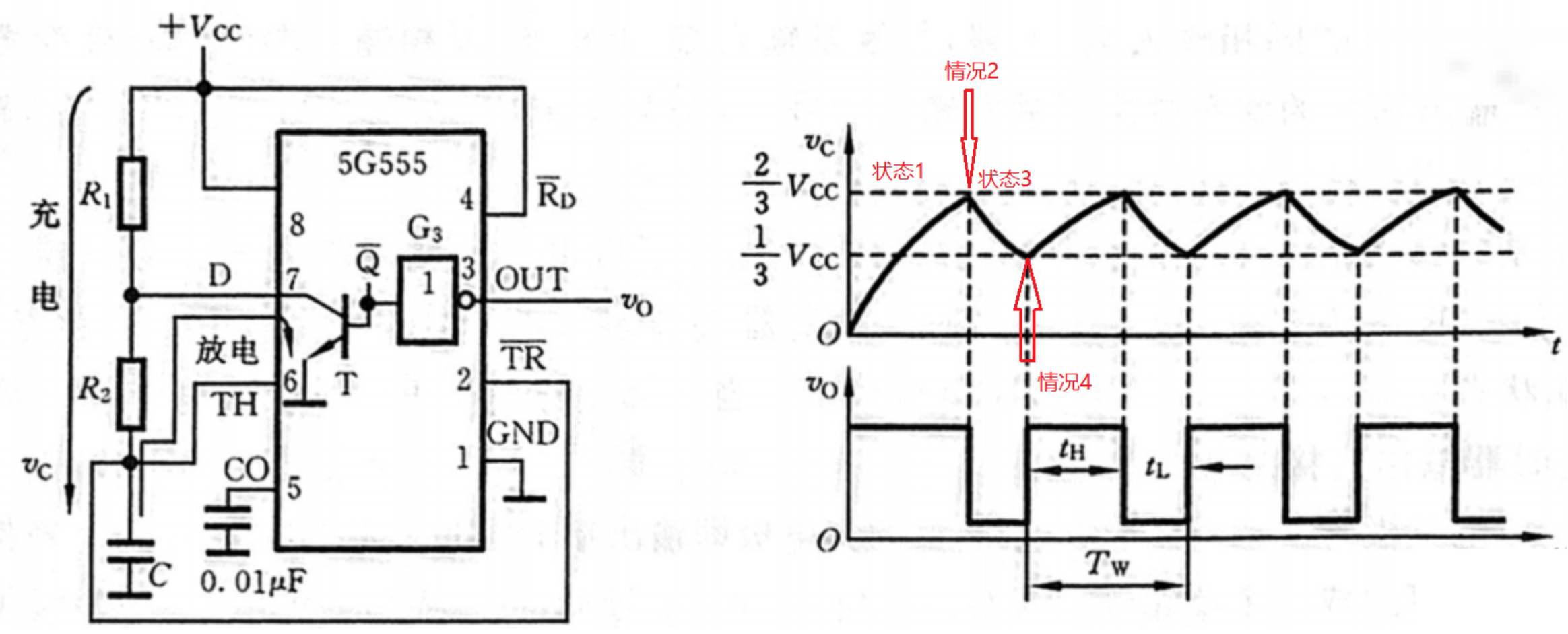

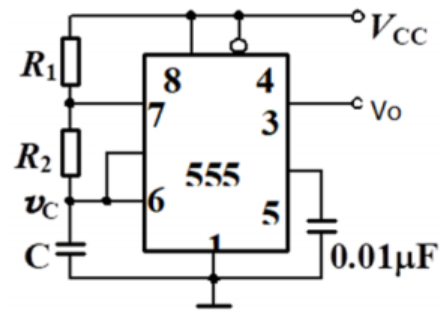

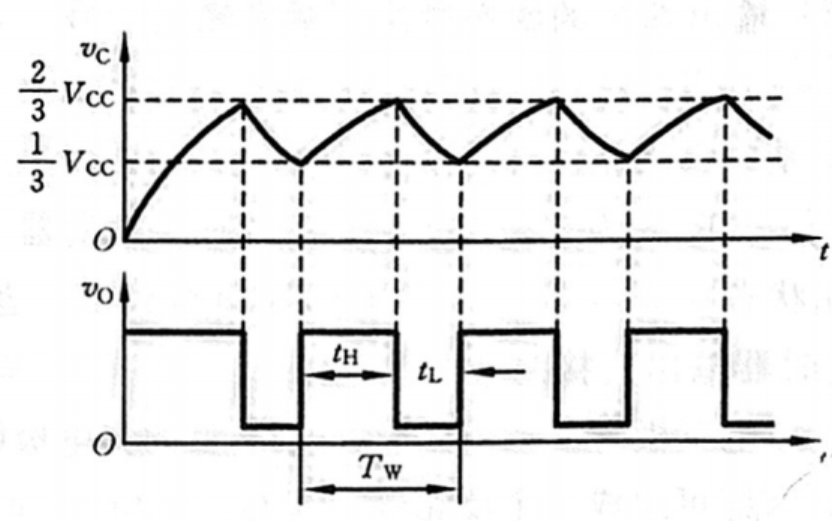

应用1 多谐振荡器

所谓的“稳态”指的是3脚输出端的电平高低是否稳定。“无稳态”的意思是,3脚的输出会自动在高低之间变换,而不会稳定地停留在高或低上。这就形成了一个振荡器。这个特性可以用来制作LED的闪烁效果、电子琴等,也可以用于PWM技术控制电动机的转速等。

这个电路的工作原理如下:

- 接通电源瞬间,因为电容不能突变,所以 T H ‾ \mathrm{\overline{TH}} TH 电压小于 2 3 V C C \frac{2}{3}V_{CC} 32VCC , T R ‾ \mathrm{\overline{TR}} TR 电压小于 1 3 V C C \frac{1}{3}V_{CC} 31VCC ,对比功能表,$\mathrm{OUT} $ 为1

- 电容电压升高到 2 3 V C C \frac{2}{3}V_{CC} 32VCC 时, T H ‾ \mathrm{\overline{TH}} TH 和 T R ‾ \mathrm{\overline{TR}} TR 电压为 2 3 V C C \frac{2}{3}V_{CC} 32VCC ,对比功能表,$\mathrm{OUT} $ 为0

- $\mathrm{OUT} $ 为0后,放电三极管导通,电容开始放电

- 电容电压下降到 1 3 V C C \frac{1}{3}V_{CC} 31VCC 时,恰好又符合 T H ‾ \mathrm{\overline{TH}} TH 电压小于 2 3 V C C \frac{2}{3}V_{CC} 32VCC , T R ‾ \mathrm{\overline{TR}} TR 电压小于 1 3 V C C \frac{1}{3}V_{CC} 31VCC ,对比功能表,$\mathrm{OUT} $ 为1

- 于是开始2-4循环

因此我们可以得出以下公式:

- 充电时间 t H = 0.7 ⋅ ( R 1 + R 2 ) ⋅ C 1 t_H=0.7 \cdot (R_1+R_2 ) \cdot C_1 tH=0.7⋅(R1+R2)⋅C1

- 放电时间 L 2 = 0.7 ⋅ R 2 ⋅ C 1 L_2=0.7 \cdot R_2 \cdot C_1 L2=0.7⋅R2⋅C1

- 周期 T w = t 1 + t 2 = 0.7 ⋅ ( R 1 + 2 R 2 ) ⋅ C 1 T_w=t_1+t_2=0.7 \cdot\left(R_1+2R_2\right) \cdot C_1 Tw=t1+t2=0.7⋅(R1+2R2)⋅C1

- 频率 f = 1 T = 1.43 ( R 1 + 2 R 2 ) ⋅ C 1 f=\frac{1}{T}=\frac{1.43}{\left(R_1+2R_2\right) \cdot C_1} f=T1=(R1+2R2)⋅C11.43

- 占空比 t 1 T = R 1 + R 2 R 1 + 2 R 2 \frac{t_1}{T}=\frac{R_1+R_2}{R_1+2R_2} Tt1=R1+2R2R1+R2

【例】分析下图电路,画出Vc、Vo 电压波形,计算Vo高电平持续的时间Th

【解】

t

H

=

0.7

⋅

(

R

1

+

R

2

)

⋅

C

t_H=0.7 \cdot (R_1+R_2 ) \cdot C

tH=0.7⋅(R1+R2)⋅C

这是2021年原题。。。

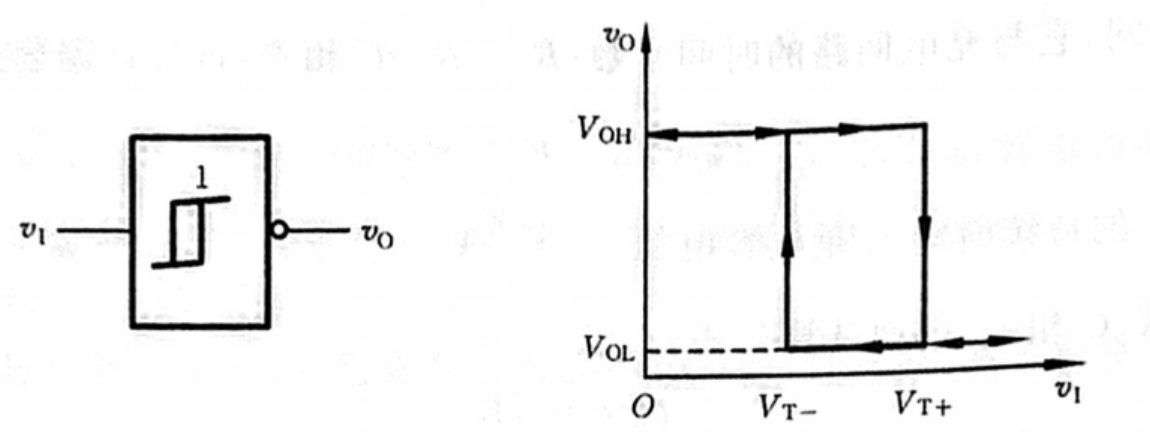

应用2 施密特触发器

图中,

v

1

v_1

v1 上升时的阈值电压

V

T

+

V_{\mathrm{T}+}

VT+ 称为正向阈值电平或上限触发电平; 下降时的阈值电压

V

T

V_{\mathrm{T}}

VT - 称为负向阈值电平或下限触发电平。它们之间的差值称为回差电压 (或滞后电压), 用

Δ

V

T

\Delta V_{\mathrm{T}}

ΔVT 表示, 即

Δ

V

T

=

V

T

+

−

V

T

−

=

1

3

V

C

C

\Delta V_{\mathrm{T}}=V_{\mathrm{T}+}-V_{\mathrm{T}-}\mathrm{=\frac{1}{3}V_{CC}}

ΔVT=VT+−VT−=31VCC

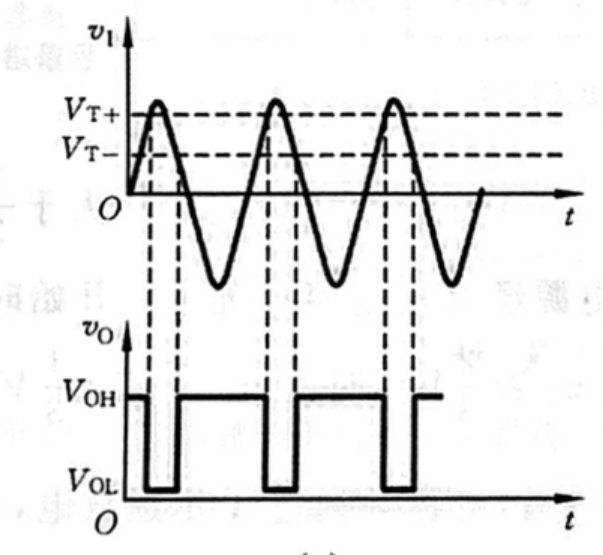

施密特触发器的应用广泛,其典型应用有波形变换、脉冲整形、幅值鉴别等。

-

波形变换:施密特触发器能将正弦波、三角波或任意形状的模拟信号波形变换成矩形波。

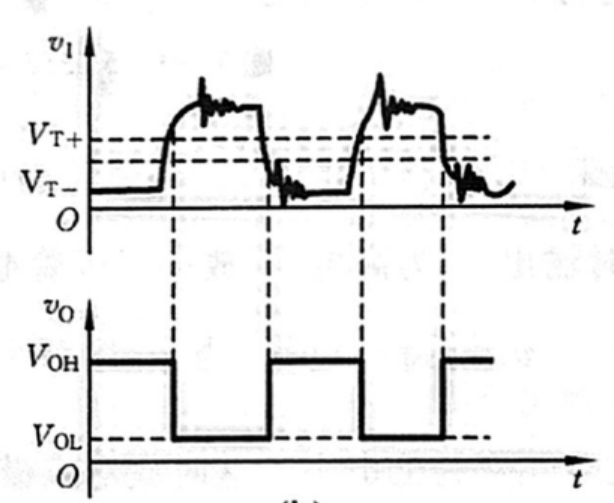

-

脉冲整形:经传输后的矩形脉冲往往由于干扰及传输线路的分布电容等因素而使信号发生畸变,出现前、后沿变坏或信号电平波形.上叠加脉动干扰波等现象。用施密特触发器,选择适当的回差电压OVτ,即可对输人信号整形后输出。

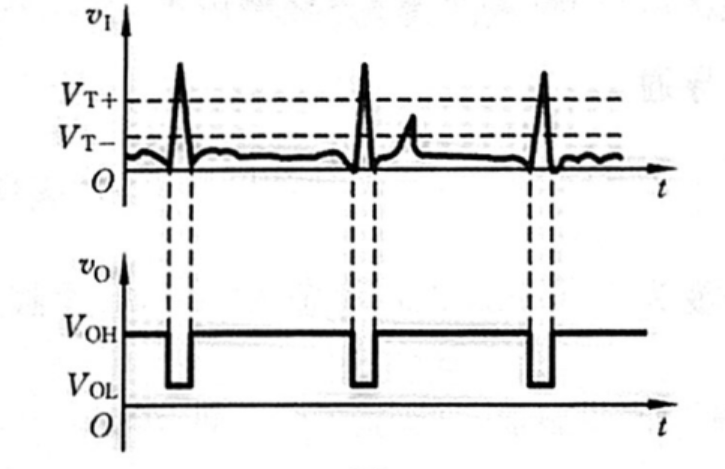

-

幅值鉴别:施密特触发器能在一系列幅值各异的脉冲信号中鉴别出幅值大于VT+的脉冲,并产生对应的输出信号。

应用3 单稳态触发器

通过调节定时元件

R

、

C

R、C

R、C 的参数,即可改变输出脉冲的宽度

t

w

t_w

tw

t

w

≈

1.1

R

C

t_w \approx 1.1 R C

tw≈1.1RC

考试指南

这里列举一下常见的大题,供大家参考

函数发生器

函数发生器指的是用中规模组合电路实现某个逻辑函数的功能,通常使用74138译码器和选择器。通常出的题型有以下情况:

-

实现逻辑函数的功能

F ( A , B , C ) = ∑ m ( 3 , 6 , 7 ) \mathrm{F(A,B,C)=\sum m(3,6,7)} F(A,B,C)=∑m(3,6,7) -

实现逻辑函数 L = A B + B C \mathrm{L=AB+BC} L=AB+BC

这两种情况本质上都在问一个东西,就是当输入 A , B , C \mathrm{A,B,C} A,B,C 时应该什么时候输出1,什么时候输出0,通过电路来实现这一功能

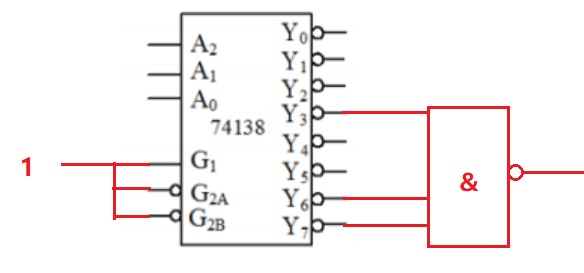

74138译码器

该译码器在输出门上具有最强大的非门,配合与非门可以实现逻辑函数

【例】用3线-8线译码器74138 (可附加与非门)实现组合逻辑函数L=AB+BC, 要求画出电路图: (10分)

【解】先大概看一下他给的板,下面那个使能端跟书本上的不太一样,但道理不变的,他那两个绑在一起的已经提前给了非门了,所以三个端绑一起接个恒1信号就行,然后看看题目,他要实现的逻辑函数有三个参数,刚好对应三条线,因此我们要画真值表

可以看到,只有

m

3

,

m

6

,

m

7

\mathrm{m_3,m_6,m_7}

m3,m6,m7 会输出1,题目要求用与非门,那刚好这个与非门就能实现了原因是

Z

i

(

A

i

,

B

i

,

C

i

)

=

m

3

+

m

6

+

m

7

=

m

3

+

m

6

+

m

7

‾

‾

=

m

3

‾

⋅

m

6

‾

⋅

m

7

‾

‾

\mathrm{Z_i(A_i,B_i,C_i)=m_3+m_6+m_7=\overline{\overline{m_3+m_6+m_7}}=\overline{\overline{m_3}\cdot\overline{m_6}\cdot\overline{m_7}}}

Zi(Ai,Bi,Ci)=m3+m6+m7=m3+m6+m7=m3⋅m6⋅m7

而

Y

\mathrm{Y}

Y 输出天然带个非,所以一个与非门就搞定了

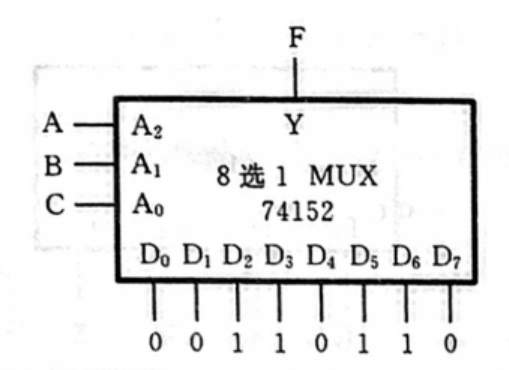

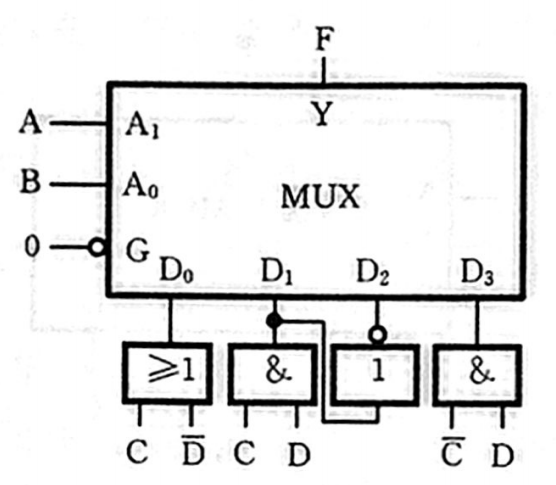

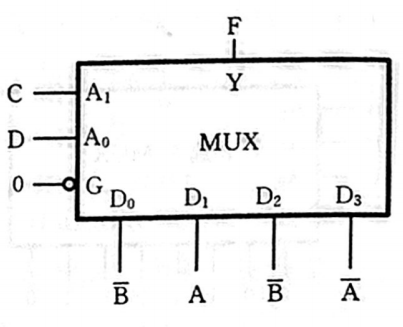

选择器

选择器是一个由 n n n 个选择输入, 2 n 2^n 2n 个数据输入,1个输出的电路,输出的结果取决于选择输入和输入

换句话说,你可以控制输出的是哪一位的

D

\mathrm{D}

D ,也可以控制输出的

D

\mathrm{D}

D 是0还是1。由此,我们可以写出选择器的函数表达式,这对于我们解决问题很关键:

Y

=

A

‾

2

A

‾

1

A

‾

0

D

0

+

A

‾

2

A

‾

1

A

0

D

1

+

A

‾

2

A

1

A

‾

0

D

2

+

A

‾

2

A

1

A

0

D

3

+

A

2

A

‾

1

A

‾

0

D

4

+

A

2

A

ˉ

1

A

0

D

5

+

A

2

A

1

A

‾

0

D

6

+

A

2

A

1

A

0

D

7

\begin{aligned} Y= & \overline{\mathrm{A}}_2 \overline{\mathrm{A}}_1 \overline{\mathrm{A}}_0 \mathrm{D}_0+\overline{\mathrm{A}}_2 \overline{\mathrm{A}}_1 \mathrm{~A}_0 \mathrm{D}_1+\overline{\mathrm{A}}_2 \mathrm{~A}_1 \overline{\mathrm{A}}_0 \mathrm{D}_2+\overline{\mathrm{A}}_2 \mathrm{~A}_1 \mathrm{~A}_0 \mathrm{D}_3 \\ & +\mathrm{A}_2 \overline{\mathrm{A}}_1 \overline{\mathrm{A}}_0 \mathrm{D}_4+\mathrm{A}_2 \bar{A}_1 \mathrm{~A}_0 \mathrm{D}_5+\mathrm{A}_2 \mathrm{~A}_1 \overline{\mathrm{A}}_0 \mathrm{D}_6+\mathrm{A}_2 \mathrm{~A}_1 \mathrm{~A}_0 \mathrm{D}_7 \end{aligned}

Y=A2A1A0D0+A2A1 A0D1+A2 A1A0D2+A2 A1 A0D3+A2A1A0D4+A2Aˉ1 A0D5+A2 A1A0D6+A2 A1 A0D7

这个表达式很好解释,以前两个为例,

A

‾

2

A

‾

1

A

‾

0

D

0

\overline{\mathrm{A}}_2 \overline{\mathrm{A}}_1 \overline{\mathrm{A}}_0 \mathrm{D}_0

A2A1A0D0 指的是,当选择输入为

(

000

)

(000)

(000) 时,输出

D

0

\mathrm{D_0}

D0,

A

‾

2

A

‾

1

A

0

D

1

\overline{\mathrm{A}}_2 \overline{\mathrm{A}}_1 {\mathrm{A}}_0 \mathrm{D}_1

A2A1A0D1 指的是,当选择输入为

(

001

)

(001)

(001) 时,输出

D

1

\mathrm{D_1}

D1,其实这就是选择器的数学表达式,根据这个,可以将选择器改造成函数发生器,根据改造的种类可以分为以下三种

-

m = n m=n m=n (用n个数据输入来实现 m m m 的变量的函数)

设计这种电路跟译码器是神似的,甚至真值表都不用画

【例】用8路MUX实现以下逻辑功能

F ( A , B , C ) = ∑ m ( 2 , 3 , 5 , 6 ) \mathrm{F(A,B,C)=\sum m (2,3,5,6)} F(A,B,C)=∑m(2,3,5,6)

【解】这里指的是输出对应的 D 2 , D 3 , D 3 , D 6 \mathrm{D_2,D_3,D_3,D_6} D2,D3,D3,D6 时要为1,其余为0,那意思就是给这4个D恒1信号,其他恒0信号

-

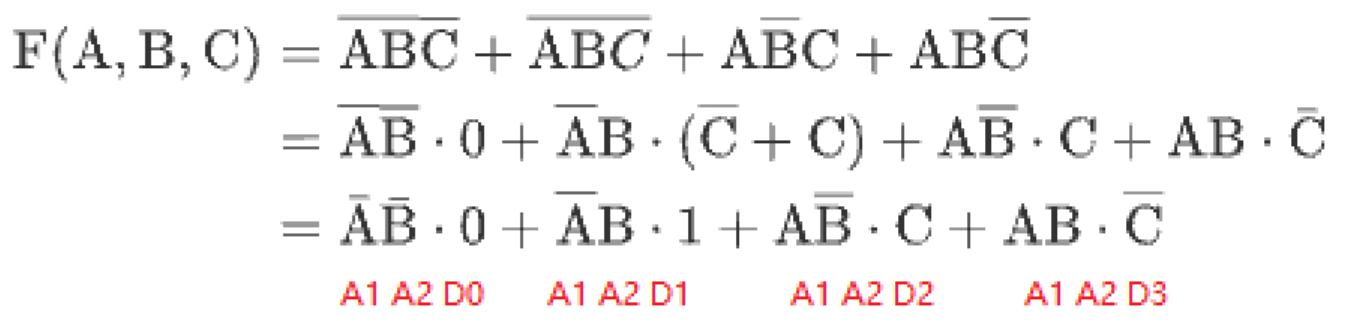

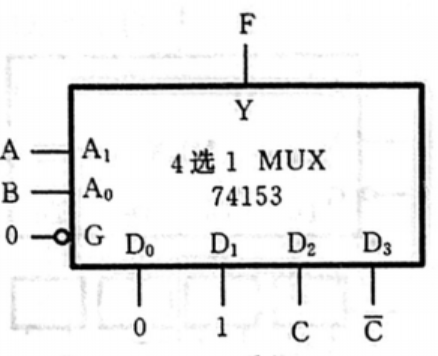

m = n + 1 m=n+1 m=n+1 (用n个数据输入来实现 m m m 的变量的函数)

【例】用4路MUX实现以下逻辑功能

F ( A , B , C ) = ∑ m ( 2 , 3 , 5 , 6 ) \mathrm{F(A,B,C)=\sum m (2,3,5,6)} F(A,B,C)=∑m(2,3,5,6)

【解】4路MUX最多允许两个 A \mathrm{A} A 输入,也就是说, C \mathrm{C} C是多余的(悲),这个时候就要把逻辑功能全展开,并按照选择器的输出函数那样按照二进制序进行排序

在排列后,发现 C \mathrm{C} C 是可以充当输入 D \mathrm{D} D 的功能的,于是就可以按照上述方式输入

-

m ≥ n + 2 m≥n+2 m≥n+2 (用n个数据输入来实现 m m m 的变量的函数)

【例】用4路MUX实现4变量逻辑函数的功能,函数表达式为

F ( A , B , C , D ) = ∑ m ( 0 , 2 , 3 , 7 , 8 , 9 , 10 , 13 ) \mathrm{F}(\mathrm{A}, \mathrm{B}, \mathrm{C}, \mathrm{D})=\sum \mathrm{m}(0,2,3,7,8,9,10,13) F(A,B,C,D)=∑m(0,2,3,7,8,9,10,13)

【解】思路是一样的,将函数表达式全展开,然后按你的想法, 你觉得把哪些变量作为选择输入,就按照二进制序排列哪些变量

F ( A , B , C , D ) = ∑ m ( 0 , 2 , 3 , 7 , 8 , 9 , 10 , 13 ) = A ‾ B ‾ C ‾ D ‾ + A ‾ B ‾ C D ‾ + A ‾ B C D ‾ + A B C D ‾ + A B ‾ C ‾ D ‾ + A B ‾ C ‾ D + A B ‾ C D ‾ + A B C ‾ D = A ‾ B ‾ ( C ‾ D ‾ + C D ‾ + C D ) + A ‾ B ⋅ C D + A B ‾ ( C ‾ D ‾ + C ‾ D + C D ‾ ) + A B ⋅ C ‾ D = A ‾ B ‾ ( C + D ‾ ) + A ‾ B ⋅ C D + A B ‾ ( C ‾ + D ‾ ) + A B ⋅ C ‾ D \begin{aligned} & \mathrm{F}(\mathrm{A}, \mathrm{B}, \mathrm{C}, \mathrm{D})=\sum \mathrm{m}(0,2,3,7,8,9,10,13) \\ & =\overline{\mathrm{A}} \overline{\mathrm{B}} \overline{\mathrm{C}} \overline{\mathrm{D}}+\overline{\mathrm{A}} \overline{\mathrm{B}} \mathrm{C} \overline{\mathrm{D}}+\overline{\mathrm{A}} \overline{\mathrm{B} C D}+\overline{\mathrm{ABCD}}+\mathrm{A} \overline{\mathrm{B}} \overline{\mathrm{C}} \overline{\mathrm{D}}+\mathrm{A} \overline{\mathrm{B}} \overline{\mathrm{C}} \mathrm{D}+\mathrm{A} \overline{\mathrm{B}} \mathrm{C} \overline{\mathrm{D}}+\mathrm{AB} \overline{\mathrm{C}} \mathrm{D} \\ & =\overline{\mathrm{A}} \overline{\mathrm{B}}(\overline{\mathrm{C}} \overline{\mathrm{D}}+\mathrm{C} \overline{\mathrm{D}}+\mathrm{CD})+\overline{\mathrm{A}} \mathrm{B} \cdot \mathrm{CD}+\mathrm{A} \overline{\mathrm{B}}(\overline{\mathrm{C}} \overline{\mathrm{D}}+\overline{\mathrm{C}} \mathrm{D}+\mathrm{C} \overline{\mathrm{D}})+\mathrm{AB} \cdot \overline{\mathrm{C}} \mathrm{D} \\ & =\overline{\mathrm{A}} \overline{\mathrm{B}}(\mathrm{C}+\overline{\mathrm{D}})+\overline{\mathrm{A}} \mathrm{B} \cdot \mathrm{CD}+\mathrm{A} \overline{\mathrm{B}}(\overline{\mathrm{C}}+\overline{\mathrm{D}})+\mathrm{AB} \cdot \overline{\mathrm{C}} \mathrm{D} \\ & \end{aligned} F(A,B,C,D)=∑m(0,2,3,7,8,9,10,13)=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD=AB(CD+CD+CD)+AB⋅CD+AB(CD+CD+CD)+AB⋅CD=AB(C+D)+AB⋅CD+AB(C+D)+AB⋅CD

根据变换后的逻辑表达式, 即可确定各数据输人 D i \mathrm{D}_i Di 分别为

D 0 = C + D ‾ D 1 = C D D 2 = C ‾ + D ‾ = + C D ‾ D 3 = C D ‾ \mathrm{D}_0=\mathrm{C}+\overline{\mathrm{D}} \quad \mathrm{D}_1=\mathrm{CD} \quad \mathrm{D}_2=\overline{\mathrm{C}}+\overline{\mathrm{D}}=+\overline{\mathrm{CD}} \quad \mathrm{D}_3=\overline{\mathrm{CD}} D0=C+DD1=CDD2=C+D=+CDD3=CD

F ( A , B , C , D ) = ∑ m ( 0 , 2 , 3 , 7 , 8 , 9 , 10 , 13 ) = A ‾ B ‾ C ‾ D ‾ + A ‾ B ‾ C D ‾ + A ‾ B ‾ C D + A B C D ‾ + A B ‾ C ‾ D ‾ + A B ‾ C ‾ D + A B C ‾ D ‾ + A B C ‾ D = C ‾ D ‾ ( A ‾ B ‾ + A B ‾ ) + C ‾ D ( A B ‾ + A B ) + C D ‾ ( A ‾ B ‾ + A B ‾ ) + C D ( A ‾ B ‾ + A ‾ B ) = C ‾ D ‾ ⋅ B ‾ + C ‾ D ⋅ A + C D ‾ ⋅ B ‾ + C D ⋅ A ‾ \begin{aligned} \mathrm{F}(\mathrm{A}, \mathrm{B}, \mathrm{C}, \mathrm{D}) & =\sum \mathrm{m}(0,2,3,7,8,9,10,13) \\ & =\overline{\mathrm{A}} \overline{\mathrm{B}} \overline{\mathrm{C}} \overline{\mathrm{D}}+\overline{\mathrm{A}} \overline{\mathrm{B}} \mathrm{C} \overline{\mathrm{D}}+\overline{\mathrm{A}} \overline{\mathrm{B}} \mathrm{CD}+\overline{\mathrm{A} B C D}+\mathrm{A} \overline{\mathrm{B}} \overline{\mathrm{C}} \overline{\mathrm{D}}+\mathrm{A} \overline{\mathrm{B}} \overline{\mathrm{C}} \mathrm{D}+\mathrm{A} \overline{\mathrm{B} C} \overline{\mathrm{D}}+\mathrm{AB} \overline{\mathrm{C}} \mathrm{D} \\ & =\overline{\mathrm{C}} \overline{\mathrm{D}}(\overline{\mathrm{A}} \overline{\mathrm{B}}+\mathrm{A} \overline{\mathrm{B}})+\overline{\mathrm{C}} \mathrm{D}(\mathrm{A} \overline{\mathrm{B}}+\mathrm{AB})+C \overline{\mathrm{D}}(\overline{\mathrm{A}} \overline{\mathrm{B}}+\mathrm{A} \overline{\mathrm{B}})+\mathrm{CD}(\overline{\mathrm{A}} \overline{\mathrm{B}}+\overline{\mathrm{A}} \mathrm{B}) \\ & =\overline{\mathrm{C}} \overline{\mathrm{D}} \cdot \overline{\mathrm{B}}+\overline{\mathrm{C}} \mathrm{D} \cdot \mathrm{A}+\mathrm{C} \overline{\mathrm{D}} \cdot \overline{\mathrm{B}}+\mathrm{CD} \cdot \overline{\mathrm{A}} \end{aligned} F(A,B,C,D)=∑m(0,2,3,7,8,9,10,13)=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD=CD(AB+AB)+CD(AB+AB)+CD(AB+AB)+CD(AB+AB)=CD⋅B+CD⋅A+CD⋅B+CD⋅A

根据变换后的逻辑表达式, 可确定各数据输人 D i D_i Di 分别为

D 0 = B ‾ D 1 = A D 2 = B ‾ D 3 = A ‾ \mathrm{D}_0=\overline{\mathrm{B}} \quad \mathrm{D}_1=\mathrm{A} \quad \mathrm{D}_2=\overline{\mathrm{B}} \quad \mathrm{D}_3=\overline{\mathrm{A}} D0=BD1=AD2=BD3=A

化简

暴力化

- 定理 3(吸收律): A + A ⋅ B = A A ⋅ ( A + B ) = A \mathrm{A+A\cdot B=A\quad\quad A\cdot (A+B)=A} A+A⋅B=AA⋅(A+B)=A

- 定理 4(消除律): A + A ˉ ⋅ B = A + B A ⋅ ( A ˉ + B ) = A ⋅ B \mathrm{A+\bar{A}\cdot B=A+B\quad\quad A\cdot (\bar{A}+B)=A\cdot B} A+Aˉ⋅B=A+BA⋅(Aˉ+B)=A⋅B

- 定理 5(对合律): A ˉ ˉ = A \mathrm{\bar{\bar{A}}=A} Aˉˉ=A

- 定理 6(互补律): A + B ‾ = A ˉ ⋅ B ˉ A ⋅ B ‾ = A ˉ + B ˉ \overline{A+B}=\bar{A} \cdot \bar{B} \quad\quad \overline{A \cdot B}=\bar{A}+\bar{B} A+B=Aˉ⋅BˉA⋅B=Aˉ+Bˉ

- 定理 7(并项律): A ⋅ B + A ⋅ B ˉ = A ( A + B ) ⋅ ( A + B ˉ ) = A \mathrm{A\cdot B +A\cdot \bar{B} =A \quad \quad (A+B)\cdot(A+\bar{B})=A} A⋅B+A⋅Bˉ=A(A+B)⋅(A+Bˉ)=A

- 定理 8(包含律): A ⋅ B + A ˉ ⋅ C + B ⋅ C = A ⋅ B + A ˉ ⋅ C \mathrm{A\cdot B+\bar{A}\cdot C+B\cdot C =A\cdot B+\bar{A}\cdot C } A⋅B+Aˉ⋅C+B⋅C=A⋅B+Aˉ⋅C

【例】化简 F = A D + A D ˉ + A B + A ˉ C + B D + A C E G + B ˉ E G + D E G H F=A D+A \bar{D}+A B+\bar{A} C+B D+A C E G+\bar{B} E G+D E G H F=AD+ADˉ+AB+AˉC+BD+ACEG+BˉEG+DEGH

【解】

F

=

A

D

+

A

D

ˉ

+

A

B

+

A

ˉ

C

+

B

D

+

A

C

E

G

+

B

ˉ

E

G

+

D

E

G

H

=

A

+

A

B

+

A

ˉ

C

+

B

D

+

A

C

E

G

+

B

ˉ

E

G

+

D

E

G

H

=

A

+

A

B

+

C

+

B

D

+

A

C

E

G

+

B

ˉ

E

G

+

D

E

G

H

=

A

+

C

+

B

D

+

A

C

E

G

+

B

ˉ

E

G

+

D

E

G

H

=

A

+

C

+

B

D

+

B

ˉ

E

G

+

D

E

G

H

\begin{aligned} F&=A D+A \bar{D}+A B+\bar{A} C+B D+A C E G+\bar{B} E G+D E G H \\ &= A+A B+\bar{A} C+B D+A C E G+\bar{B} E G+D E G H \\ &= A+A B+ C+B D+A C E G+\bar{B} E G+D E G H \\ &= A+ C+B D+A C E G+\bar{B} E G+D E G H\\ &= A+ C+B D+\bar{B} E G+D E G H\\ \end{aligned}

F=AD+ADˉ+AB+AˉC+BD+ACEG+BˉEG+DEGH=A+AB+AˉC+BD+ACEG+BˉEG+DEGH=A+AB+C+BD+ACEG+BˉEG+DEGH=A+C+BD+ACEG+BˉEG+DEGH=A+C+BD+BˉEG+DEGH

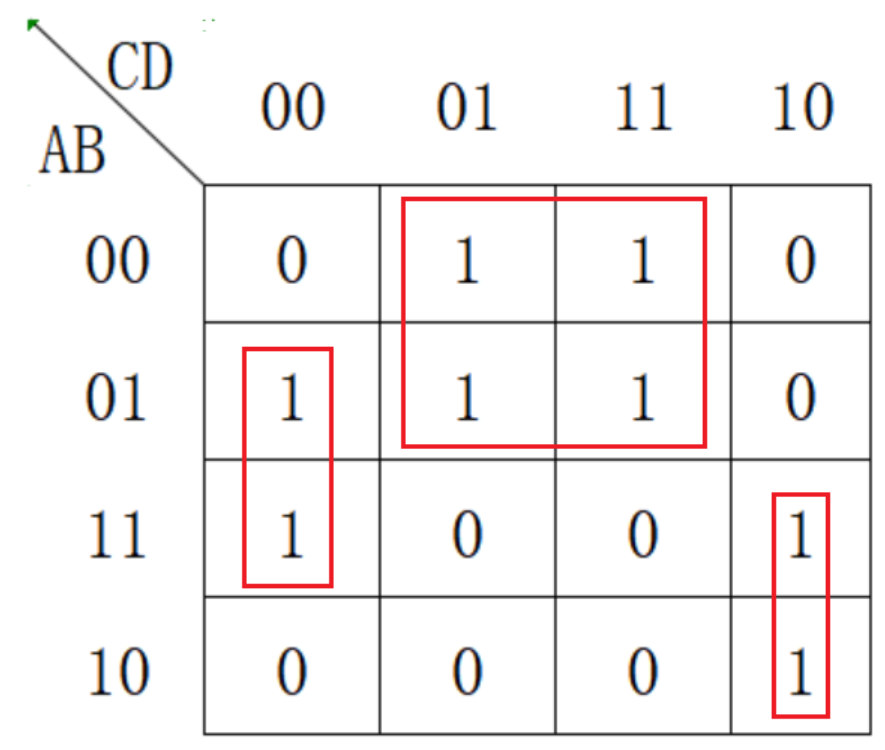

卡诺图化

【例】卡诺图法求函数 F = A B D ˉ + A ˉ D + A ˉ B C ˉ + A C D ˉ F=A B \bar{D}+\bar{A} D+\bar{A} B \bar{C}+A C \bar{D} F=ABDˉ+AˉD+AˉBCˉ+ACDˉ 的最简与或式

【解】

F = A ˉ D + B C ˉ D ˉ + A C D ˉ F=\bar{A}D+B\bar{C}\bar{D}+AC\bar{D} F=AˉD+BCˉDˉ+ACDˉ

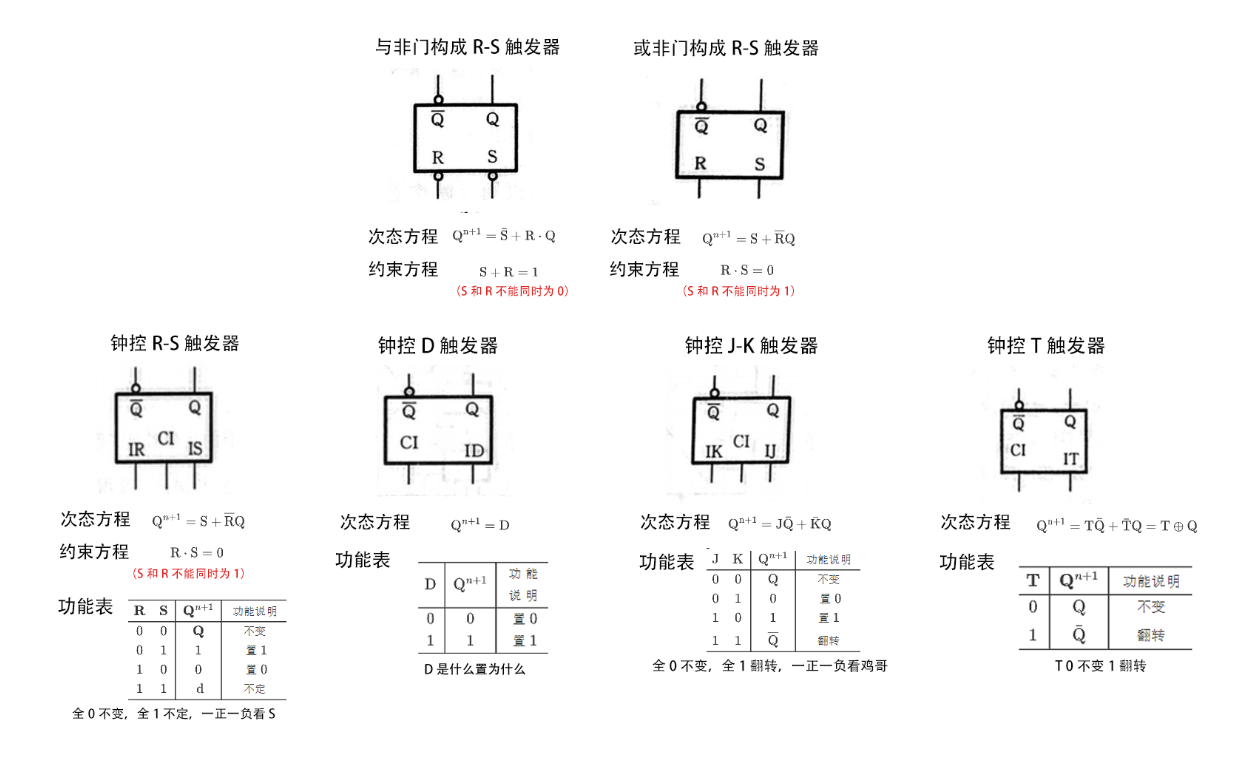

触发器大全

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?