基于FPGA串口发送与接收

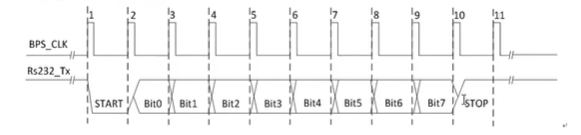

RS232协议的时序图如下

在这里可以看到,以低电平为开始的起始位,高电平为截止位,中间传输八位的数据。

传输的速率分为9600bps,19200bps与38400bps等,例如9600bps,系统时钟为1M用{(1/9600)x10^8}/2再减1,就可以得到9600的波特率。

这里只列出几种,当系统复位时默认为9600bps,因为最为常用。从时序图上看,每一位数据发送的时候都应该有一个周期的时钟信号,这里写一个时钟模块。

每次开始传输数据,都让bps_clk有一个周期的高电平。

每次开始传输数据,都让bps_clk有一个周期的高电平。

FPGA串口收发

最新推荐文章于 2024-04-19 21:28:53 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8209

8209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?