1 总体概述

为避免闭门造车,找一个不错的开源项目,学习在FPGA上实现CNN,为后续的开发奠定基础

1.1 项目链接

大佬的开源项目链接: CNN-FPGA

链接跳转界面如下:

大佬的该项目已经发表论文,而且开源工程结构清晰,同时附带了硬件文档,所以对于咱们初学者来说,这个项目很友好

发表的论文:

硬件文档:

1.2 项目介绍

用ZYNQ FPGA搭建LeNet-5卷积神经网络(CNN),实现手写数字识别,数据集为MNIST。LeNet-5网络结构如图所示:

图片来自附带的技术文档《Hardware Documentation》

1.2.1 卷积(Convolution)

LeNet-5网络有3个卷积层,每个层的卷积核大小均为5x5。本项目的实现方案权衡并行度、速度和资源占用。下图中绿色部分即为卷积层:

图片来自附带的技术文档《Hardware Documentation》

1.2.2 TanH激活函数(TanH Activation)

LeNet-5网络的激活函数是双曲正切函数(TanH),如图紫色部分所示:

图片来自附带的技术文档《Hardware Documentation》

1.2.3 SoftMax激活函数(SoftMax Activation)

LeNet-5网络的最后一层是SoftMax激活层,输出最终的手写数字分类结果,如图蓝色部分所示:

图片来自附带的技术文档《Hardware Documentation》

1.2.4 平均池化层(Average Pooling)

LeNet-5网络有2个平均池化层,减小卷积层的输出数据的大小,如图橙色部分所示:

图片来自附带的技术文档《Hardware Documentation》

1.2.5 综合网络(Integrating Network)

将上述模块综合到一起,调通控制通路和数据通路,如图所示:

图片来自附带的技术文档《Hardware Documentation》

1.3 验证思路

(1)在不同软件设计语言(Python和C++)编写的脚本上运行功能相似的代码

(2)为设计模块创建相应的TestBench(激励),记录输出结果

(3)对比两组输出数据是否一致,并随机抽样进行转换验证

(4)如果有错误,修改代码逻辑

1.4 项目目录

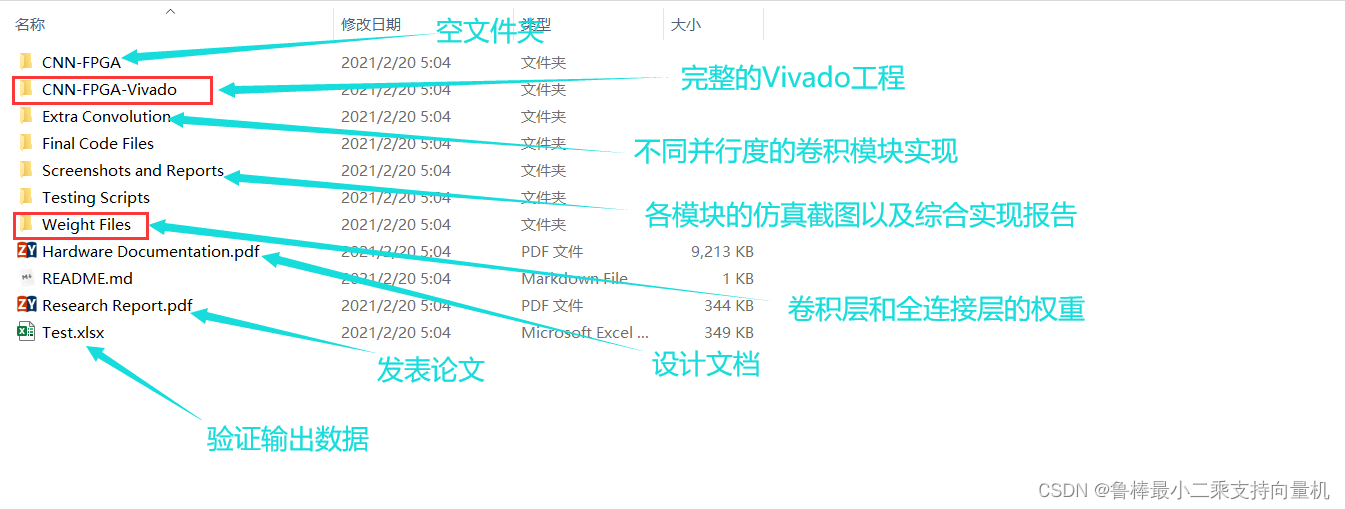

项目完整目录如下:

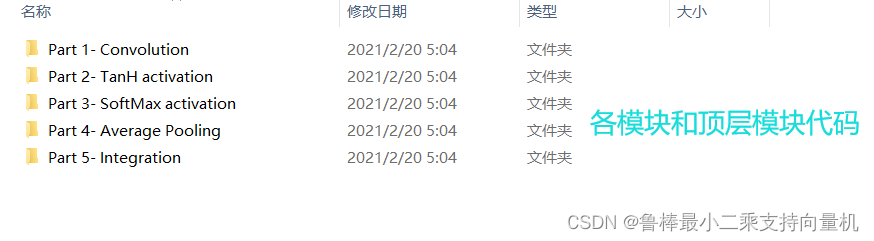

Final Code Files文件夹展开:

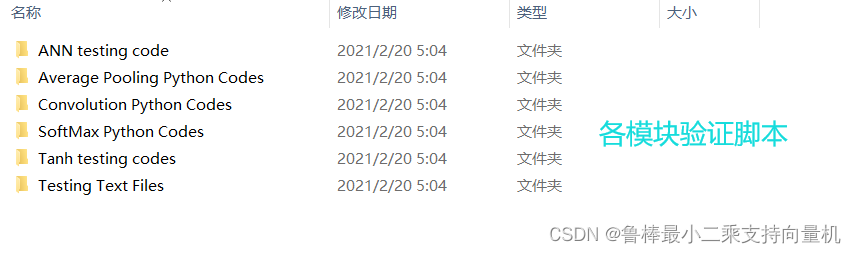

Testing Scripts文件夹展开:

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距

1389

1389

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?