Xilinx 7系 FPGA片上资源之触发器 FDCE FDPE FDRE FDSE

简介

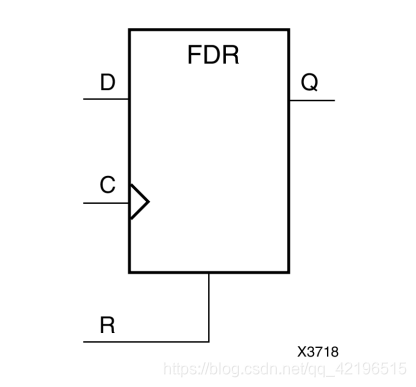

FDR : D Flip-Flop with Synchronous Rsest 同步清除D触发器。FDR 拥有一个时钟输入接口,一个D触发器数据接口,一个同步复位接口和一个触发器输出接口,当同步复位接口为高电平时,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平时,时钟的上升沿触发寄存器装载数据接口的数据。

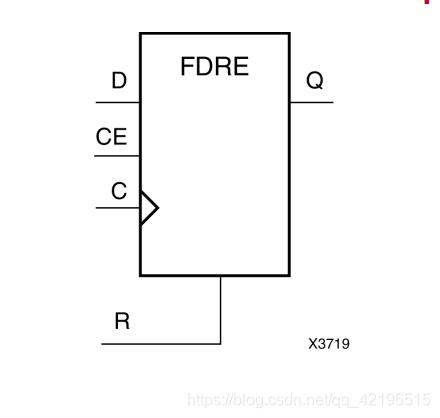

FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 带使能功能的同步清除D触发器,相比与FDR多了一个使能接口,当同步复位接口为高电平时覆盖所有其他输出,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

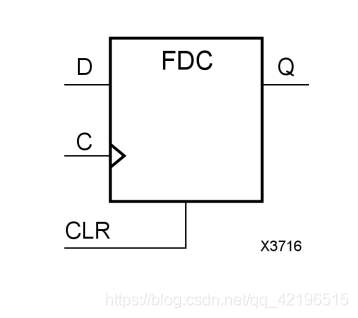

FDC :: D Flip-Flop with Asynchronous Clear 带异步清除D触发器 ,与 FDR的区别是。当CLR置为高电平时,不需要等到下一个时钟的上升沿就可以复位寄存器。

FDC :: D Flip-Flop with Asynchronous Clear 带异步清除D触发器 ,与 FDR的区别是。当CLR置为高电平时,不需要等到下一个时钟的上升沿就可以复位寄存器。

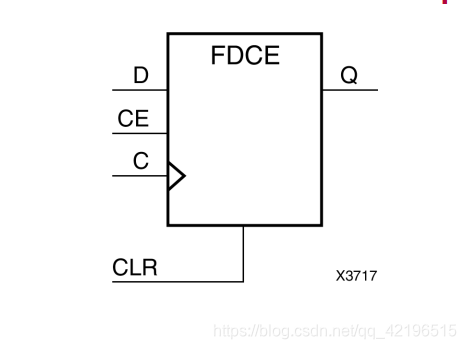

FDCE:D Flip-Flop with Clock Enable and AsynchronousReset 带使能功能的异步清除D触发器,相比与FDRE将同步复位变化成异步复位,当同步复位接口为高电平时,直接触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

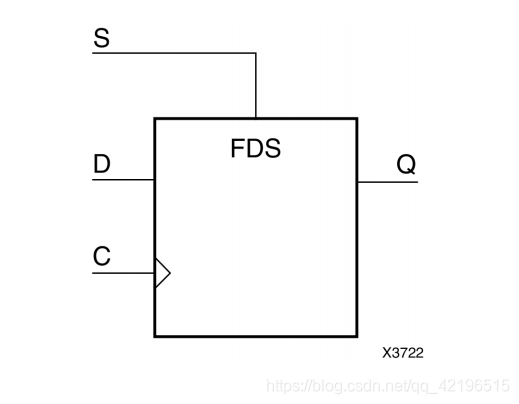

FDS:D Flip-Flop with Synchronous Set 带同步置位的D触发器 当置为端为低电平时,在时钟的上升沿触发数据保存在触发器中,当置位端为低电平时,在一个时钟的上升沿触发导致触发器清0

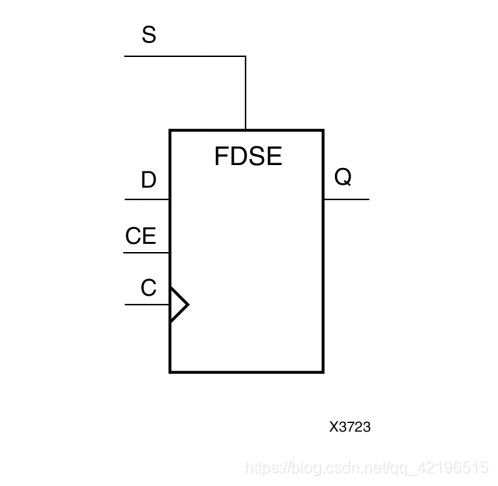

FDSE:D Flip-Flop with Clock Enable and Synchronous Set 带时钟使能和同步置位的D触发器。当置位端为高电平是覆盖所有输出,一个时钟的上升沿触发导致寄存器置位,当置位端为低电平和时钟使能位为高电平时,在一个时钟的上升沿触发导致寄存器装载数据口的数据。

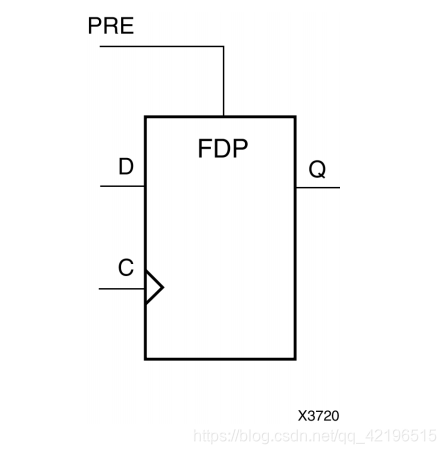

FDP:D Flip-Flop with Asynchronous Preset 带有异步预置的D触发器 相比FDS不需要等到时钟的上升沿,即刻可进行置位。

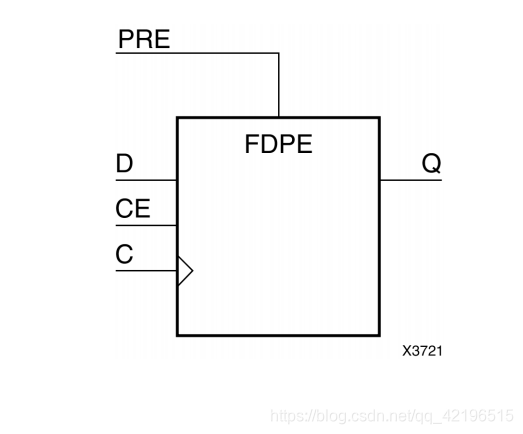

FDPE:D Flip-Flop with Clock Enable and Asynchronous Preset 带有时钟使能和异步置位的D触发器 相比于FDSE不需要等到时钟的上升沿,即刻可进行置位。

FDPE:D Flip-Flop with Clock Enable and Asynchronous Preset 带有时钟使能和异步置位的D触发器 相比于FDSE不需要等到时钟的上升沿,即刻可进行置位。

使用always块综合实现各种触发器

```handlebars

module exp(

input clk,

input rst,

input A,

input B,

output reg Q,

output reg Q1,

output reg Q2,

output reg Q3

);

//or posedge rst

always @(posedge clk or posedge rst) begin //异步复位 综合出FDCE

if(rst)

Q<=0;

else begin

Q<=A|B;

end

end

always @(posedge clk ) begin //同步复位 综合出FDRE

if(rst)

Q1<=1;

else begin

Q1<=A|B;

end

end

always @(posedge clk or posedge rst) begin//异步置位 综合出FDPE

if(rst)

Q2<=1;

else begin

Q2<=A|B;

end

end

always @(posedge clk) begin//同步置位 综合出FDSE

if(rst)

Q3<=1;

else begin

Q3<=A|B;

end

end

endmodule

使用源语综合出各种触发器

FDCE:

FDCE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDCE_inst (

.Q(Q), // 1-bit Data output

.C(C), // 1-bit Clock input

.CE(CE), // 1-bit Clock enable input

.CLR(CLR), // 1-bit Asynchronous clear input

.D(D) // 1-bit Data input

);

FDPE:

FDPE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDPE_inst (

.Q(Q), // 1-bit Data output

.C(C), // 1-bit Clock input

.CE(CE), // 1-bit Clock enable input

.PRE(PRE), // 1-bit Asynchronous preset input

.D(D) // 1-bit Data input

);

FDRE:

FDRE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDRE_inst (

.Q(Q), // 1-bit Data output

.C(C), // 1-bit Clock input

.CE(CE), // 1-bit Clock enable input

.R(R), // 1-bit Synchronous reset input

.D(D) // 1-bit Data input

);

FDSE:

FDSE #(

.INIT(1'b0) // Initial value of register (1'b0 or 1'b1)

) FDSE_inst (

.Q(Q), // 1-bit Data output

.C(C), // 1-bit Clock input

.CE(CE), // 1-bit Clock enable input

.S(S), // 1-bit Synchronous set input

.D(D) // 1-bit Data input

);

2261

2261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?