题目

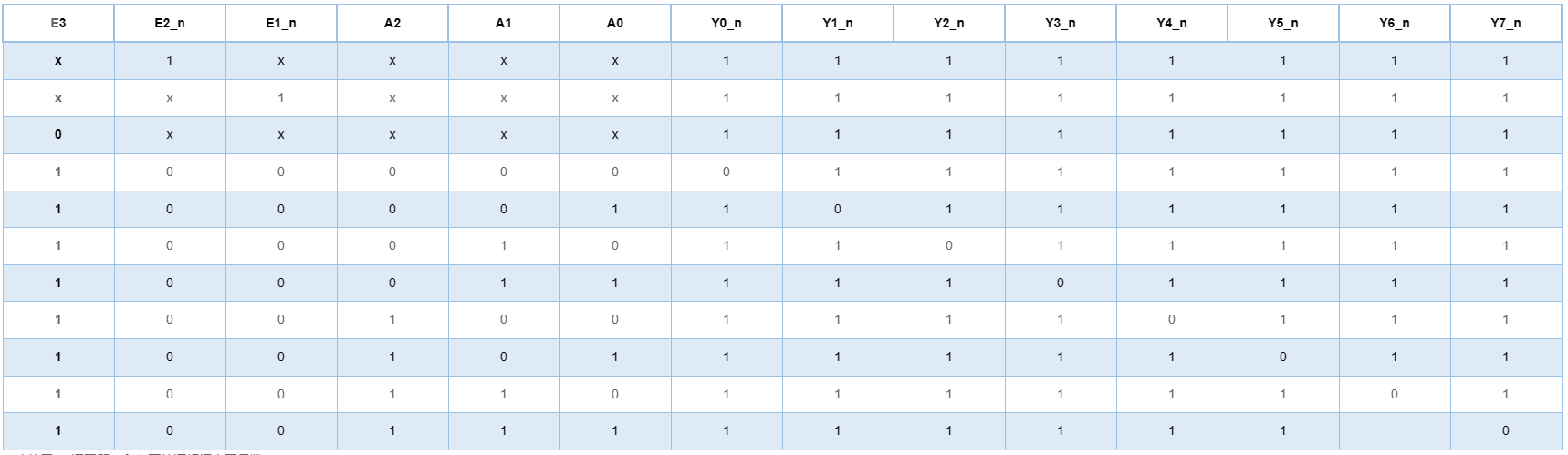

在本题中,已经给出了下面74HC138译码器真值表对应的3-8译码器模块程序。需要例化该模块,实现逻辑函数:L=(~A)B+AC。

| 信号 | 类型 | 输入/输出 | 位宽 |

|---|---|---|---|

| A | wire | Intput | 1 |

| B | wire | Intput | 1 |

| C | wire | Intput | 1 |

| L | wire | Output | 1 |

在写Verilog代码前,根据需要实现的函数:L=(~A)B+AC。我们可以知道其真值表如下。

| A | B | C | L |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

根据上述真值表,可以知道,当ABC为010、011、101、111时,输出L为1,所以L = Y2_n + Y3_n + Y5_n + Y7_n,这里“+”号表示或操作,在数电中,我们学过,或门可以用与非门进行替换,即L = ~(Y2_n & Y3_n & Y5_n & Y7_n)。

答案

`timescale 1ns/1ns

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire [3:0] G;

wire [3:0] P;

wire [3:0] C;

assign G = A_in & B_in;

assign P = A_in ^ B_in;

assign C[0] = G[0] | P[0] & C_1;

assign C[1] = G[1] | P[1] & C[0];

assign C[2] = G[2] | P[2] & C[1];

assign C[3] = G[3] | P[3] & C[2];

assign CO = C[3];

assign S[0] = P[0] ^ C_1;

assign S[1] = P[1] ^ C[0];

assign S[2] = P[2] ^ C[1];

assign S[3] = P[3] ^ C[2];

endmodule

795

795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?