总的来说,ZYNQ开发中,对于PS端和PL端的数据交互可以采用多种方式,主要有BRAM,AXI DMA,DDR, 文件。BRAM主要适用于数据量较少,地址不连续,长度不规则的数据传输场景,AXI DMA适用于数据量较大的块状连续数据传输场景。同时可以采用读写文件来实现数据的交互。

BRAM

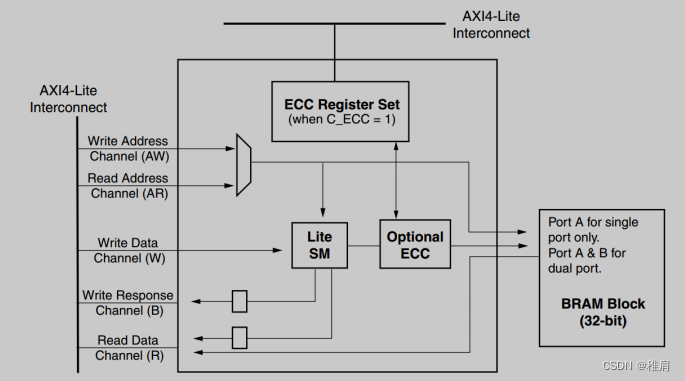

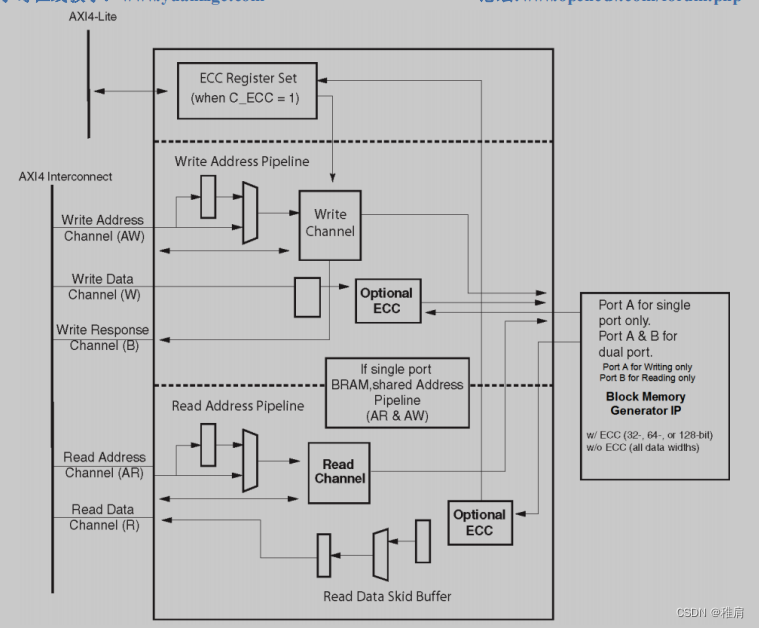

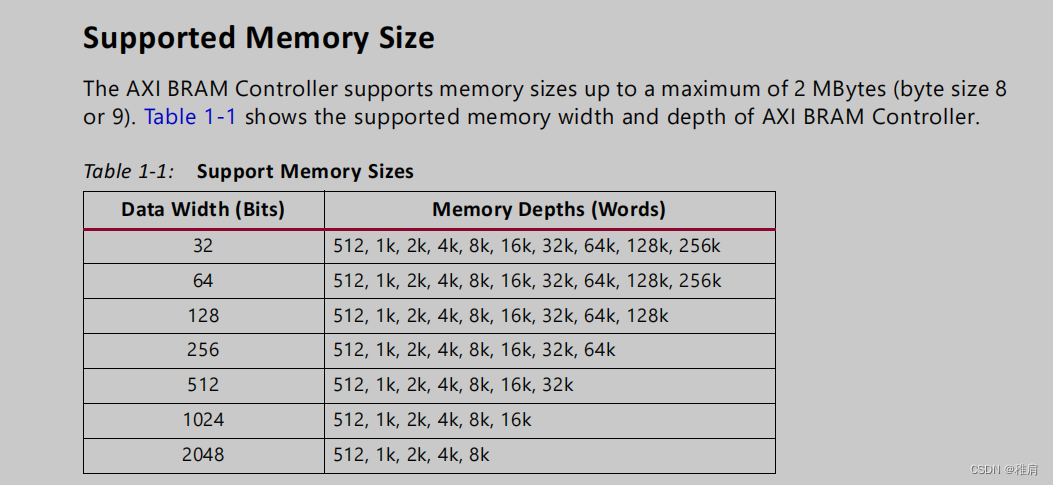

BRAM是Block RAM的缩写,是一种可编程逻辑块,用于存储数据和指令。它通常用于FPGA(现场可编程门阵列)等可编程逻辑器件中。BRAM可以存储大量的数据和指令,并且可以在运行时进行读写操作。在PS端,并不直接驱动BRAM的端口,而是通过AXI BRAM控制器对BRAM进行读写操作。该控制器可以配置为AXI4-Lite 接口模式和 AXI4 接口模式,框图如下。两者的主要区别和应用场景在于,AXI4-Lite 接口一般适用于单次传输场景,低吞吐率存储映射通信的场合,支持的数据位宽为32bit;AXI4 接口适用于高性能存储映射通信的场合,支持突发传输,支持的数据位宽格式较多。

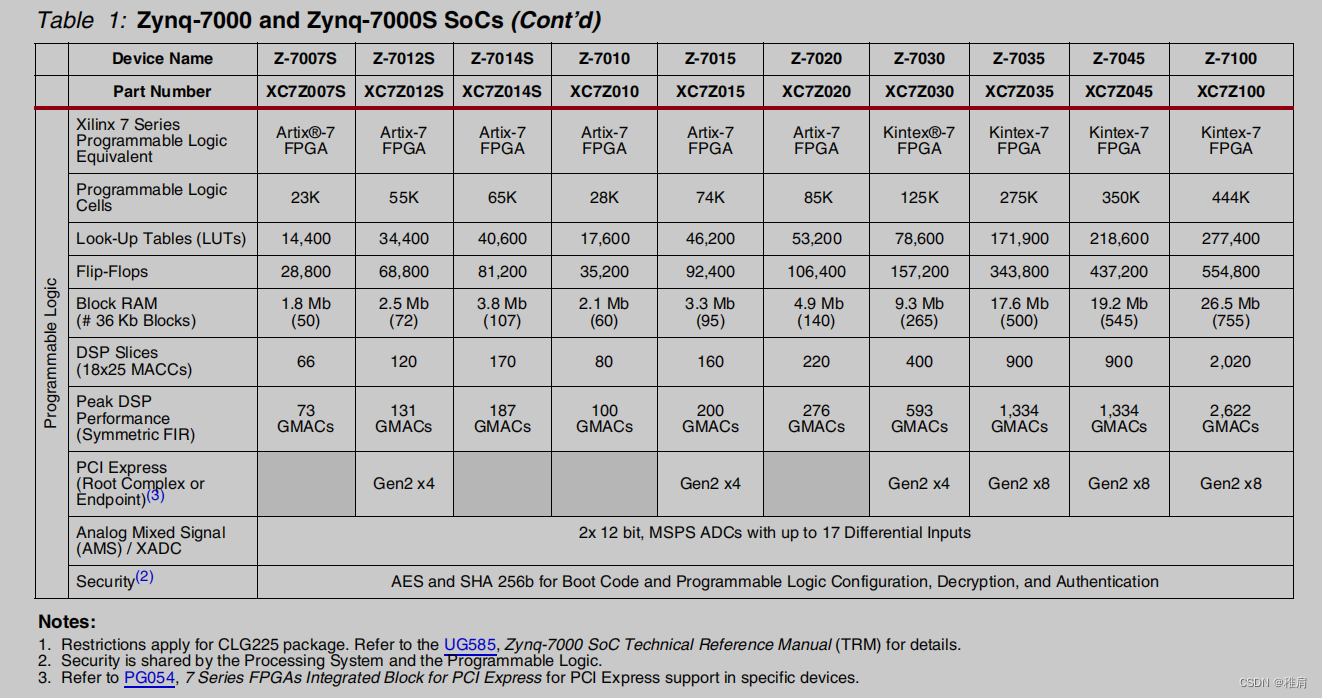

下图为常见7000系列支持的BRAM大小和数量,Z-7020的Block RAM大小为36Kb,一共有140个,总大小为4.9M。所以BRAM只适合数据量较少,地址不连续,长度不规则的数据传输场景。

设计思路

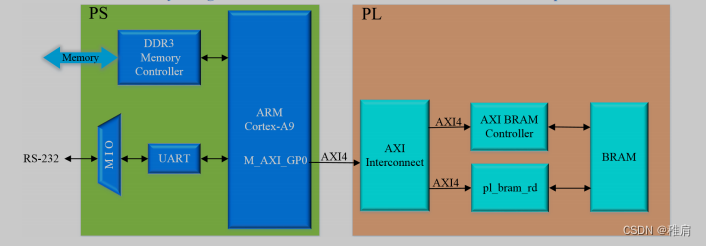

上图是PS端将串口的数据,经过M_AXI_GPO接口,通过AXI总线和PL端的AXI Interconnect IP相连接。AXI Interconnect IP与AXI BRAM Controller连接实现对BRAM的读写控制。AXI Interconnect IP也会自定义的pl_bram_rd相连实现对BRAM的读写控制。

硬件设计上:主要是对AXI BRAM Controller IP 核、Block Memory Generator IP 核、 AXI SmartConnect的配置和修改(实现内存映射主设备连接到内存映射从设备,是上述的AXI Interconnect IP的替代)。

总的来说,PS端通过AXI BRAM控制器读写PL端的BRAM,PL本身支持读写BRAM,从而实现两者的通信。

AXI DMA

DMA即直接内存访问(Direct Memory Access),是一种高效的数据传输技术,它允许外部设备在不需要CPU干预的情况下直接与计算机内存进行数据交换。DMA的主要优势在于它能够显著提高数据传输的速度和系统的整体效率。通过使用DMA,外设可以直接与内存交换数据,这样可以在数据传输过程中节省CPU资源,因为CPU不必参与每次数据传输的具体操作。这对于需要高速数据传输的应用来说尤其重要,比如在多媒体处理、高速数据采集等领域。

DMA的传输过程通常包括以下几个步骤:

初始化

CPU设置DMA控制器,指定要传输的数据量、数据源和目的地地址以及传输类型(从外设到内存、从内存到外设或内存到内存)。

数据传输

CPU向DMA控制器发送一个存储传输请求,一旦初始化完成,DMA控制器将接管总线控制权,直接在内存和外设之间传输数据,而CPU可以继续执行其他任务。

结束

数据传输完成后,DMA控制器通常会通过中断通知CPU,以便进行后续处理。

ZYNQ 的DMA

ZYNQ 的DMA主要有PS端的硬核DMA控制器DMAC和PL端的软核AXI DMA IP。

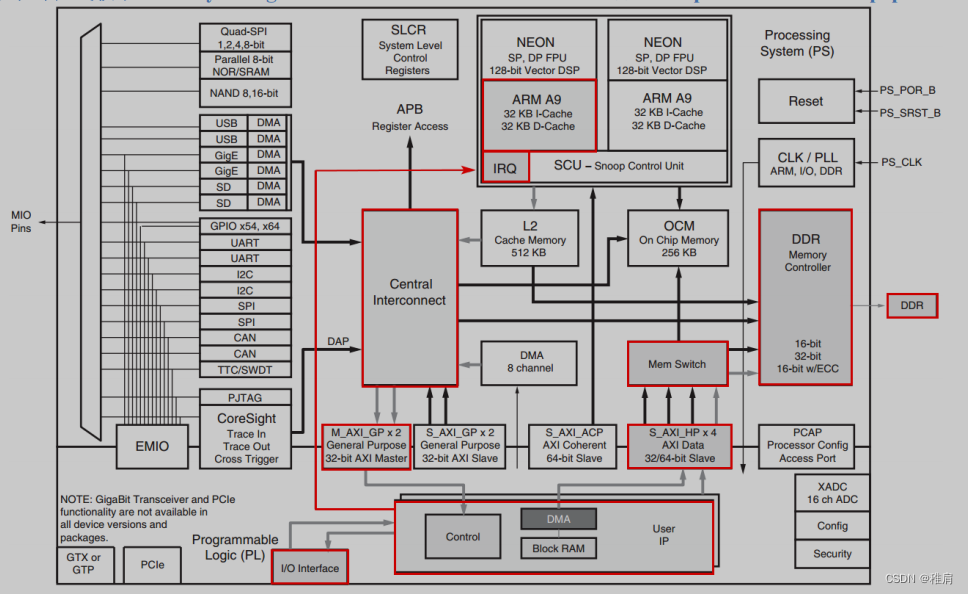

硬核DMA控制器DMAC这个设计在PS内,必须通过驻留在内存的DMA指令编程。DMAC支持8个通道的数据传输。DMAC和PL的连接是通过AXI_GP接口,这个接口只支持32位的数据位宽传输,理论最高速率位600M/s。这种模式不占用PL端的资源。

由下图可知,M_AXI_GP接口主要用于DMA的控制和基本配置,DMA传输过程中的状态可以通过中断给到PS端的中断控制器。M_AXI_HP接口有四条通路,且通路有FIFO,为大数据量突发传输提供缓冲。

三种操作模式

AXI DMA主要有三种操作模式:直接寄存器模式、分散/收集(Scatter/Gather,简称S/G)模式和直接内存访问(DMA)模式。

- 直接寄存器模式:这种模式用于在内存映射到流(Memory Mapping to Stream, MM2S)和流到内存映射(Stream to Memory Mapping, S2MM)通道上执行简单的DMA传输。它适用于资源较少的小型FPGA设备,包含两个通道,一个用于从设备到DMA的传输,另一个用于从DMA到设备的传输。

- 分散/收集(Scatter/Gather,S/G)模式:S/G模式是一种高级操作模式,它可以减轻CPU的负担,因为它能够在不需要CPU干预的情况下独立地获取或更新传输描述符。在此模式下,AXI DMA可以从内存中的多个不连续地址读取数据或将数据写入多个不连续地址。S/G模式支持循环工作,允许连续的数据传送任务在完成一轮后自动重新开始下一轮传输。

- 直接内存访问(DMA)模式:此模式提供内存与AXI4-Stream目标外设之间的高带宽直接内存访问。在这种模式下,AXI DMA能够实现的功能包括通过AXI4读主控(Read Master)将数据从AXI4内存映射传输到AXI4流(MM2S)主控。

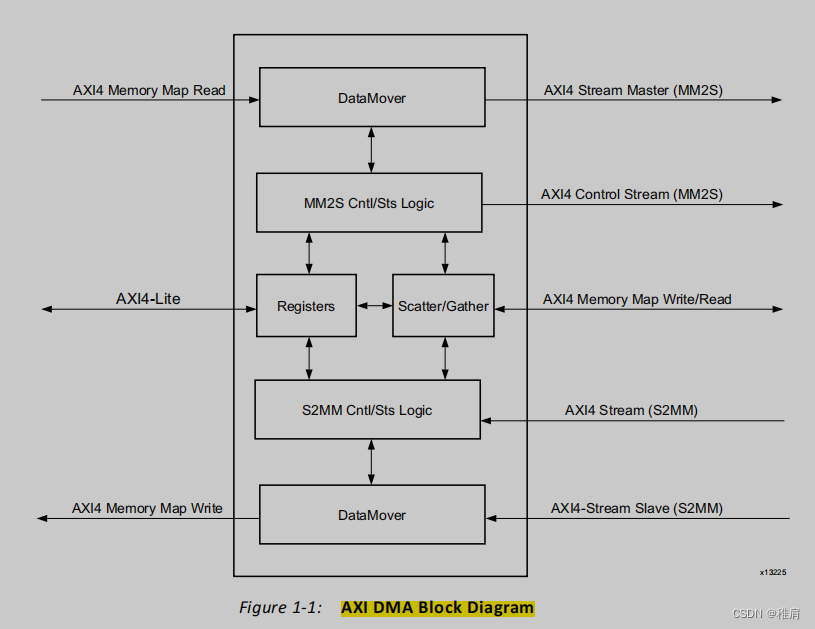

下图为AXI_DMA框图,主要用到了AXI_Lite和AXI4 Memory的读接口和写接口。AXI4 Stream主要用来对外设的读写,master(MM2S)是对外设的写,slave(S2MM)是对外设的读。

Primary AXI4 data width support of 32, 64, 128, 256, 512 and 1,024 bits

Primary AXI4-Stream data width support of 8, 16, 32, 64, 128, 256, 512 and 1,024 bits

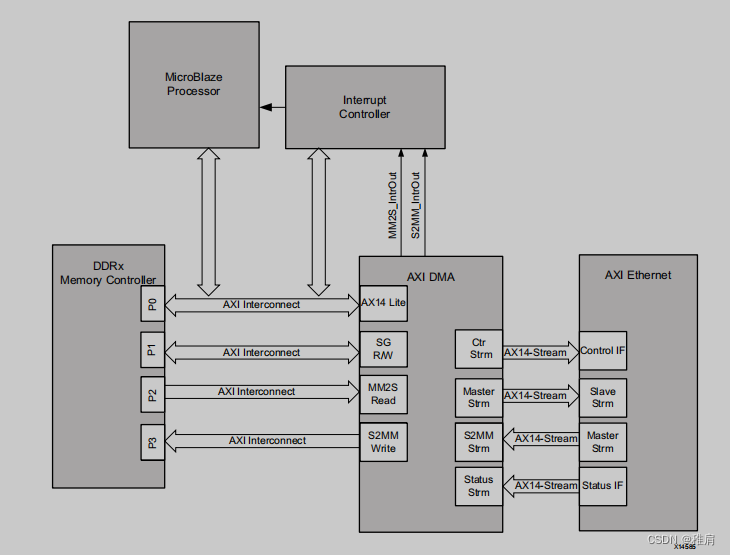

典型的应用场景框图如下,通过DMA实现网络端口和DDR之间的数据读写。

4356

4356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?