FPGA(Field-Programmable Gate Array)现场可编程门阵列

通过JTAG、AS、PS等方式现场对器件进行编程;门是实现基本逻辑关系的电路;将实现基本关系的电路按照阵列的形式排布。

(1)组成三要素

可编程逻辑功能块(Logic Blocks)、片内互联线(Programmable Interconnect)、输入输出块(I/O Blocks)

1)可编程逻辑功能块(Logic Blocks)Logic Element

是实现用户功能的基本单元,多个逻辑功能块规则地排成阵列分布在整个芯片,具体包括:查找表、D触发器(DFF,存储功能用于时序逻辑)、进位链(用于通信)等结构。

cyclone IV图中,LUT为查找表,实现组合逻辑功能,为四输入,输出两条路,其中一路接同步加载清零逻辑后接入可编程寄存器D触发器,CLK接通后取用D端数据给Q端输出,最终接入2选1多路器。(将直接结果经D触发器打一拍),下图为cyclone VI,同理。

综上,可编程逻辑单元LE的结构如下图所示。一种只用LUT实现组合逻辑,一种只用D触发器实现打拍,一种都用实现时序逻辑。

2)可编程输入输出块

完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元的四周。包括:输出寄存器、输入寄存器、输出使能寄存器、输入延迟链、输出延迟链、上拉电阻。

cyclone IV图中,Output Register为输出寄存器,输入为内部连线接与门,输出到达二选一多路器,输出延迟链Output Pin Delay到IO缓冲器,最终在管脚输出。(快速输出,离管脚最近到达管脚延迟短,优化时序性能);而数据从管脚进来会先到达Input Pin Delay输入延迟链,到Input Register输入寄存器,最终输入到内部连线上;OE Register输出使能寄存器,IO实现三态的高阻态需要开关,0/1选择门的开关,管脚输出OE打开,管脚输入则OE关闭。其中,上拉电阻引脚拉为高电平,做I2C用到。

3)可编程内部互联资源块

包括各种长度的连线线段和可编程连接开关。如下图,Altera采用行、列、局部快速通道。

(2)可编程原理

1) 与PLD的主要区别

编程原理不同,PLD修改逻辑功能(内联电路固定)进行编程,而FPGA修改内连线的布线编程,适合实现多级的逻辑功能。

2)类型

按照编程方式和逻辑功能的类型有以下三种:

①SRAM-查找表类型(Intel Xilinx)可反复编程

②反熔丝的多路开关类型FPGA(Actel)

③基于Flash的FPGA(Lattice)

3)查找表结构单元内部

4输入作为多路选择器的开关,输入D为1,下方无法输出;输入C为1,走上路;同理A,B也为两种情况,则4输入为16种可能。通过ABCD的值会选择输出RAM的值。

查找表实现可编程逻辑的原理:编程即就是要计算出RAM初始值。通过计算得知输入间的逻辑关系取出RAM的值给查找表。

一个N输入查找表(LUT)可以实现N个输入变量的任何逻辑功能,如与、或、非、异或等。输入多于N个的函数,方程必须分开用几个查找表(LUT)实现。下图,黑盒子即就是编程的sof文件。

4)可编程IO功能

①IO模块配有缓冲器和寄存器,可实现电平匹配、提高驱动能力,延时等功能。

②可实现单端IO和差分IO,差分IO有LVDS和LVPECL两种协议,电平和外部终端电路不一样。

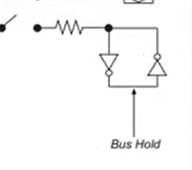

③IO电平驱动防过冲解决方案:加入分压电阻和齐纳二极管。下图加入

④兼容TTL和CMOS多种接口和电压标准(降低功耗)

⑤可配置为输入、输出、双向、三态、双速率等形式

⑥能降低功耗,提供适当的驱动电流,防止过冲和减少电源噪声

(3)可选扩展资源

①存储器资源(块RAM、分布式RAM)

②数字时钟管理单元(分/倍频、数字延迟、时钟锁定)

③算数运算单元(高速硬件乘法器、乘加器)

④高速串行IO接口

⑤特殊功能模块(PCIe、DDR等硬件IP核)

⑥微处理器(Cortex-M3、Cortex-A9、Cortex-A53、PowerPC)

(4)典型结构

数字时钟管理单元(管理时钟,对输入时钟分倍频):DLL与PLL,分别为数字与模拟的锁相环,PLL的精度高。

存储器资源(大容量存储器):Block Ram和M9K存储器

硬件乘法器:18*18的乘法器。

总结:时序分析与约束分析信号在FPGA内部从输入寄存器传输到输出寄存器时走过的每条路耗费的总共时间满足设置的主频时钟周期的要求,即就是保证信号从D触发器的输出到目的寄存器D触发器的输入耗费的时间要小于时钟周期,下一寄存器才能正确接收数据。

1176

1176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?