STM32F103RB系列芯片电源域分析

电源

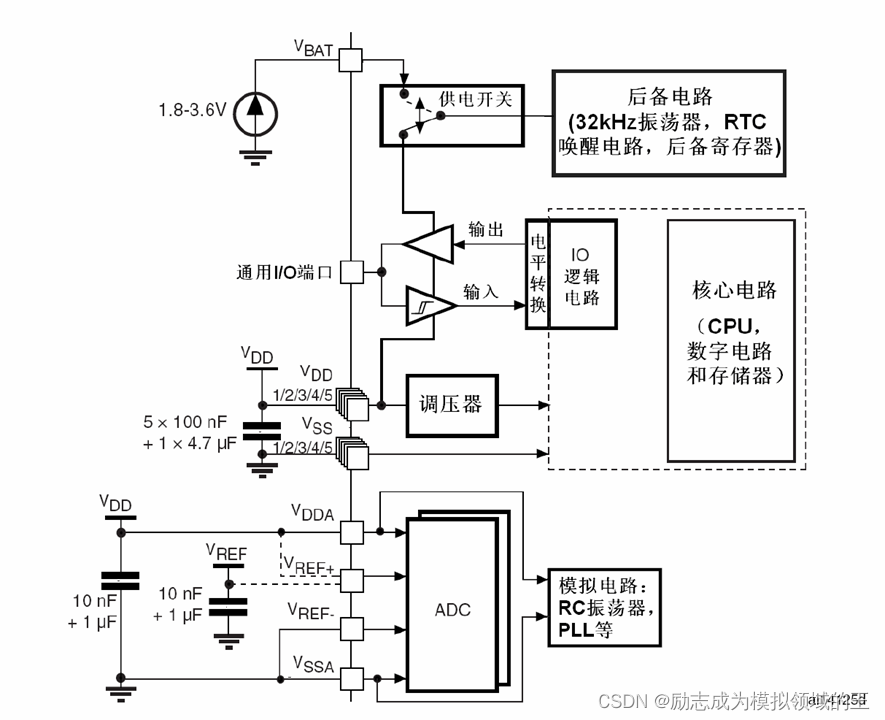

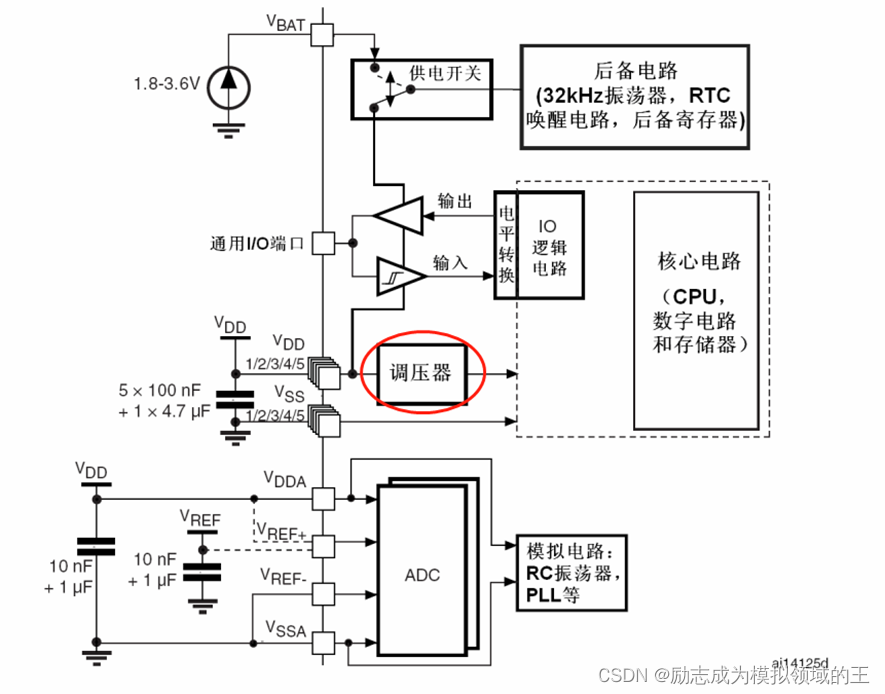

STM32F103xxx的供电方案框图如下:

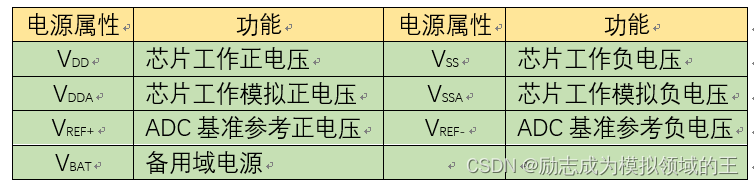

归类说明如下:

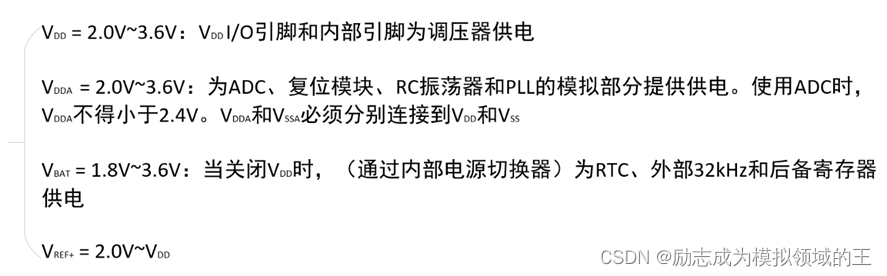

V_DD电源

V_DD为5组,即,V_DD1, V_DD2, V_DD4, V_DD4和V_DD5。该电源为同一电源,封装的时候从不同位置引出,目的提供可靠的电源完整性。

对于芯片内部的多组V_DD和V_SS,原因如下:

假设芯片中有一路V_DD,此时芯片内部V_DD的线路会很长,线路阻抗更大。且如果处于在高频的环境中,由感抗公式X_L (Ω)=2πfL可知,此时感抗会变大,阻碍电流的作用更强,所以此时整个电源网络都会异常。而多组的V_DD存在,相当于将不同线路的电感并联,减少了电感效应,使得电源网络更加稳定

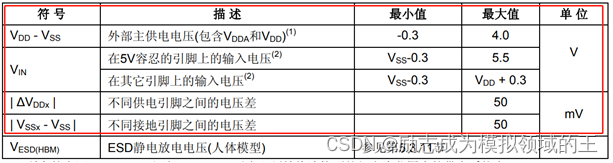

范围

输入范围为:-0.3V~4V(V_DD-V_SS);

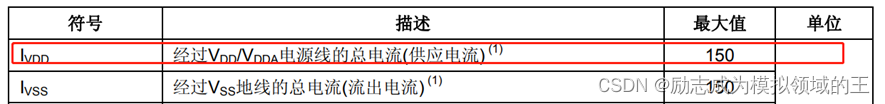

电流:经过V_DD和V_DDA电源线的总电流最大值为150mA;

∆|V_DDx |同供电引脚之间的电压差最大值为50mV。

由于|V_DDx |分布在芯片四周不同位置,所以在系统应用端进行布线时,布线的距离也会出现不同,进而导致布线阻抗不同,导致最终流入到|V_DDx |存在误差。所以有此项约束。

工作电压范围为:标准供电电压为2~3.6V;

如果供电范围在该范围之外,则可能会导致芯片部分功能失效,重启等非正常现象出现。

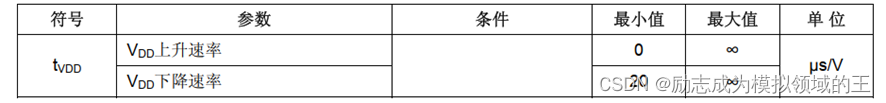

V_DD上升速率:0-无穷(μs/V),V_DD下降速率:20-无穷(μs/V)(需要注意的是,这里的单位是μs/V,和V/μs互为倒数,所以可以有:0~1/20V/μs,这里要求的是V_DD下降速率不能过快。当V_DD电压急剧下降时,电流急剧升高,可能导致芯片击穿或永久性损伤。

V_SS电源

V_SS为5组,即,V_SS1,V_SS2,V_SS3,V_SS4,V_SS5,作为芯片内部电源网络基准(芯片内部参考GND)。

不同接地引脚之间的电压差最大为50mV,即|V_SSx-V_SS |= 50mV。

多组V_SS的原因同多组V_DD。

V_DDA电源

对于V_DDA来讲,A = analog(译为模拟),主要为芯片内部模拟电路部分进行供电。其手册描述参数为模拟部分工作电压。

从使用端原理图设计(图1)上来讲,要求V_DDA必须连接V_DD,要|V_DD-V_DDA |之间最多有300mV的电压差(如果V_DDA和V_DD采用隔离滤波)。

V_DDA最大电流限制于(I_VDDA+I_VDD )_max=150mA。

范围

未使用ADC

2.0V~3.6V;

使用ADC

2.4V~3.6V。

V_DDA的前提使用条件为与V_DD保持相同。

作用域

ADC;

复位模块;

RC振荡器;

温度传感器;

PLL。

V_SSA电源

V_SSA为芯片内模拟部分的参考GND,供电方案中约束其必须与V_SS相连。

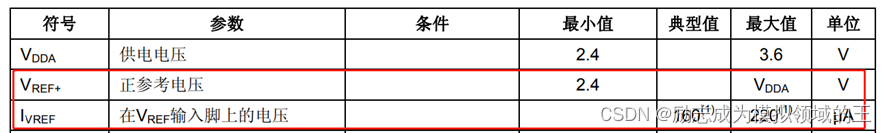

V_(REF+)电源

V_(REF+)为ADC的正向参考电压,且该输入只存在100脚以上的芯片(但是在TFBGA64封装上没有PC3,但提供了V_(REF+)引脚)。在VFQFPN36、LQFP48和LQFP64封装芯片中,V_(REF+)在内部直接连到V_DDA。

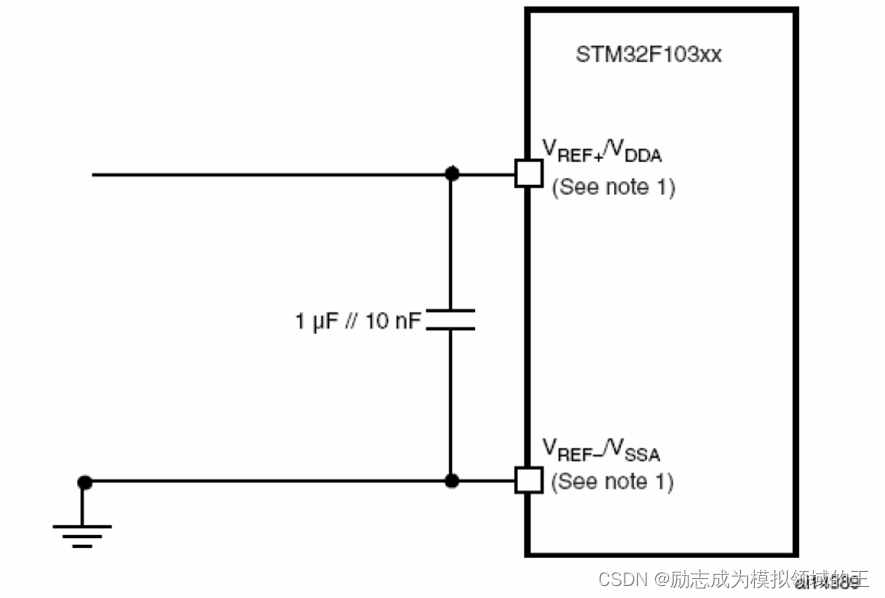

若在设计时采用独立基准电源,则该基准电源定义为V_REF,正电压连接10nF+1uF(10nF电容必须为好质量的瓷介质电容)去耦电容最终输入至V_(REF+)引脚。

若无独立基准电源,则V_(REF+)连接到V_DDA。

范围

电压范围:2.4V~ V_DDA;

测试电流最大值:220μA。

作用域

ADC转换。

V_(REF-)电源

V_(REF-)为ADC的负向参考电压,连接至V_SSA。且该输入只存在100脚以上的芯片。在VFQFPN36、LQFP48、TFBGA64和LQFP64封装芯片中,V_(REF-)在内部直接连到V_SSA。

V_BAT电源

V_BAT为备份部分工作电压。在系统中,在V_DD有效时该开关选择V_DD供电,否则由V_BAT引脚供电。需要注意的是,如果无备用供电,则必须把V_BAT和V_DD相连。

范围

工作条件:1.8V~3.6V。

作用域

RTC;

后备寄存器(10个16位寄存器)。

调压器

调压器的作用为将输入的VDD处理为1.8V供电,器件内部的1.8V域为CPU,数字电路和存储器

调压器支持三种工作模式,分别为:

(1) 主模式——main(MR)

在主模式下,用于系统正常的运行操作。

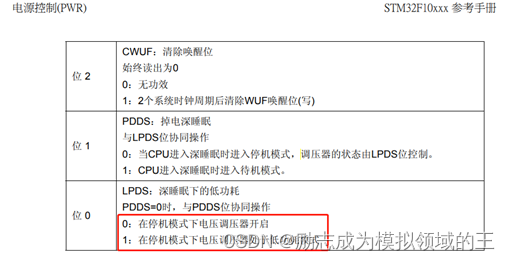

(2) 低功耗模式——low-power

低功耗模式是CPU的停机(Stop)模式下的其中一种设置(另外一种是主模式),该设置可以在PWR寄存器内进行配置。

当电压调节器处于low-power模式时,电压调节器会通过下调调压器的输出电压和调压器的时钟来减小功耗。

当CPU处于停机模式,在保持SRAM和寄存器的内容不丢失的情况下,可以产生最小的功耗。关断所有内部的1.8V供电PLL,HSI的RC振荡器和HSE的振荡器被关闭。

(3) 关断模式——power-down

在待机模式下可以达到最低的电能消耗。内部的电压调压器被关闭,因此所有内部1.8V部分的供电被切断;PLL、HSI的RC振荡器和HSE晶体振荡器也被关闭;进入待机模式后,SRAM和寄存器的内容将消失,但后备寄存器的内容仍然保留,待机电路仍工作。

调压器的处于何种模式由CPU的模式和实际功耗设计所决定。

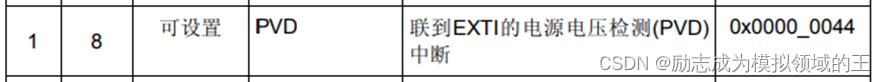

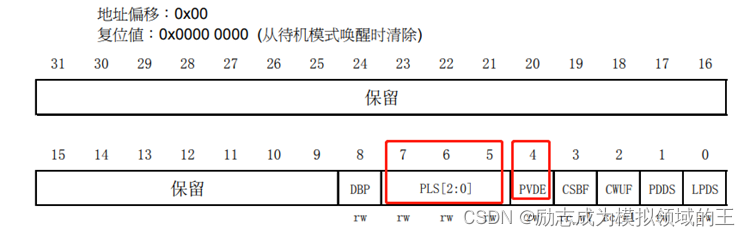

可编程的电压检测器

芯片中有一个可编程电压监测器(PVD),监视V_DD/V_DDA供电并于阈值V_PVD比较,当V_DD低于或高于阈值V_PVD时产生中断(前提使能中断),中断处理程序可以发出警告信息或将芯片转入安全模式。(PVD功能需要通过程序开启)。

其中,EXTI线16连接到PVD输出。

V_PVD的触发条件可以通过配置电源控制寄存器(PWR_CR)实现。

通过配置bit4 PVDE可以实现是否开启电压检测器:

当PVDE = 0时,则表示禁止开启电压检测器;

当PVDE = 1时,则表示使能电压检测器。

PLS[2:0] =000

(上边沿)

此时V_PVD=2.1V~2.26V,典型值为2.18V。

(下边沿)

此时V_PVD=2V~2.16V,典型值为2.08V。

PLS[2:0] =001

(上边沿)

此时V_PVD=2.19V~2.37V,典型值为2.28V。

(下边沿)

此时V_PVD=2.09V~2.27V,典型值为2.18V。

PLS[2:0] =010

(上边沿)

此时V_PVD=2.28V~2.48V,典型值为2.38V。

(下边沿)

此时V_PVD=2.18V~2.38V,典型值为2.28V。

PLS[2:0] =011(上升沿)

(上边沿)

此时V_PVD=2.38V~2.58V,典型值为2.48V。

(下边沿)

此时V_PVD=2.28V~2.48V,典型值为2.38V。

PLS[2:0] =100

(上边沿)

此时V_PVD=2.28V~2.48V,典型值为2.38V。

(下边沿)

此时V_PVD=2.37V~2.59V,典型值为2.48V。

PLS[2:0] =101

(上边沿)

此时V_PVD=2.57V~2.79V,典型值为2.68V。

(下边沿)

此时V_PVD=2.47V~2.69V,典型值为2.58V。

PLS[2:0] =110

(上边沿)

此时V_PVD=2.66V~2.9V,典型值为2.78V。

(下边沿)

此时V_PVD=2.56V~2.8V,典型值为2.68V。

PLS[2:0] =111

(上边沿)

此时V_PVD=2.76V~3V,典型值为2.88V。

(下边沿)

此时V_PVD=2.66V~2.9V,典型值为2.78V。

电压检测电平存在电压迟滞:V_PVDhyst=100mV。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?