Module

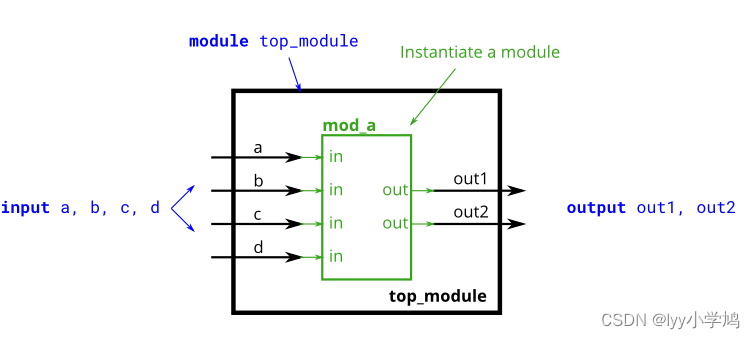

By now, you're familiar with a module, which is a circuit that interacts with its outside through input and output ports. Larger, more complex circuits are built by composing bigger modules out of smaller modules and other pieces (such as assign statements and always blocks) connected together. This forms a hierarchy, as modules can contain instances of other modules.

module top_module(

input a,

input b,

output out

);

mod_a mod_a0

(

.in1(a),

.in2(b),

.out(out)

);

endmodule

这个题,前面的描述一大堆,但是靠近代码模块的要求又说的模模糊糊,所以最初一时间摸不清楚要干啥

Module pos

This problem is similar to the previous one (module). You are given a module named mod_a that has 2 outputs and 4 inputs, in that order. You must connect the 6 ports by position to your top-level module's ports out1, out2, a, b, c, and d, in that order.

You are given the following module:

module mod_a ( output, output, input, input, input, input );

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a inst(out1,out2,a,b,c,d);

endmodule

Module name

This problem is similar to module. You are given a module named mod_a that has 2 outputs and 4 inputs, in some order. You must connect the 6 ports by name to your top-level module's ports:

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a inst(

.out1(out1),

.out2(out2),

.in1(a),

.in2(b),

.in3(c),

.in4(d)

);

endmodule

Module shift

You are given a module my_dff with two inputs and one output (that implements a D flip-flop). Instantiate three of them, then chain them together to make a shift register of length 3. The clk port needs to be connected to all instances.

The module provided to you is: module my_dff ( input clk, input d, output q );

Note that to make the internal connections, you will need to declare some wires. Be careful about naming your wires and module instances: the names must be unique.

module top_module ( input clk, input d, output q );

wire q1,q2;

my_dff inst1(clk,d,q1);

my_dff inst2(clk,q1,q2);

my_dff inst3(clk,q2,q);

endmoduleModule shift8

This exercise is an extension of module_shift. Instead of module ports being only single pins, we now have modules with vectors as ports, to which you will attach wire vectors instead of plain wires. Like everywhere else in Verilog, the vector length of the port does not have to match the wire connecting to it, but this will cause zero-padding or trucation of the vector. This exercise does not use connections with mismatched vector lengths.

You are given a module my_dff8 with two inputs and one output (that implements a set of 8 D flip-flops). Instantiate three of them, then chain them together to make a 8-bit wide shift register of length 3. In addition, create a 4-to-1 multiplexer (not provided) that chooses what to output depending on sel[1:0]: The value at the input d, after the first, after the second, or after the third D flip-flop. (Essentially, sel selects how many cycles to delay the input, from zero to three clock cycles.)

The module provided to you is: module my_dff8 ( input clk, input [7:0] d, output [7:0] q );

The multiplexer is not provided. One possible way to write one is inside an always block with a case statement inside

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0]q1,q2,q3;

my_dff8 inst1(clk,d,q1);

my_dff8 inst2(clk,q1,q2);

my_dff8 inst3(clk,q2,q3);

always@(*)begin

case(sel)

2'd0: q=d;

2'd1: q=q1;

2'd2: q=q2;

2'd3: q=q3;

endcase

end

endmodule

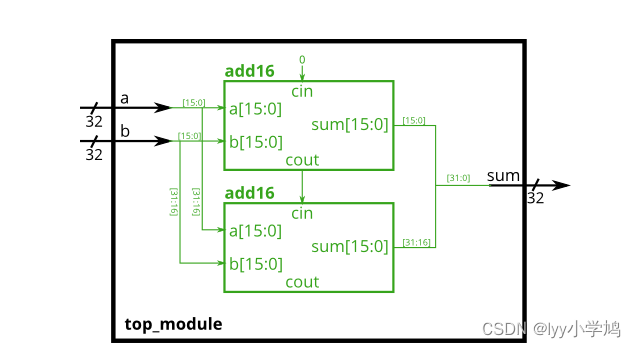

Module add

You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result, after receiving the carry-out from the first adder. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored), but the internal modules need to in order to function correctly. (In other words, the add16 module performs 16-bit a + b + cin, while your module performs 32-bit a + b).

Connect the modules together as shown in the diagram below. The provided module add16 has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout_l,cout_h;

add16 inst1(a[15:0],b[15:0],1'b0,sum[15:0],cout_l);

add16 inst2(a[31:16],b[31:16],cout_l,sum[31:16],cout_h );

endmodule

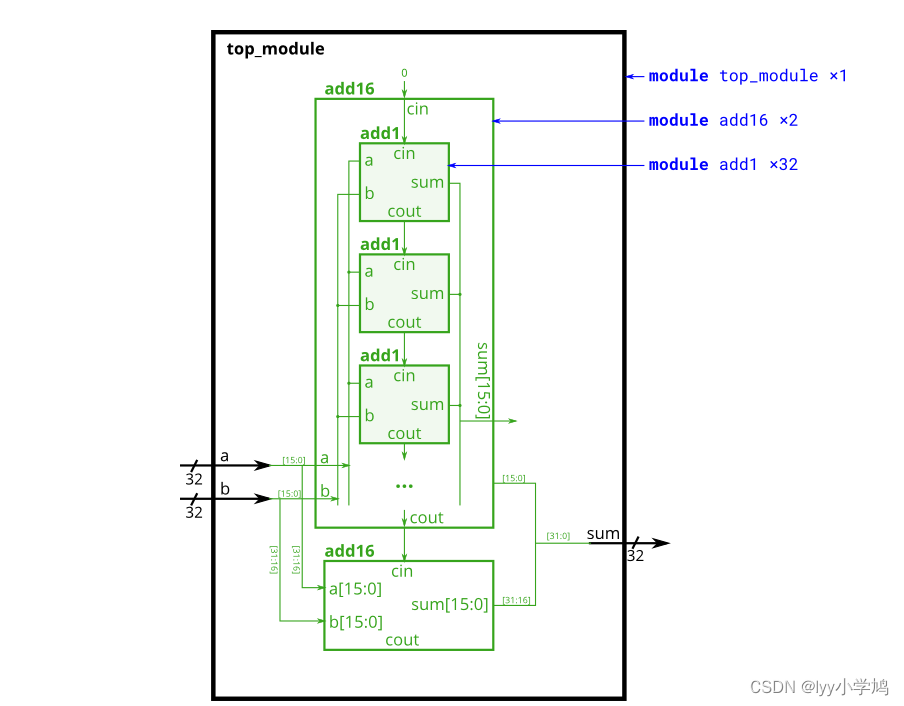

Module fadd

In summary, there are three modules in this design:

top_module— Your top-level module that contains two of...add16, provided — A 16-bit adder module that is composed of 16 of...add1— A 1-bit full adder module.

If your submission is missing a , you will get an error message that says . module add1Error (12006): Node instance "user_fadd[0].a1" instantiates undefined entity "add1"

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout_l,cout_h;

add16 inst1(a[15:0],b[15:0],1'b0,sum[15:0],cout_l);

add16 inst2(a[31:16],b[31:16],cout_l,sum[31:16],cout_h );

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

assign sum = a^b^cin;

assign cout = (a&b)|((a^b)&cin);

endmodule

在这道题中,题目的意思是已经给出了addr16,只需要例化连接就可以,但是一位全加器得到代码需要自己写,所以代码段会出现两个module模块。

2611

2611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?