2.3.1、Modules

Module

Solution:

module top_module ( input a, input b, output out );

//模块名+例化名 (按顺序写出I/O口)

//mod_a mod (a, b, out);

//模块名+例化名 (.例化名称(例化地址), .(例化名称(例化地址)))

mod_a mod (.in1(a), .in2(b), .out(out));

endmoduleSubmit:

2.3.2、Module pos

This problem is similar to the previous one (module). You are given a module named

mod_athat has 2 outputs and 4 inputs, in that order. You must connect the 6 ports by position to your top-level module's portsout1,out2,a,b,c, andd, in that order.You are given the following module:

module mod_a ( output, output, input, input, input, input );

Solution:

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

//注意的是此题目输入都为in,输出为out,不可以使用直接例化

mod_a mod (out1, out2, a, b, c, d);

endmoduleSubmit:

2.3.3、Module name

This problem is similar to module. You are given a module named

mod_athat has 2 outputs and 4 inputs, in some order. You must connect the 6 ports by name to your top-level module's ports:

Port in mod_aPort in top_moduleoutput out1out1output out2out2input in1ainput in2binput in3cinput in4dYou are given the following module:

module mod_a ( output out1, output out2, input in1, input in2, input in3, input in4);

Solution:

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a mod (.out1(out1), .out2(out2), .in1(a), .in2(b), .in3(c), .in4(d));

endmoduleSubmit:

2.3.4、Module shift

You are given a module

my_dffwith two inputs and one output (that implements a D flip-flop). Instantiate three of them, then chain them together to make a shift register of length 3. Theclkport needs to be connected to all instances.The module provided to you is:

module my_dff ( input clk, input d, output q );Note that to make the internal connections, you will need to declare some wires. Be careful about naming your wires and module instances: the names must be unique.

Solution:

module top_module ( input clk, input d, output q );

//wrie 定义线性变量用于连接

wire temp1, temp2;

my_dff mod1 (.q(temp1), .clk(clk), .d(d));

my_dff mod2 (.q(temp2), .clk(clk), .d(temp1));

my_dff mod3 (.q(q), .clk(clk), .d(temp2));

endmoduleSubmit:

2.3.5、Module shift

The module provided to you is:

module my_dff8 ( input clk, input [7:0] d, output [7:0] q );The multiplexer is not provided. One possible way to write one is inside an

alwaysblock with acasestatement inside. (See also: mux9to1v)

Solution:

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] q1, q2, q3;

my_dff8 mod1 (.clk(clk), .d(d), .q(q1));

my_dff8 mod2 (.clk(clk), .d(q1), .q(q2));

my_dff8 mod3 (.clk(clk), .d(q2), .q(q3));

always@(*)begin

case(sel)

0 : q = d;

1 : q = q1;

2 : q = q2;

3 : q = q3;

endcase

end

endmoduleSubmit:

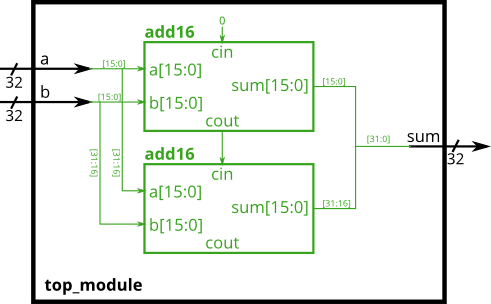

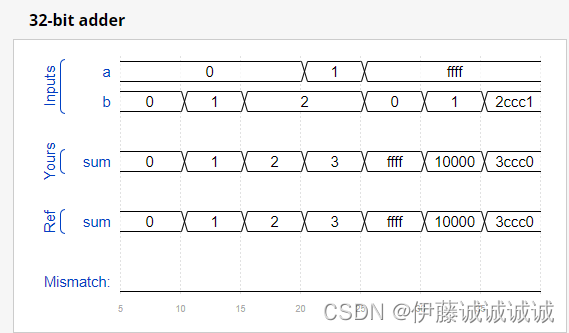

2.3.6、Module add

You are given a module

add16that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result, after receiving the carry-out from the first adder. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored), but the internal modules need to in order to function correctly. (In other words, theadd16module performs 16-bit a + b + cin, while your module performs 32-bit a + b).Connect the modules together as shown in the diagram below. The provided module

add16has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

Solution:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire temp;

add16 add16_1 (.cin(0), .a(a [15:0]), .b(b [15:0]), .cout(temp), .sum(sum [15:0]));

add16 add16_2 (.cin(temp), .a(a [31:16]), .b(b[31:16]), .cout(), .sum(sum [31:16]));

endmoduleSubmit:

3359

3359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?