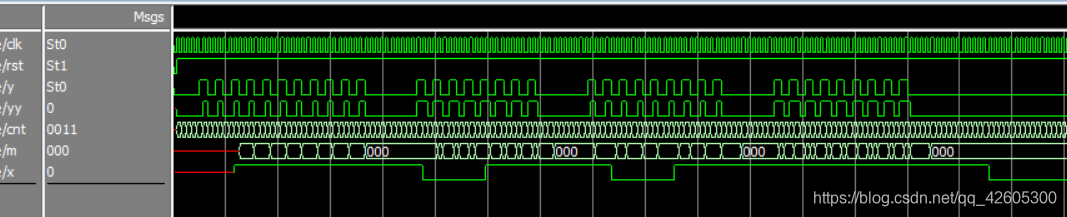

一、2ASK调制与解调

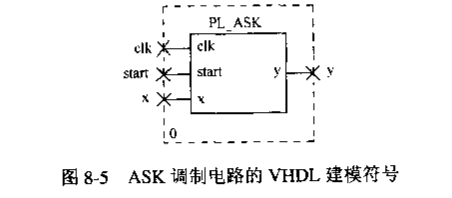

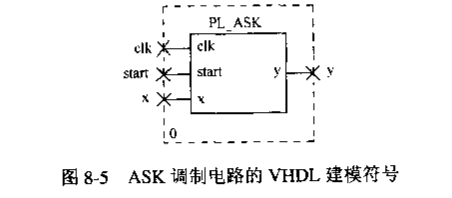

module modulate_2ASK(clk , rst , x, y);

input clk,rst;

input x;

reg [1:0] cnt;

reg carry = 0;

output y; //wire类型

//第一步:分频得到载波信号序列:carry,(4分频)

always@(posedge clk)

begin

if(!rst) //rst低电平有效:置位为0可以重置cnt、carry初值

begin

cnt <= 0;

carry <= 0;

end

else

begin //高电平:3、0;低电平:1、2

if(cnt == 3 ) //先判断cnt是否为3: 令carry =1

begin

cnt <= 0;

carry <= 1;

end

else if(cnt == 0) //0: 令carry = 1

begin

carry <= 1;

cnt <= cnt + 1;

end

else //1、2: 令carry = 0

begin

cnt = cnt + 1;

carry <= 0;

end

end

end

//第二步:基带信号x、载波信号carry,&&

assign y = x && carry;

endmodule

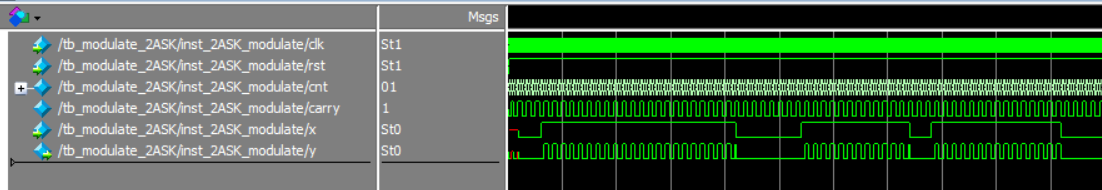

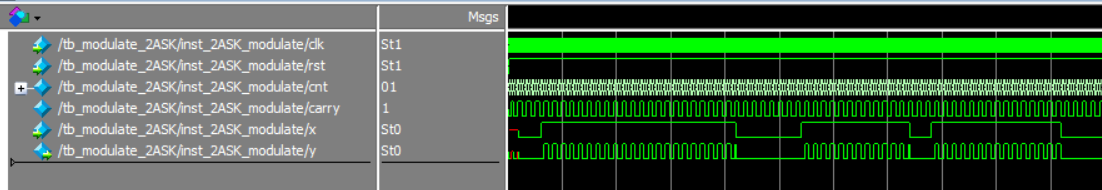

`timescale 100ns/1ps //time scale = 0.1us

module TB_ASK_Modulate();

reg CLK, START, X;

//parameter initTime = 30; //start after initTime

parameter period = 2;

modulate_2ASK Obj(.clk(CLK), .rst(START), .x(X));

/* period = 0.2us */

initial

begin

CLK = 0;

//#initTime;

forever

#(period/2) CLK = ~CLK;

end

/* ASK_CLK */

initial

begin

START=0;

@(posedge CLK);

START=1;

end

/* testbench */

initial

begin

X=0;

#50 X=1; // 1 delay for 5us

#50 X=0; // 0 delay for 5us

#50 X=1; // 1 delay for 10us

#100 X=0; // 0 delay for 10us

#100 X=1; // 1 delay for 5us

#50 X=0; // 0 delay for 10us

#100 X=1; // 1 delay for 5us

#50 X=0; //0 delay forever

end

endmodule

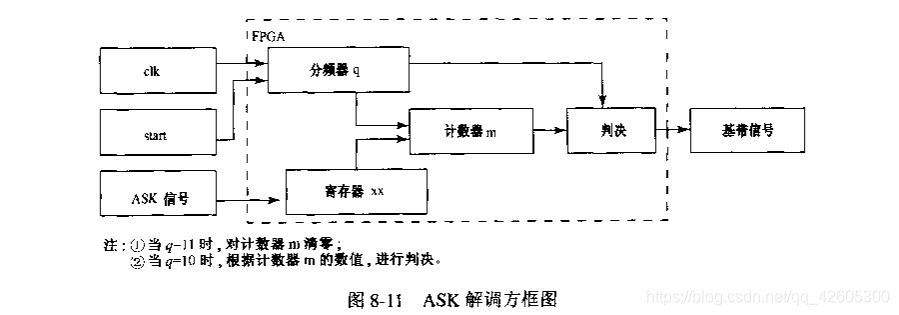

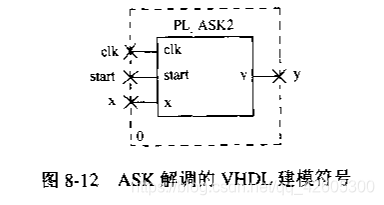

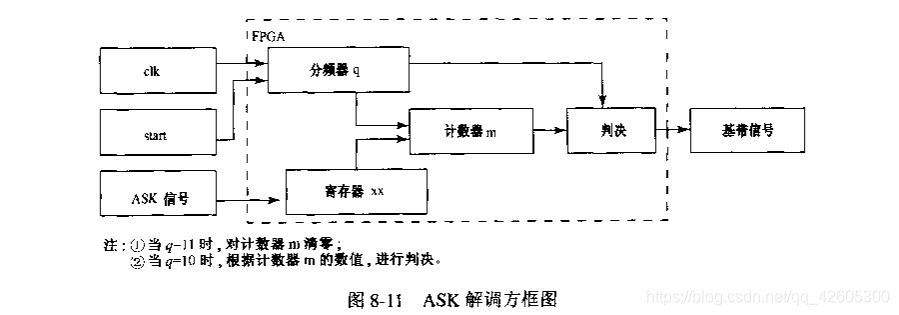

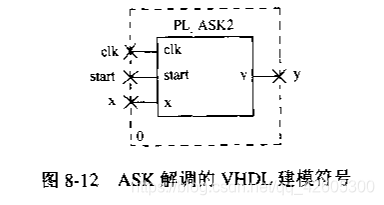

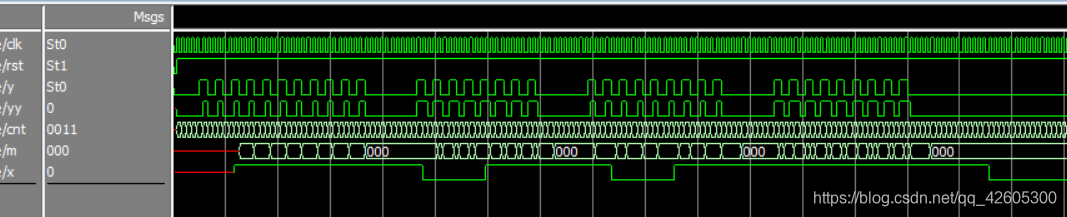

module demodulate_2ASK( clk,rst , y, x );

input clk,rst;

input y; //调制信号

output reg x; //解调后信号,原始基带信号

reg [3:0] cnt;

reg [2:0] m; //记录采样过程中"1"的个数

reg yy; //yy

//计数器 0 ~ 11,一直循环累加

always@(posedge clk)

begin

yy <= y;

if(!rst)

begin

cnt <= 0;

end

else

begin

if(cnt == 11)

cnt <= 0;

else

cnt <= cnt +1; // 000、001、···、007

end

end

//采样判决

always@(posedge clk)

begin

if(cnt == 11) //cnt=11,m重置为0

begin

m <= 0;

end

else

begin

if(cnt == 10) //cnt=11,开始采样判决

begin

if(m <= 2)

x <= 0;

else //只要 m 超过 2, 就判决为1

x <= 1;

end

else if(yy == 1)

m <= m + 1; //cnt:0 ~ 5,都在累加

end

end

endmodule

`timescale 100ns/1ps //time scale = 0.1us

module TB_ASK_Demodulate();

reg CLK, START, X;

//parameter initTime = 30; //start after initTime

parameter period = 2;

demodulate_2ASK Obj(.clk(CLK), .rst(START), .y(X));

/* period = 0.2us */

initial

begin

CLK = 0;

//#initTime;

forever

#(period/2) CLK = ~CLK;

end

/* ASK_CLK */

initial

begin

START=0;

@(posedge CLK);

START=1;

end

/* testbench */

initial

begin

X=0;

#50 X=1; // 1 delay for 5us

#50 X=0; // 0 delay for 5us

#50 X=1; // 1 delay for 10us

#100 X=0; // 0 delay for 10us

#100 X=1; // 1 delay for 5us

#50 X=0; // 0 delay for 10us

#100 X=1; // 1 delay for 5us

#50 X=0; //0 delay forever

end

endmodule

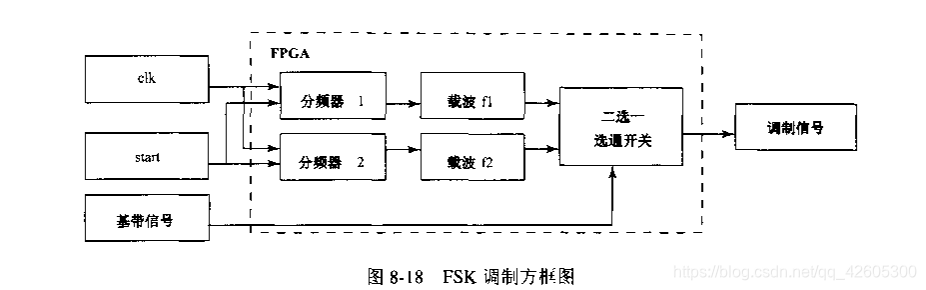

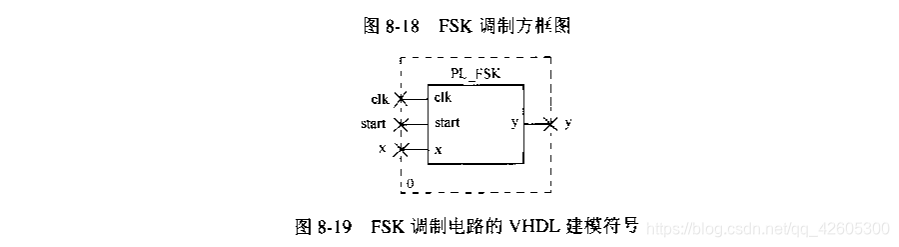

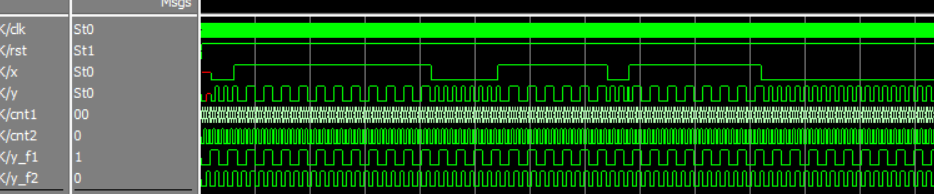

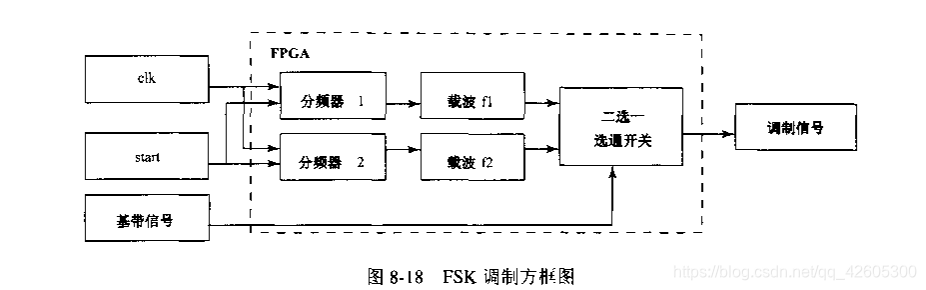

二、2FSK调制解调

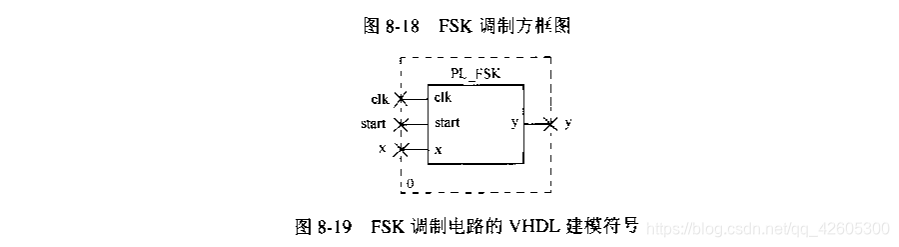

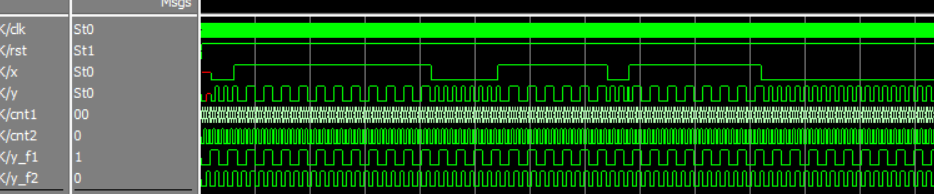

module modulate_2FSK(clk,rst , x, y);

input clk, rst;

input x;

output y;

reg [1:0] cnt1;

reg cnt2;

reg y_f1, y_f2; // 2个不同频率的信号

// 利用2位计数器cnt1实现4分频,分频之后的信号为y_f1

always@(posedge clk or negedge rst)

begin

if(!rst) // rst是低电平有效

begin

cnt1 <= 0;

y_f1 <= 0;

end

else

begin

if(cnt1 == 2'b11) //0、1、2、3、 0、1、2、3 、···

begin

cnt1 <= 0;

y_f1 <= ~y_f1;

end

else

cnt1 <= cnt1 + 1;

end

end

// 利用1位计数器cnt2实现2分频,分频之后的信号为f2

always@(posedge clk or negedge rst)

begin

if(!rst) //rst是低电平有效

begin

cnt2 <= 0;

y_f2 <= 0;

end

else

begin

if(cnt2 == 2'b1)

begin

cnt2 <= 0;

y_f2 <= ~y_f2;

end

else

cnt2 <= cnt2 + 1;

end

end

assign y = (x==1)? y_f1 : y_f2;

endmodule

module demodulate_2FSK(clk,rst , x, y);

input clk, rst;

input y;

output reg x;

reg clk1;

reg temp;

reg [3:0] cnt1;

reg [3:0] cnt2;

//计数器,cnt1计数变量:记录clk下调制信号‘0’电平个数

always@(posedge clk or negedge rst)

begin

if(!rst)

cnt1 <= 0;

else

begin

if(!y)

cnt1 <= cnt1 + 1;

else

cnt1 <= 0;

end

end

//比较器,temp变量:记录‘0’电平个数大于6的数量,采样

always@(posedge clk or negedge rst)

begin

if(!rst)

temp <= 0;

else

begin

if(cnt1 > 6) //若clk时钟下调制信号中的‘1’电平个数大于6

temp <= 1; //temp置为‘1’

else

temp <= 0;

end

end

//20分频作为采样频率

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

cnt2 <= 0;

clk1 <= 0;

end

else

begin

if(cnt2 == 9)

begin

clk1 <= ~clk1;

cnt2 <= 0;

end

else

cnt2 <= cnt2 + 1;

end

end

//调制信号是在clk1的上升沿下的temp状态

always@(posedge clk1 or negedge rst)

begin

if(!rst)

x <= 0;

else

x <= temp;

end

endmodule

本文深入探讨了2ASK和2FSK两种数字调制解调技术的实现原理及Verilog源代码设计。从调制信号生成到解调过程,详细解析了如何通过计数器和采样判决实现信号的正确传输与接收,适用于嵌入式系统与通信领域的工程师和技术人员。

本文深入探讨了2ASK和2FSK两种数字调制解调技术的实现原理及Verilog源代码设计。从调制信号生成到解调过程,详细解析了如何通过计数器和采样判决实现信号的正确传输与接收,适用于嵌入式系统与通信领域的工程师和技术人员。

1767

1767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?