主程序:

module led_flash(

//端口列表

Clk50M,

Rst_n,

led

);

//端口定义

input Clk50M;

input Rst_n;

output [3:0]led;

reg [24:0]cnt;

parameter CNT_MAX = 25'd24_999_999; //定义参数

always@(posedge Clk50M or negedge Rst_n)

if(!Rst_n)

cnt <= 25'd0; //非阻塞赋值方式

else if(cnt == CNT_MAX)

cnt <= 25'd0;

else

cnt <= cnt + 1'b1;

// always@(posedge Clk50M or negedge Rst_n)

// if(!Rst_n)

// led <= 4'b1111;

// else if(cnt == CNT_MAX)

// led <= ~led;

// else

// led <= led;

reg [3:0]led_r;

// always@(posedge Clk50M or negedge Rst_n)

// if(!Rst_n)

// led_r <= 4'b0001;

// else if(cnt == CNT_MAX)begin

// if(led_r == 4'b1000)

// led_r <= 4'b0001;

// else

// led_r <= led_r << 1;

// end

// else

// led_r <= led_r;

always@(posedge Clk50M or negedge Rst_n)

if(!Rst_n)

led_r <= 4'b0001;

else if(cnt == CNT_MAX)

led_r <= {led_r[2:0],led_r[3]};

else

led_r <= led_r;

assign led = ~led_r;

endmodule

测试程序:

`timescale 1ns/1ns

`define clock_period 20

module led_flash_tb;

reg Clk50M;

reg Rst_n;

wire [3:0]led;

// led_flash

// #(

// .CNT_MAX(25'd249)

// )

// led_flash0(

// .Clk50M(Clk50M),

// .Rst_n(Rst_n),

// .led(led)

// );

led_flash led_flash0(

.Clk50M(Clk50M),

.Rst_n(Rst_n),

.led(led)

);

//生成50M时钟信号

initial Clk50M = 1;

always #(`clock_period/2) Clk50M = ~Clk50M;

initial begin

Rst_n = 0;

#(`clock_period*20 + 1) Rst_n = 1;

#(`clock_period*25000000 +1);

$stop;

end

endmodule

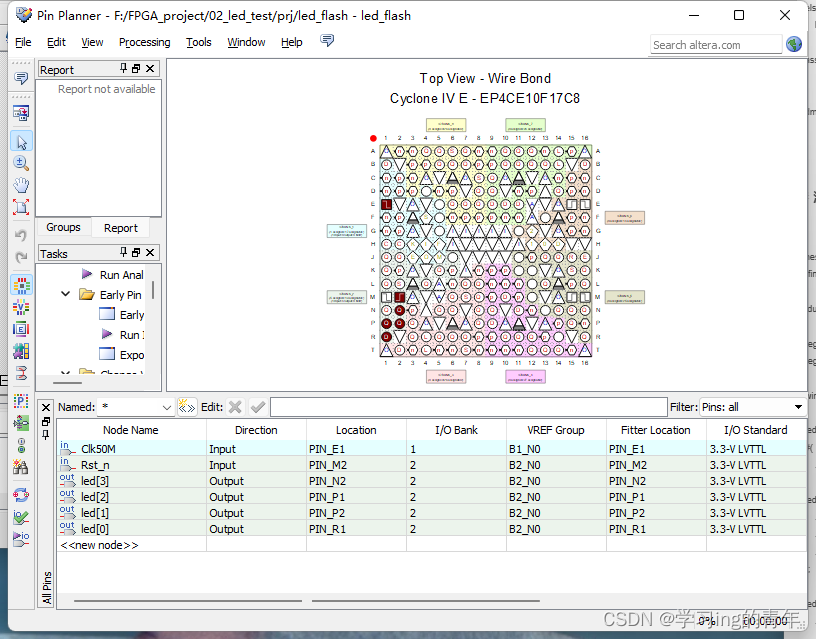

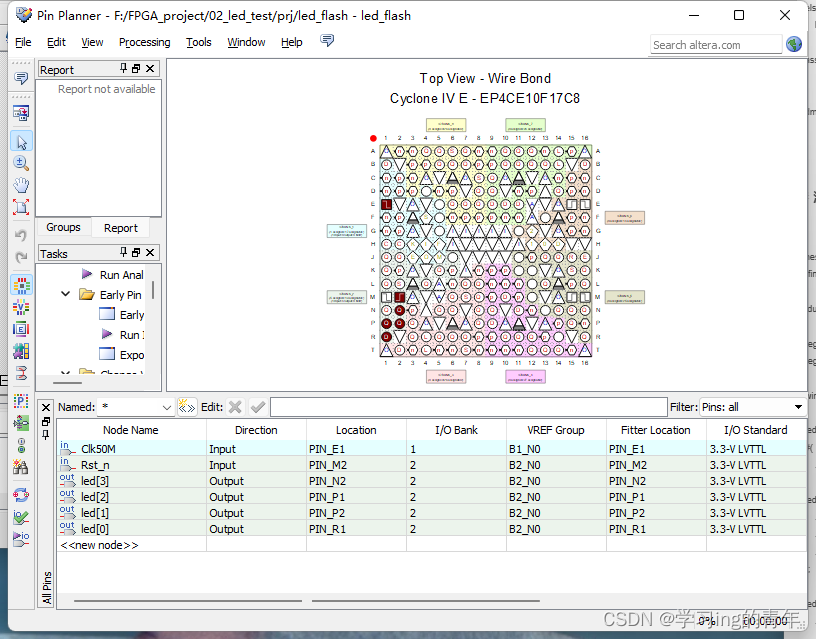

引脚定义:

1048

1048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?