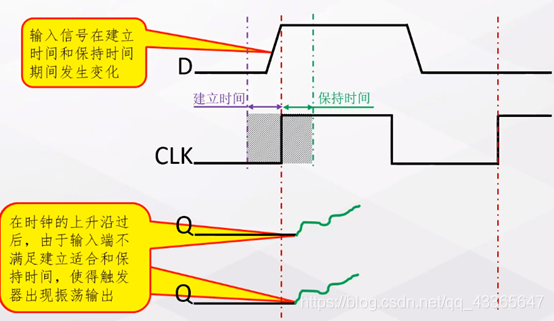

建立时间和保持时间:

建立时间:在有效的时钟沿到来之前,输入端的输入信号需要保持稳定不变的最小时间

保持时间:在有效的时钟沿到来之后,输入端的输入信号需要保持稳定不变的最小时间

如果不满足建立时间和保持时间的要求,电路就会进入亚稳态。

建立时间和保持时间由工艺决定。

如果触发器的恢复能力较强,可以在一个时钟周期之内恢复稳定的输出,但是不能确定是稳定在0上还是1上,而是一个与D端无关的随机值。

如果FF的恢复能力较弱,无法在一个时钟周期之内恢复稳定的输出,会在下一个有效的时钟沿时仍处于振荡状态。即这种无用的状态还会传递到下一级电路中去,导致后级的电路也会出现亚稳态问题。这种振荡状态称为亚稳态,亚稳态的影响是灾难性的。

同步设计可以使用STA来保持时序正确。

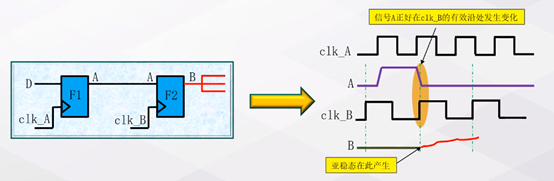

但是,芯片的功能模块越来越多,而且需要和外界的各种设备进行通讯,这样就意味着芯片内部的时钟需要和不同频率的时钟协同工作,它们之间的相位关系也是随机的,所以就不能使用STA方法来分析电路。这些不同时钟的模块之间的信号传输将产生CDC(跨时钟域)问题。

由CDC所引起的问题主要由以下几种:

1、 电路出现亚稳态:要确保可能产生的亚稳态对设计的功能没有错误的影响

2、 数据收敛:要确保一组相关联的同步信号在经过不同的路径之后可以在某一个相同的时钟周期正确的到达另一个时钟域。

3、 多路扇出:一个信号在跨时钟域后出现多个fanout,要确保后续的逻辑得到的值是相同的。

4、 数据丢失:前级时钟比后级的块,要确保该时钟保持足够长的时间以便被另一个石中玉的输入端正确的捕获到。如果这个信号出现的时间太短,就会出现数据丢失。

5、 异步复位:当异步复位信号在释放的时候,处理不当会导致后续电路出现亚稳态。

【Metastability】

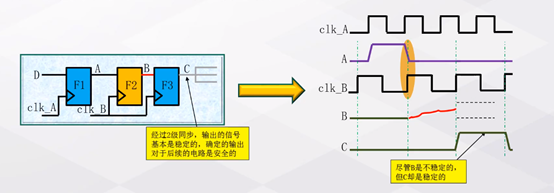

使用两级FF来进行信号同步。

经过F3的同步之后,C出现亚稳态的几率会很小。

(C端的结果与A端没有必然的联系)。

【数据收敛】

建立时间和保持时间:建立时间:在有效的时钟沿到来之前,输入端的输入信号需要保持稳定不变的最小时间保持时间:在有效的时钟沿到来之后,输入端的输入信号需要保持稳定不变的最小时间如果不满足建立时间和保持时间的要求,电路就会进入亚稳态。建立时间和保持时间由工艺决定。如果触发器的恢复能力较强,可以在一个时钟周期之内恢复稳定的输出,但是不能确定是稳定在0上还是1上,而是一个与D端无关的随机值。如...

建立时间和保持时间:建立时间:在有效的时钟沿到来之前,输入端的输入信号需要保持稳定不变的最小时间保持时间:在有效的时钟沿到来之后,输入端的输入信号需要保持稳定不变的最小时间如果不满足建立时间和保持时间的要求,电路就会进入亚稳态。建立时间和保持时间由工艺决定。如果触发器的恢复能力较强,可以在一个时钟周期之内恢复稳定的输出,但是不能确定是稳定在0上还是1上,而是一个与D端无关的随机值。如...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2520

2520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?