使用Quartus 18.1制作半(全)加器以及时序仿真

博客参考科学出版社《EDA技术使用教程》–Verilog HDL版(第六版)

软件使用Quartus18.1,仿真软件是ModelSim

第一节实验课老师就让我们跟着做半加器和全加器的时序仿真,具体操作步骤是书上第四章的内容,进度有点太快了,老师说让我们好好做笔记,我就先把操作步骤写下来,免得以后忘记了。

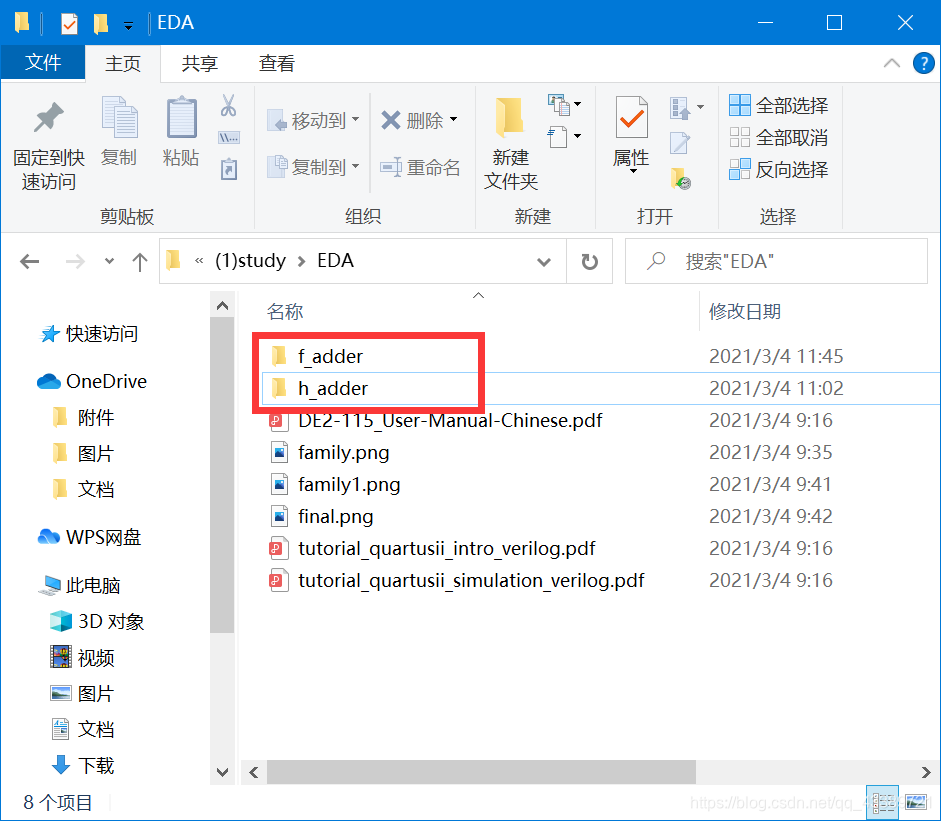

步骤一:建立文件夹

创建文件夹,在不同于安装目录的地方建文件夹,文件夹名字最好能表达此项目的含义。

我这里是full adder 全加器和half adder 半加器的英文简写。

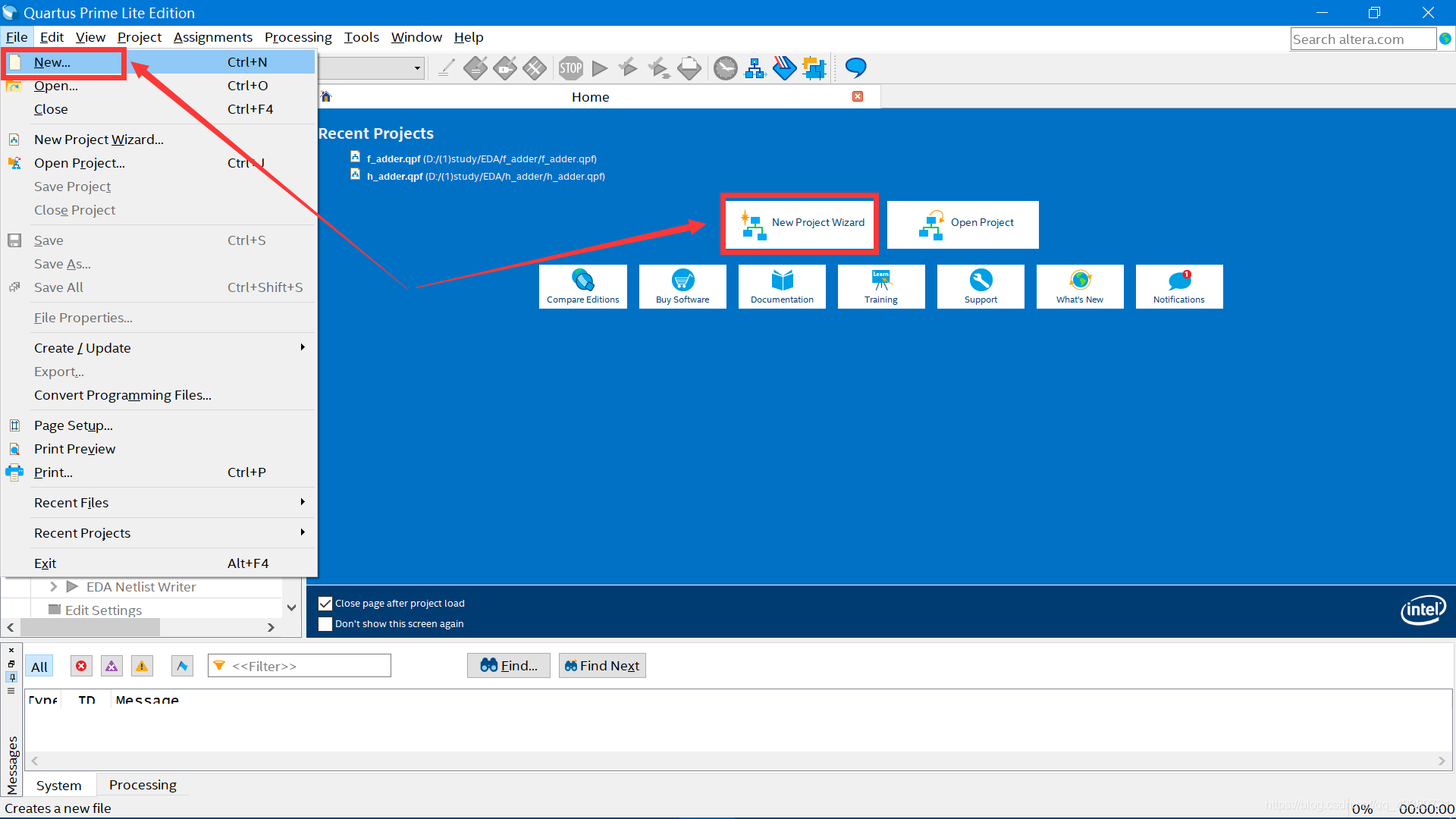

步骤二:创建工程

两个地方可以新建文件,点击新建之后它会出来新项目向导,也就是New Project Wizard,第一页跳过。

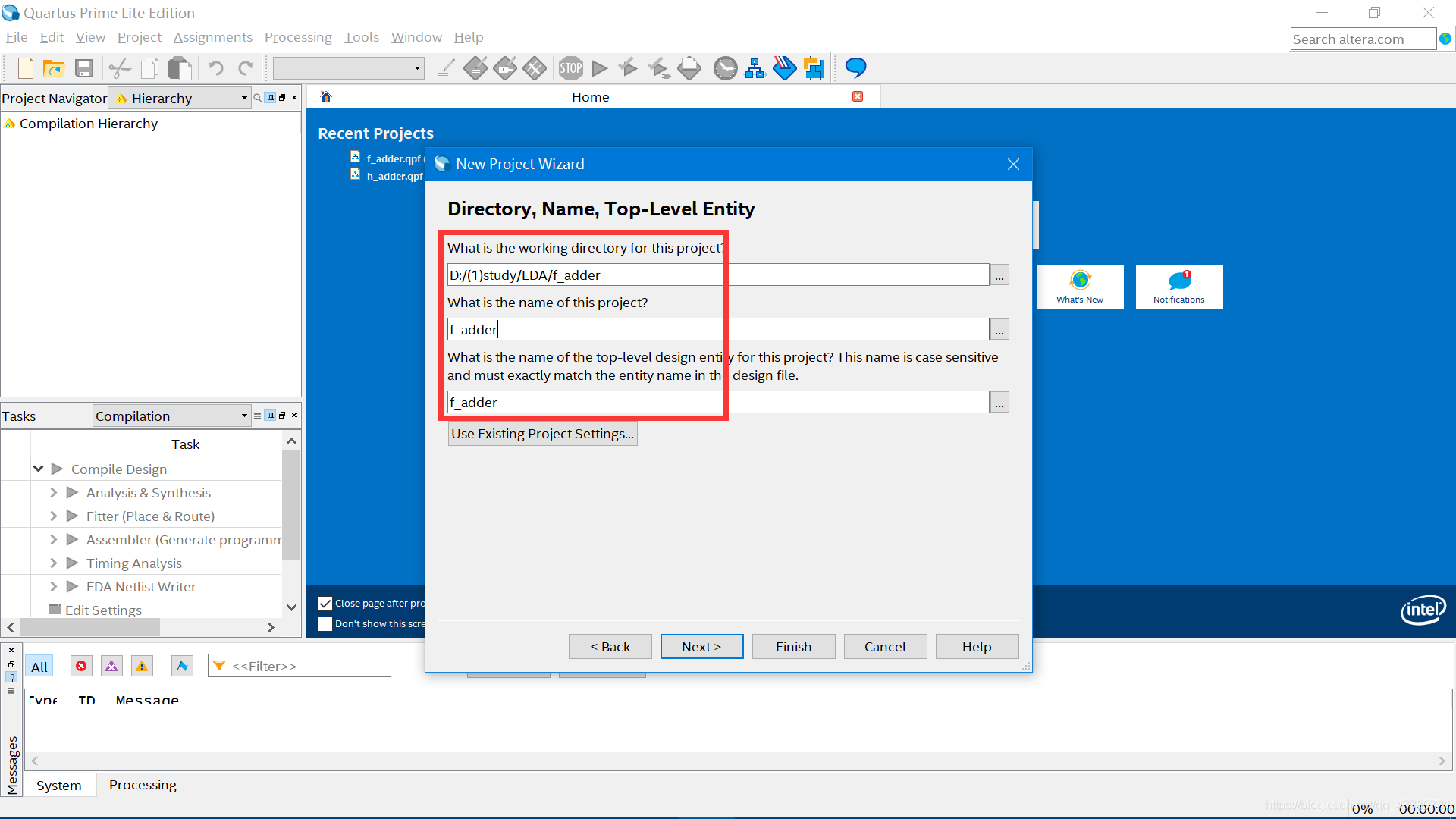

选择刚刚建的文件夹,第二行就跟文件夹名字一样就可以了,第三行会自己出来跟第二行一样的名字,不用管,下一步选择默认的空工程 Empty Project,再下一步直接跳过。

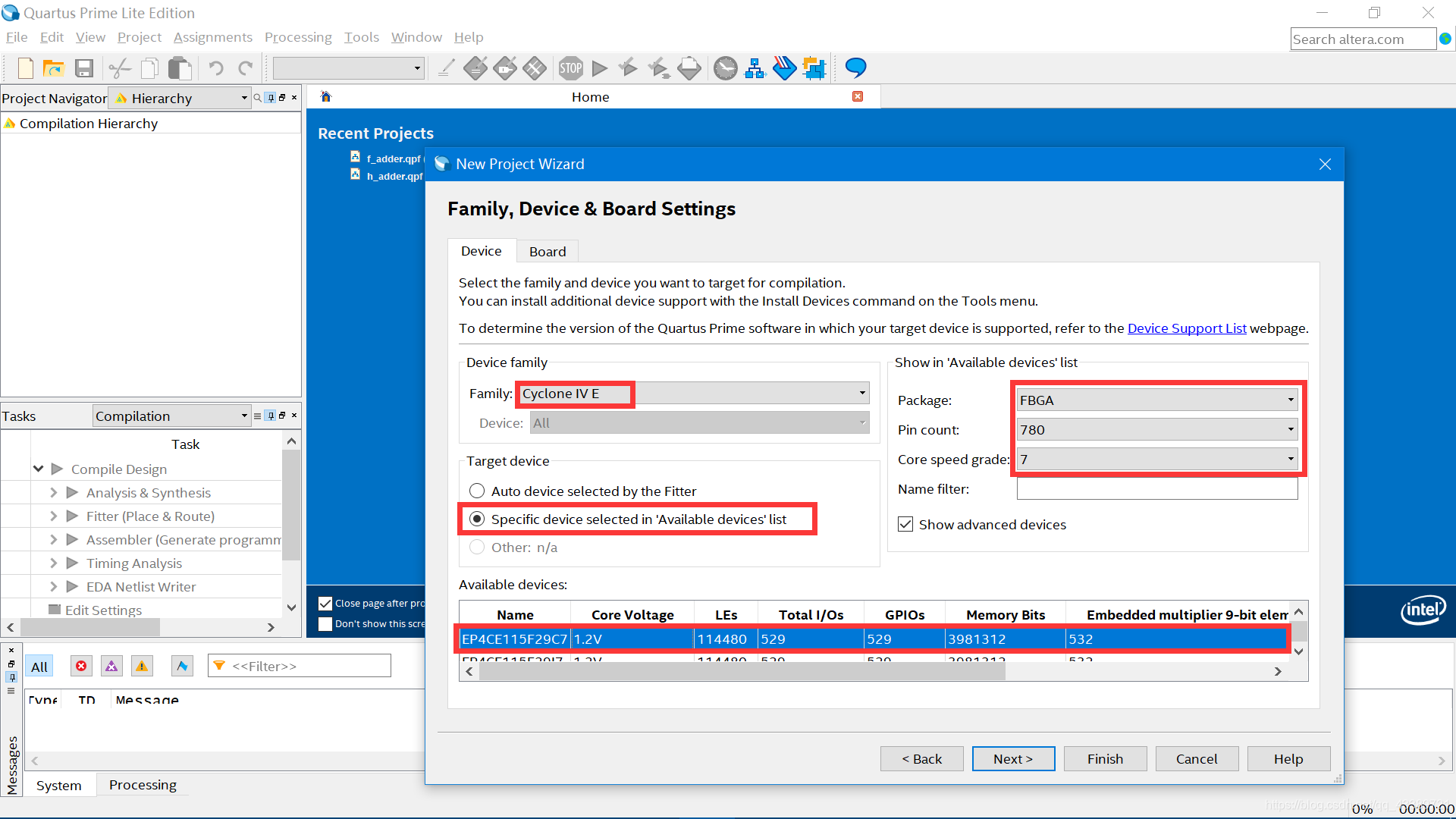

配置参数的页面,这是按照我们学校实验室的开发板来配置的,不同开发板应该配置的不一样。

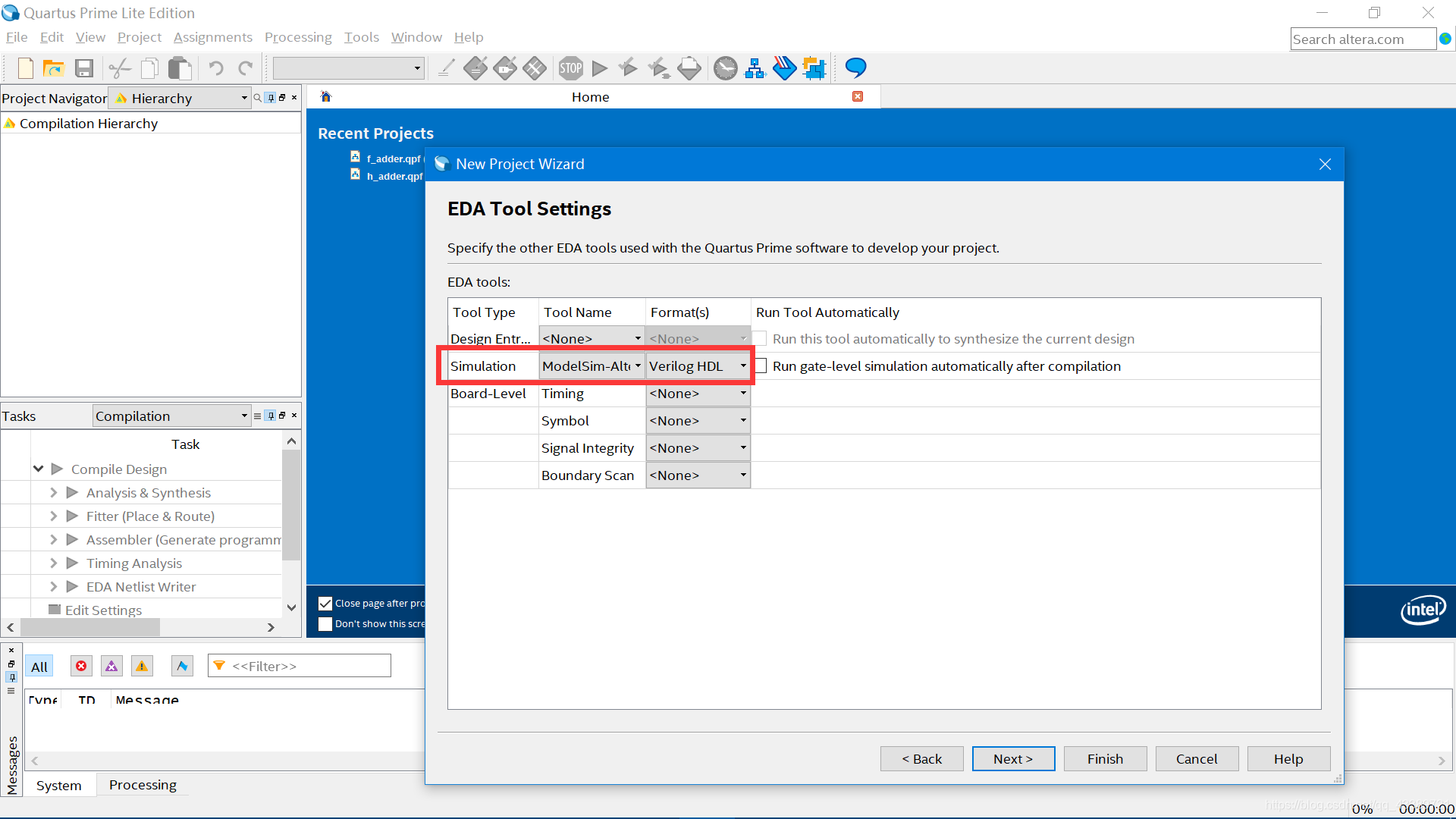

最后一步就是选择仿真的软件,点next之后会出来一个总结,显示了之前所有选择的参数,检查一下,如果不对可以back回去查看修改。

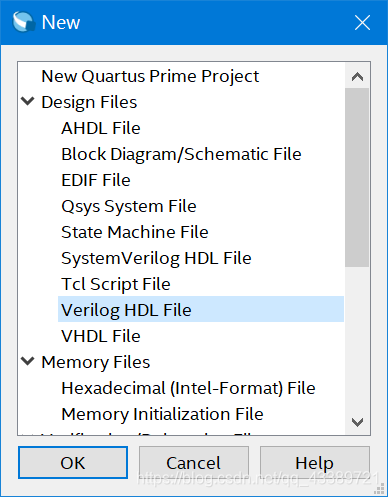

点击File- new,选择Veriog HDL File,最后点击File - Save as直接保存就可以了。

步骤三:编译之前的项目设置

最开始刚建好工程就跟着老师编译项目,但是发现用不了那个编译器,翻书才发现是要先配置一下,这里就直接放在敲代码编译之前吧。

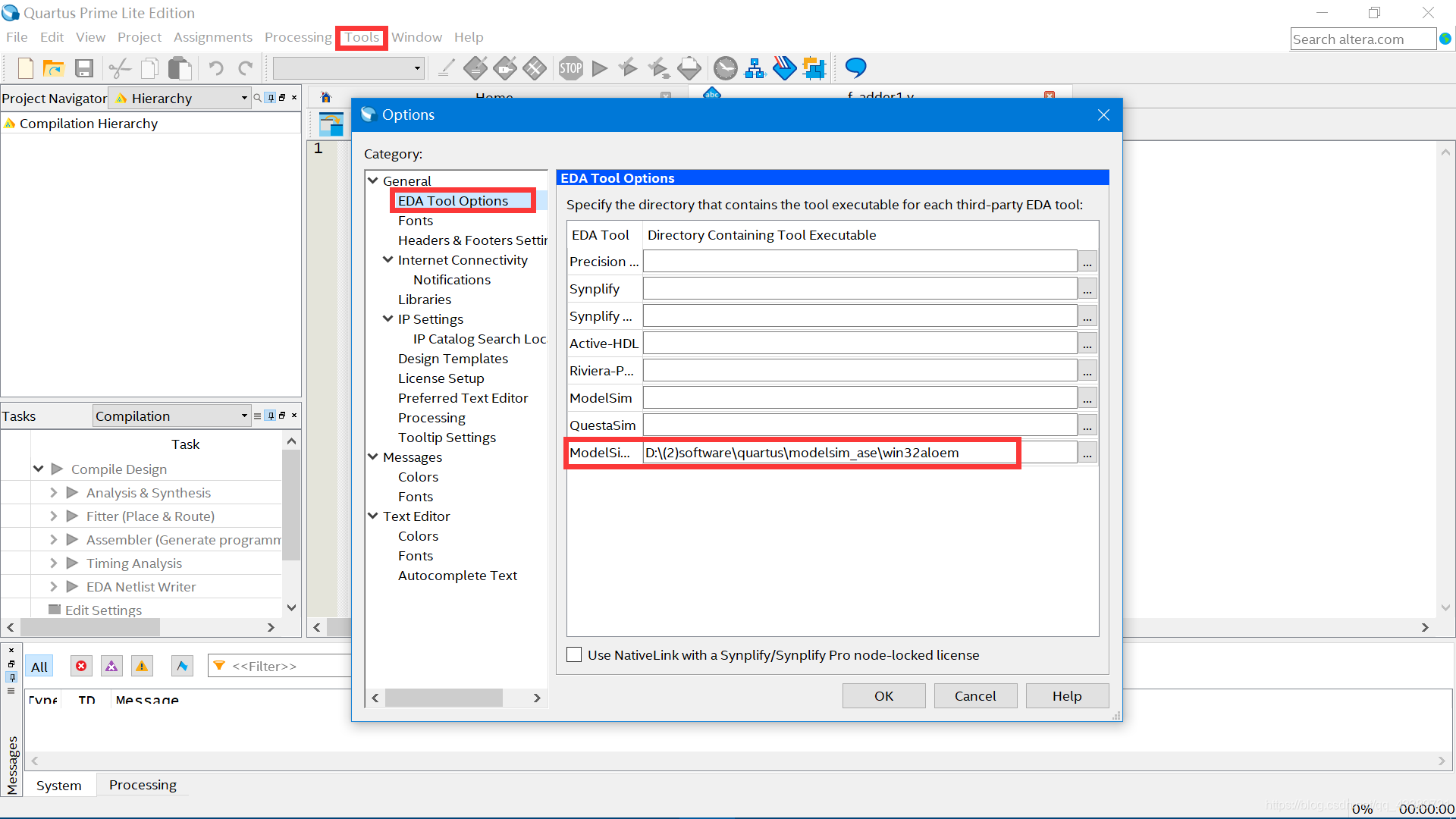

选择Tools-Options-EDA tool options,在ModelAim-Altera里要选择安装路径里面的modelsim_ase\win32aloem,下面的是我电脑的modelsim_ase\win32aloem路径。

书上还有一个全程编译前约束项目设置和全程综合与编译,暂时还没有用到,先放在这里,以后再补充。

步骤四:编写全加器与半加器的代码

这是半加器的数据流描述风格的程序设计

module h_adder (A,B,SO,CO);

input A,B;

output SO,CO;

assign SO = A ^ B;

assign CO = A & B;

endmodule

这是半加器的行为描述风格的程序设计

module h_adder1 (A,B,SO,CO);

input A,B;

output SO,CO;

reg SO,CO; //输出定义为寄存器类型

reg M;

always@(A,B)begin //always里面放输入

case({A,B})

0:begin SO = 0;CO = 0; end

1|2:begin SO = 1;CO = 0; end

//2:begin SO = 0;CO = 1; end

3:begin SO = 0;CO = 1; end

default:begin end

endcase

end

endmodule

这是半加器的结构描述风格的程序设计

module h_adder2 (A,B,SO,CO);

input A,B;

output SO,CO;

reg[1:0] M;

reg SO,CO; //输出定义为寄存器类型

always@(A,B)begin //always里面放输入

M = {A,B};

if(M == 0)begin CO = 0;SO = 0;end

else if(M == 1)begin CO = 0;SO = 1;end

else if(M == 2)begin CO = 0;SO = 1;end

else begin CO = 1;SO = 1;end

end

endmodule

这是全加器的数据流描述风格的程序设计

module f_adder (ain,bin,cin,cout,sum);

input ain,bin,cin;

output cout,sum;

assign cout = ain&bin|bin&cin|ain&cin;

assign sum = ain ^ bin ^cin;

endmodule

这是全加器的行为描述风格的程序设计

module f_adder1 (ain,bin,cin,cout,sum);

input ain,bin,cin;

output cout,sum;

reg cout,sum;

always@(ain,bin,cin)begin

case({ain,bin,cin})

0:begin cout = 0;sum = 0;end

1:begin cout = 0;sum = 1;end

2:begin cout = 0;sum = 1;end

4:begin cout = 0;sum = 1;end

3:begin cout = 1;sum = 0;end

5:begin cout = 1;sum = 0;end

6:begin cout = 1;sum = 0;end

7:begin cout = 1;sum = 1;end

default:begin cout = 0;sum =0;end

endcase

end

endmodule

这是全加器的结构描述风格的程序设计

module f_adder2 (ain,bin,cin,cout,sum);

input ain,bin,cin;

output cout,sum;

reg cout,sum;

reg [7:0] M;

always@(ain,bin,cin)begin

M = {ain,bin,cin};

if (M == 0) begin cout = 0;sum = 0;end

else if (M == 1) begin cout = 0;sum = 1;end

else if (M == 2) begin cout = 0;sum = 1;end

else if (M == 4) begin cout = 0;sum = 1;end

else if (M == 3) begin cout = 1;sum = 0;end

else if (M == 5) begin cout = 1;sum = 0;end

else if (M == 6) begin cout = 1;sum = 0;end

else if (M == 7) begin cout = 1;sum = 1;end

end

endmodule

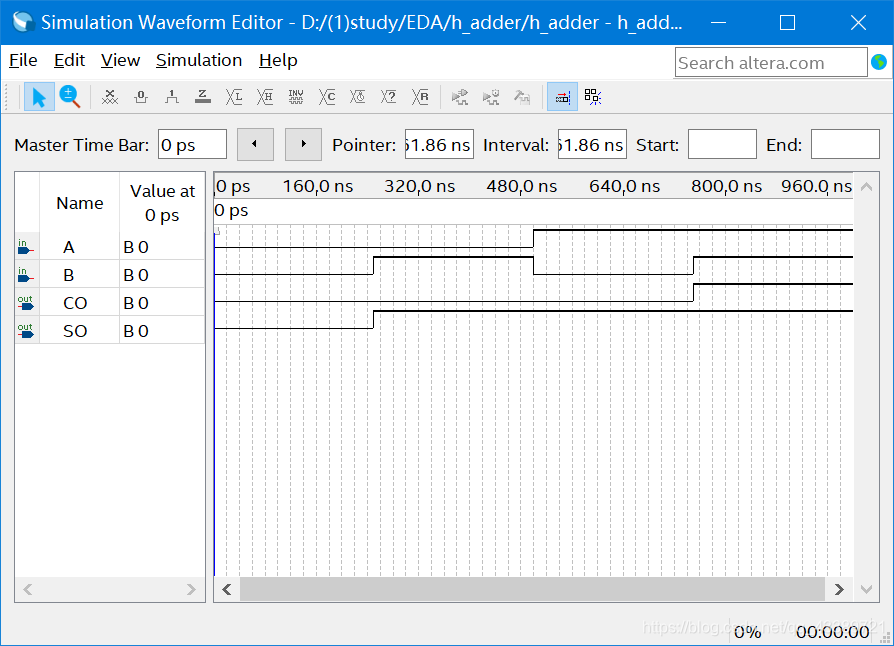

步骤五:时序仿真(复杂的来了)

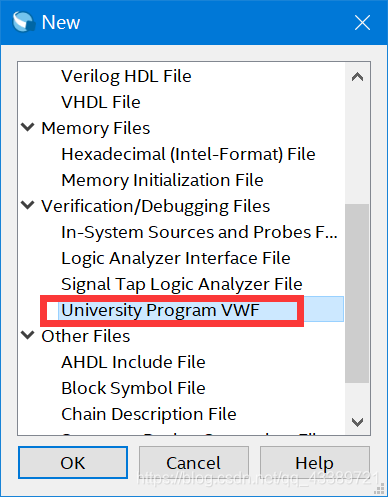

以半加器为例,还是File-New,选择如下图所示的University Program VWF,点了之后在出现的新界面点File - Save as ,名字千万别改,要不然会出莫名奇妙的问题。

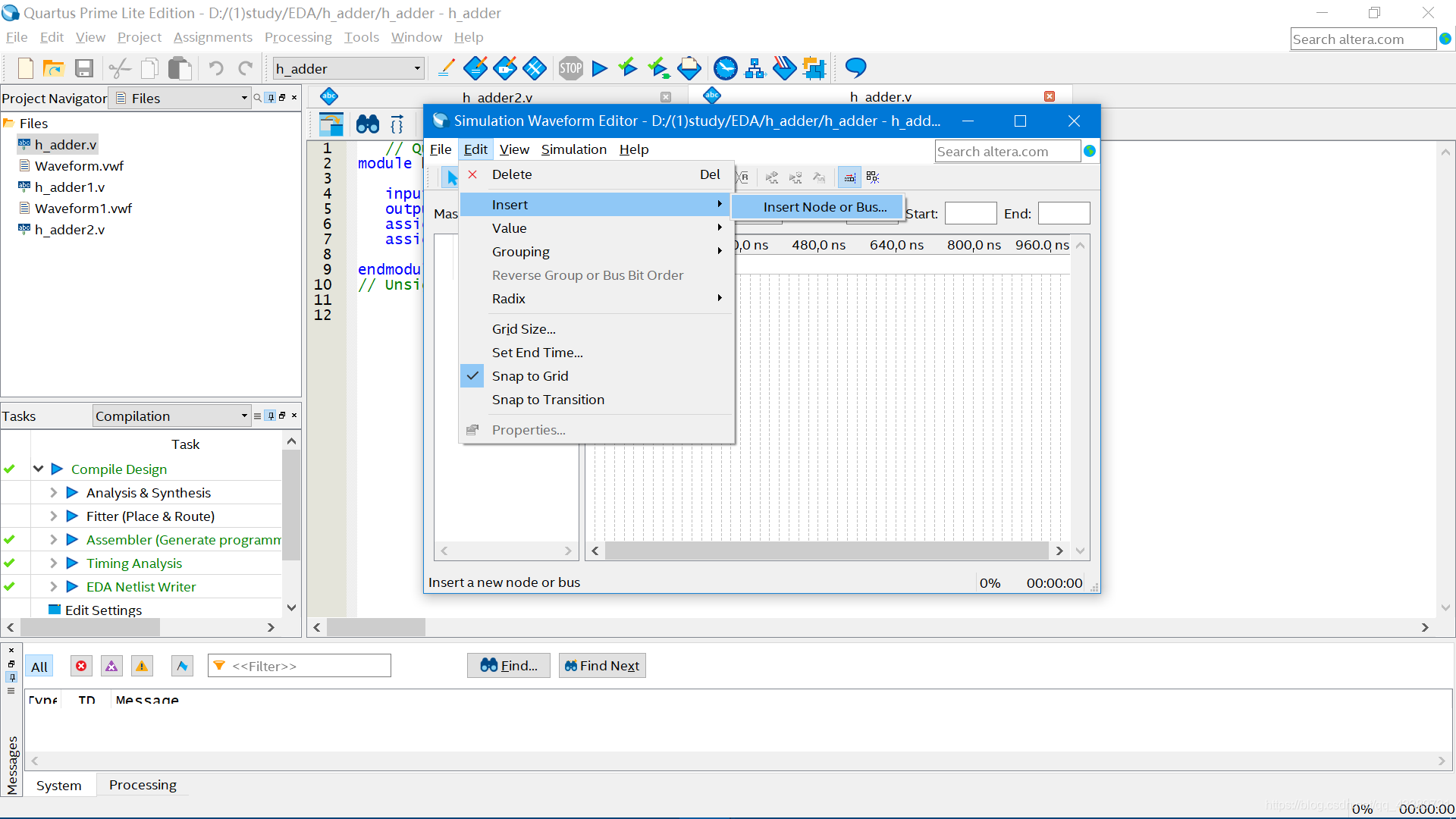

保存好之后点击Edit-Insert,insert node or bus

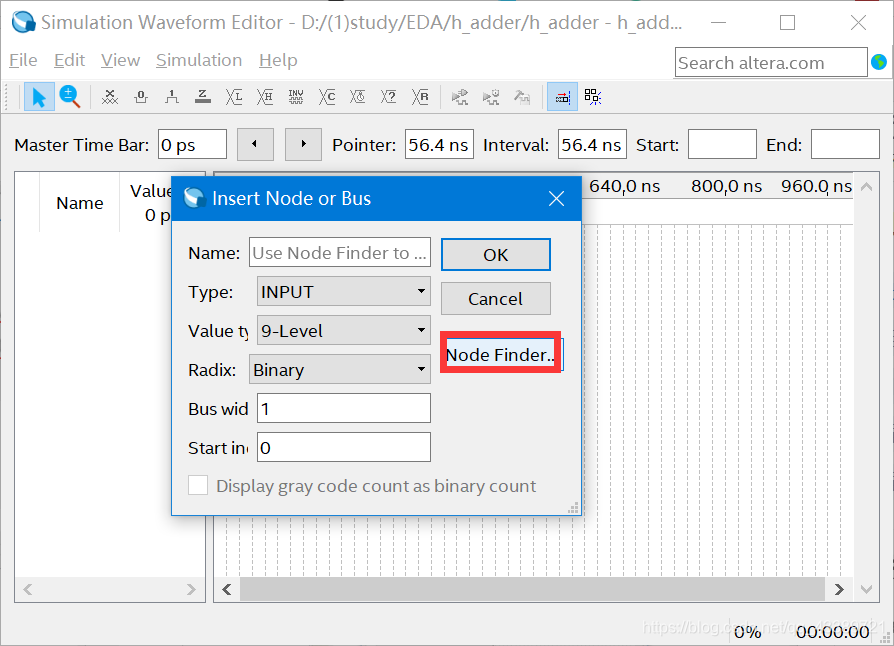

然后点node finder

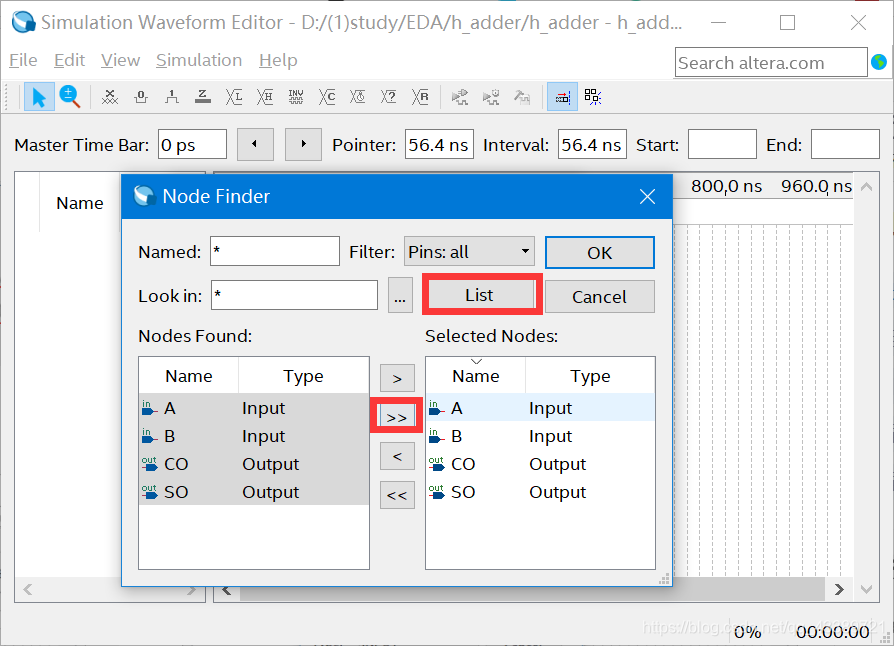

点以下两个,先List,然后是两个向右的箭头,最后点击两个OK。

步骤六:设置时间

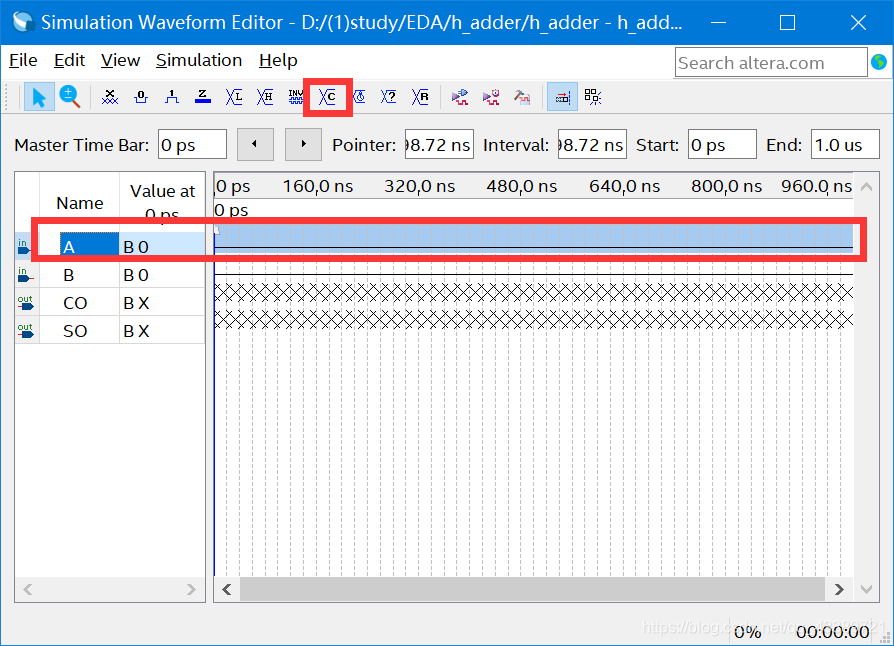

选择第一个输入信号,然后再点上面那个有一个c的符号,

设置500ns吧,然后第二个信号设置250ns。

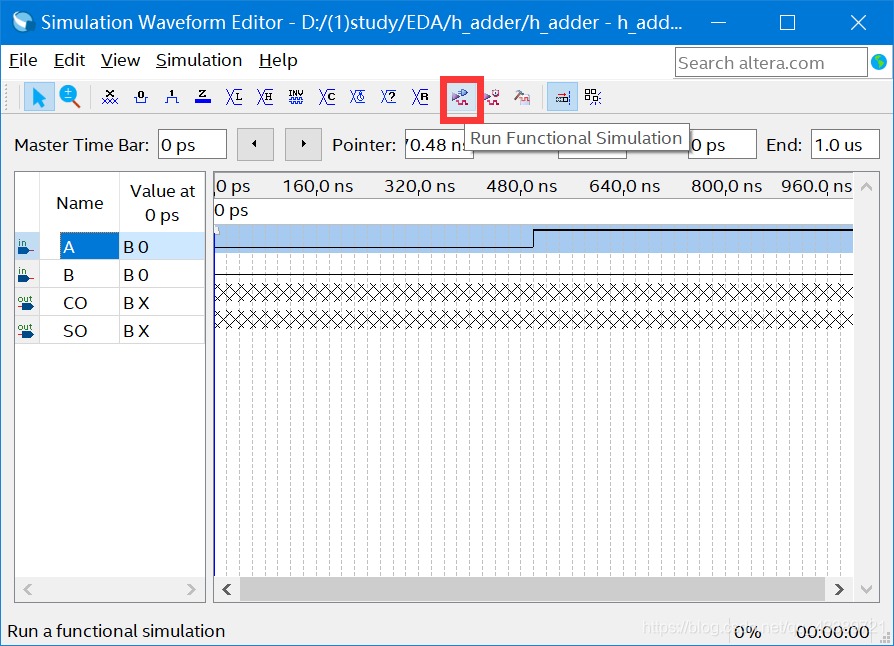

最后点击运行

完成!!!

本文详细介绍了如何使用Quartus18.1创建VerilogHDL的半加器和全加器项目,并进行时序仿真的步骤。从新建工程、配置编译器路径、编写代码到时序仿真设置,每个步骤都有清晰说明。涉及的数据流、行为和结构描述风格的代码设计,以及UniversityProgramVWF仿真文件的创建和设置,为读者提供了完整的实践指南。

本文详细介绍了如何使用Quartus18.1创建VerilogHDL的半加器和全加器项目,并进行时序仿真的步骤。从新建工程、配置编译器路径、编写代码到时序仿真设置,每个步骤都有清晰说明。涉及的数据流、行为和结构描述风格的代码设计,以及UniversityProgramVWF仿真文件的创建和设置,为读者提供了完整的实践指南。

1799

1799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?