目录

一、什么是D触发器

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

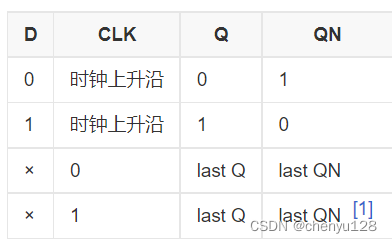

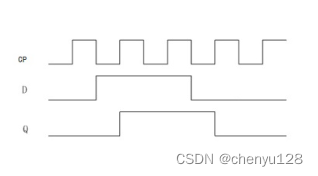

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等等。

二、门电路设计D触发器并仿真

1、创建工程

先新建个文件夹存放工程项目文件

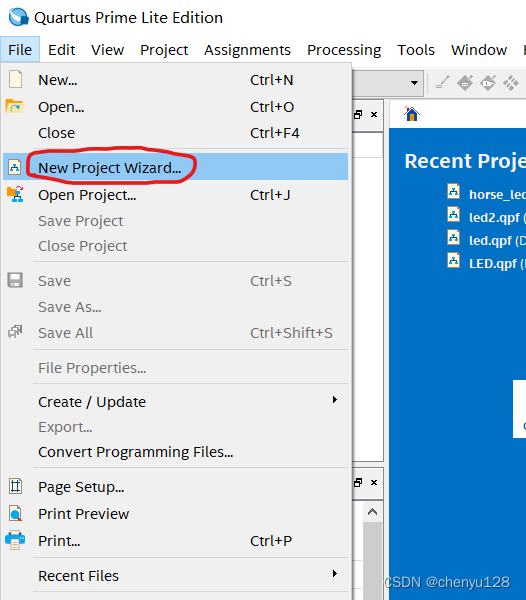

然后新建项目文件:

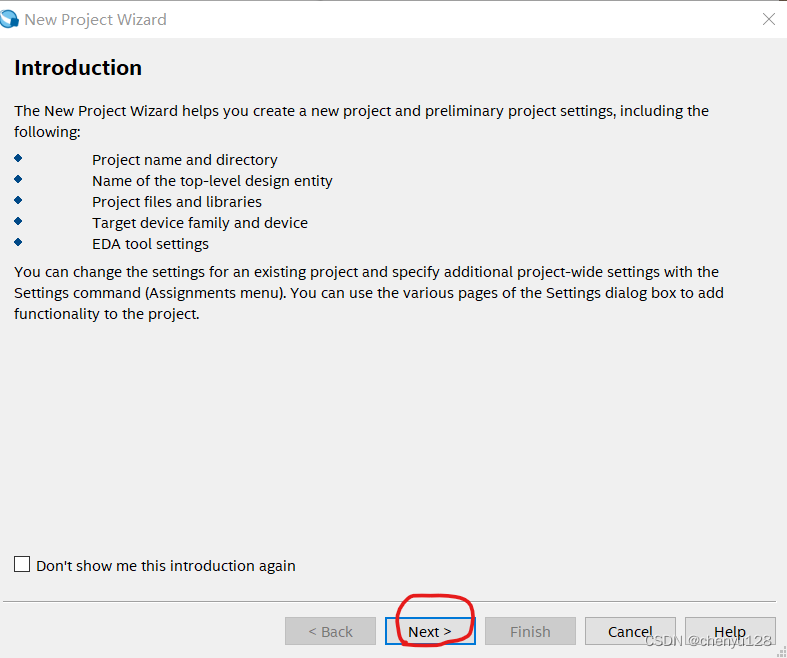

点击next

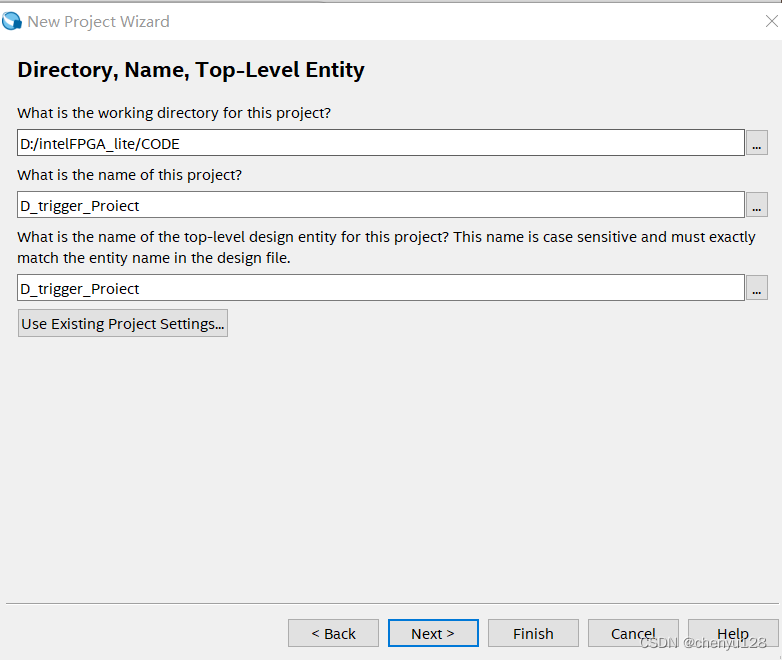

设置工程的存储位置和项目名称

弹出对话框,选择Yes:

点击next:

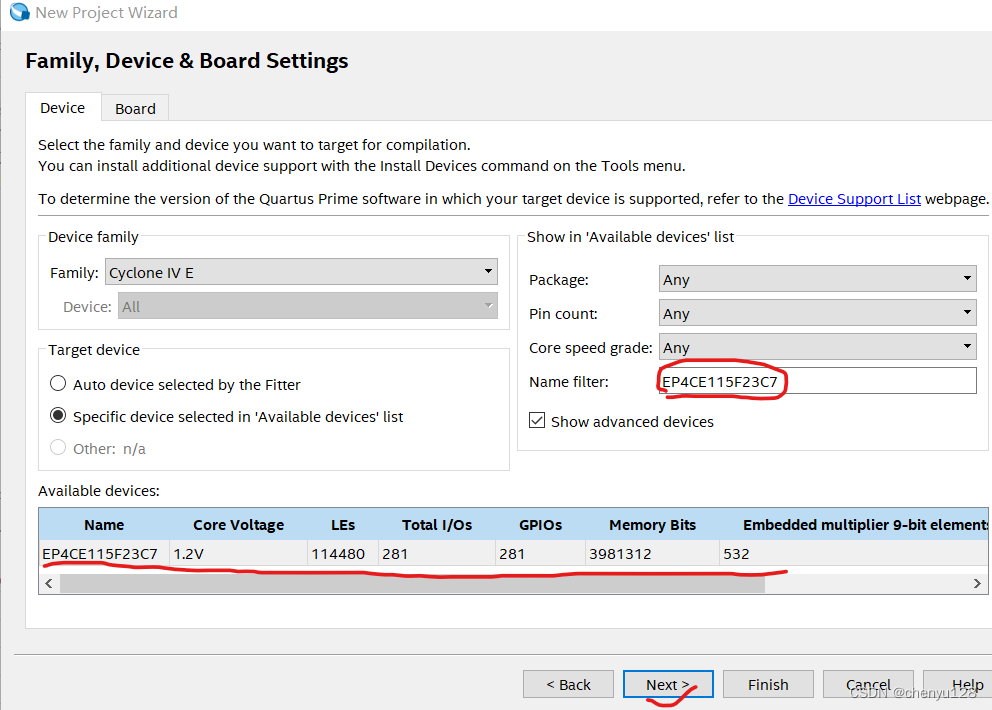

选择目标芯片:cycloneIVE系列的EP4CE11529C7

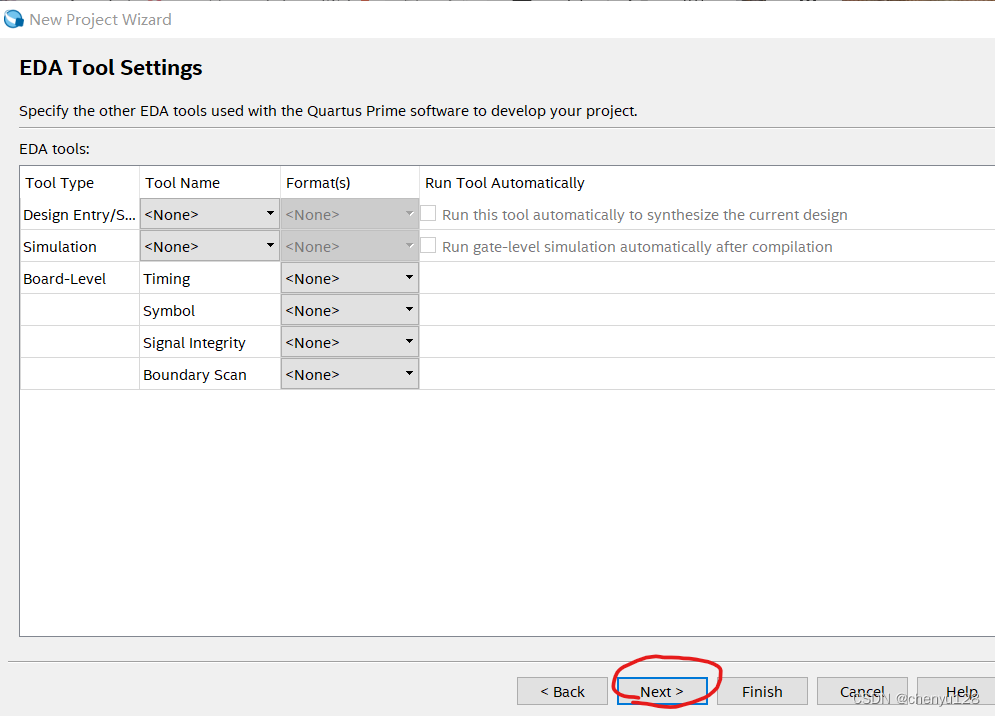

EDA Tool Setting设置

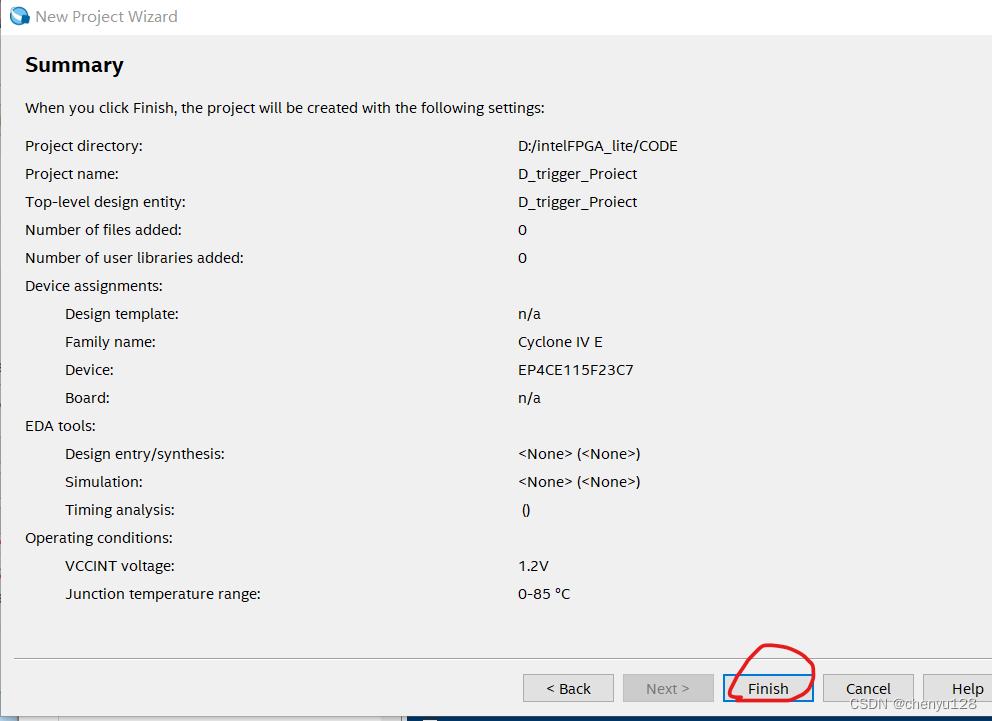

点击finish

创建成功,进入项目

2、设计电路原理图文件

打开QuartusII,选菜单“File”一“New”,在弹出的“New-”对话框中选择“ Design Files” 的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3202

3202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?