采用artix7-fgg484- -2

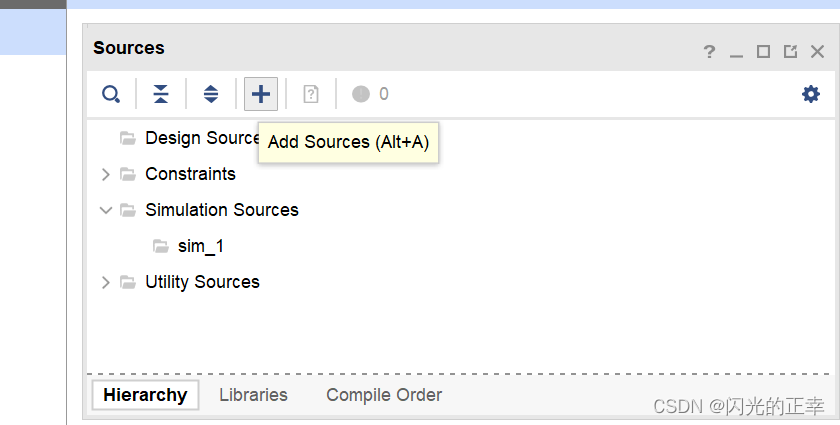

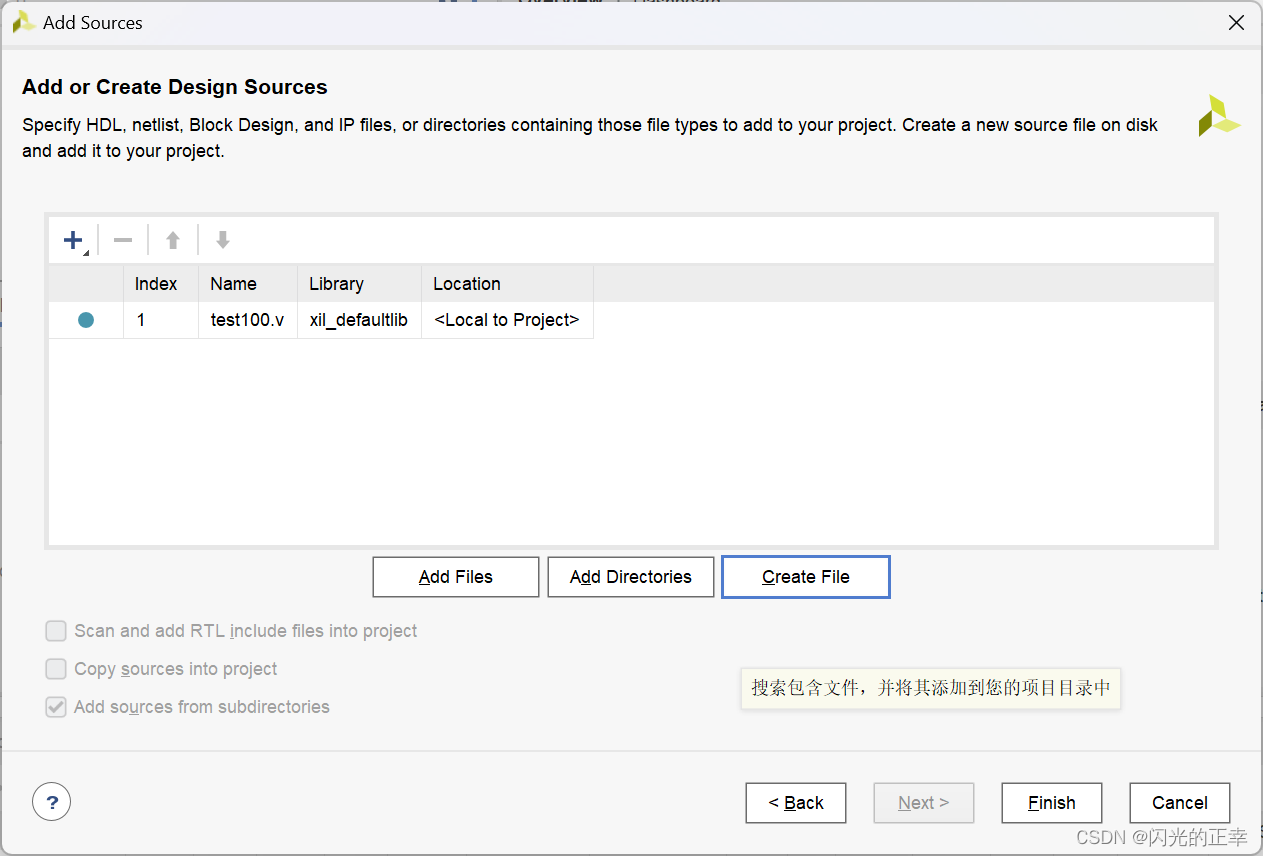

1.创建好之后可以选择添加或者创建.v文件。用verilog语言编写代码

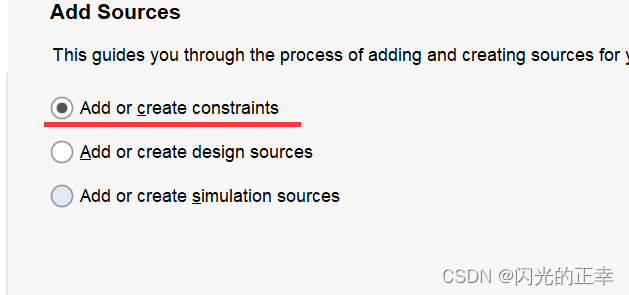

2.然后创建约束文件(管脚约束、始终约束等)

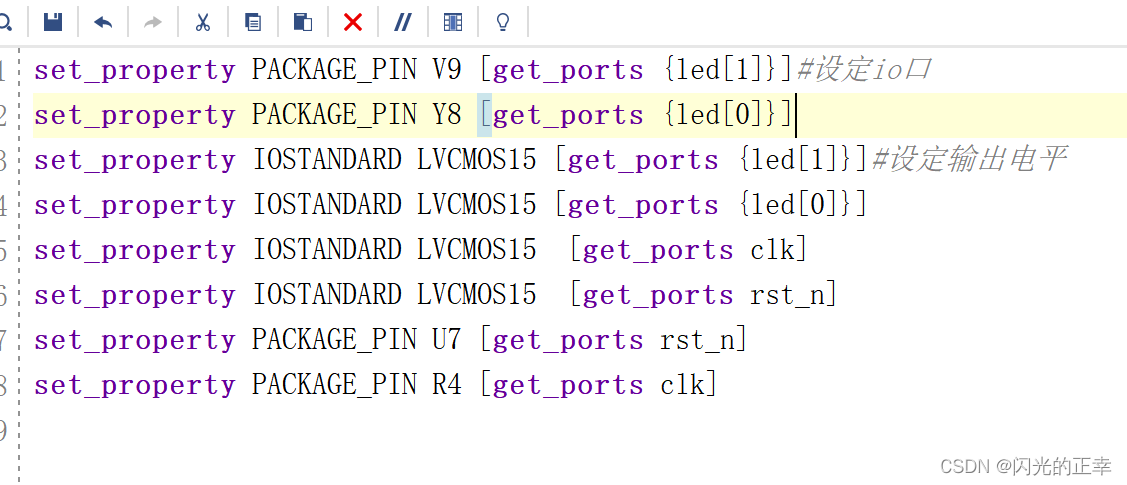

自己写的约束文件

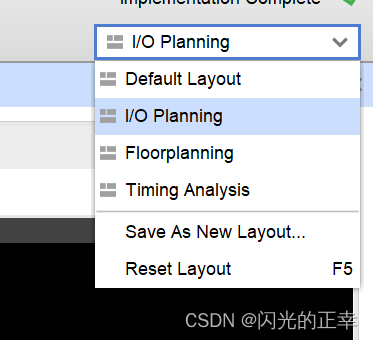

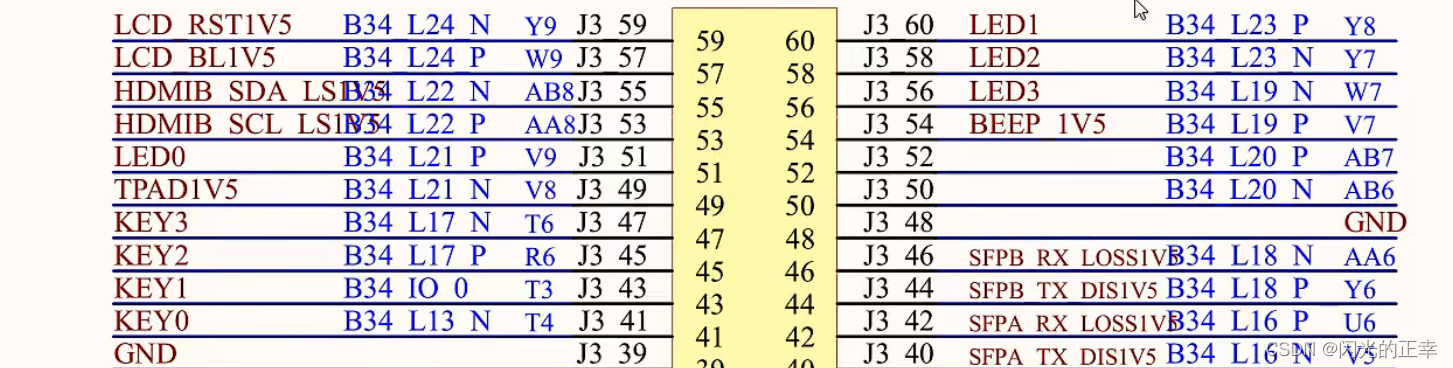

也可以在运行了synthesis之后可以在右上角选择io/planning进行管脚约束

其中led的管脚为v9,y8,y7,w7,fpga的bank中 bank34跟bank35的是1.5v其他都是3.3v ,除非有别的需求。clk是r4,rst是u7。

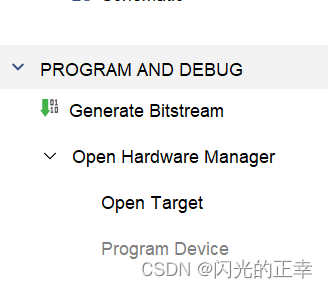

3.点左下角生成bit流,然后open target 连接到板子。最后program device将生成的bit流文件烧尽板子里。注意(因为没有固化代码所以断电之后代码就消失了,除非后面固化上)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?