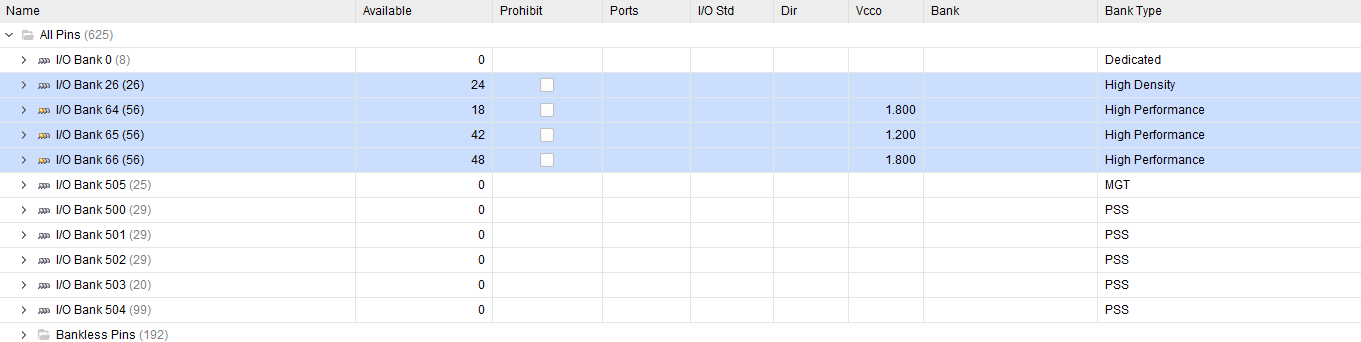

Fpga器件有很多bank,不同bank有不同的作用,下面随便找了一款器件介绍下bank分类

从上图可以看出,这个器件共有625个引脚,总共有11个bank,其中bank26,bank64,bank65,bank66是PL侧bank,其余的都是PS侧bank。

bank0:一般用来作为ADC电压输入,温度传感器输入,以及部分配置端口;

bank26 : HD bank;

bank64,65,66 : HP bank;

bank50x ; PS侧使用的bank;

下面我们重点说下3cg器件bank503中的一些io(需要查看下ug570,再更新)

1)PS_MODE0~PS_MODE3 : boot模式管脚;

2) PS_ERROR_OUT,ERROR_STATUS

3) PS_REF_CLK

4) JTAG_TDI, JTAG_TDO, JTAG_TCK, JTAG_TMS

5) PADI, PADO

6) INIT_B

7) PROG_B,输入信号,当拉低时代表FPGA当前配置被cleared,会重新发起一个配置序列,相当于会重新根据boot引脚boot一次?

8) POR_B

9) SRST_B

10) DONE,如果为高代表configuration 完成,配置过程中为0?

HP/HD/HR bank说明:

在ultrascale器件中,会把PL侧bank分为HP,HD,HR三种,HP bank一般用来满足高速接口,电压最高支持到1.8V;HR bank一般用来满足高范围电平接口,电压最高支持到3.3V; HD bank用来支持低速接口;ultrascaler器件会组合使用HP,HD,HRbank,但是不保证在同一个器件中同时会有3个类型的bank。另外DCI接口只能使用在HP bank上。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?