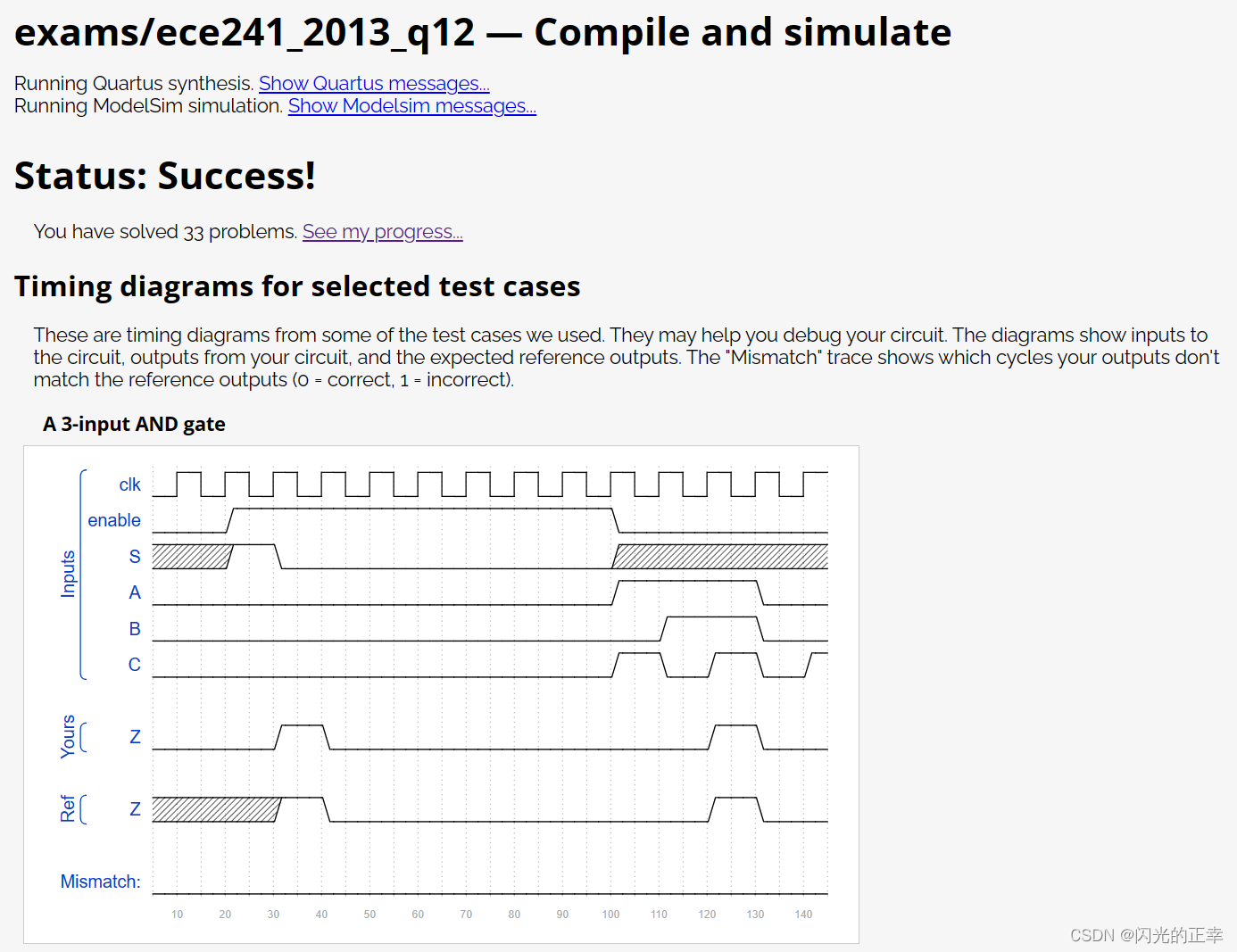

1、这个题就是八个移位寄存器以及一个三位的选择器。我的理解是选择器那里应该是组合逻辑所以应该用阻塞赋值,非阻塞赋值的话就会延后一个周期。

2、还有就是模块的名称不能跟本来的定义的名称一样。之前名字是dff 跟fpga内部的逻辑器件重名就会报错。

完整代码如下:

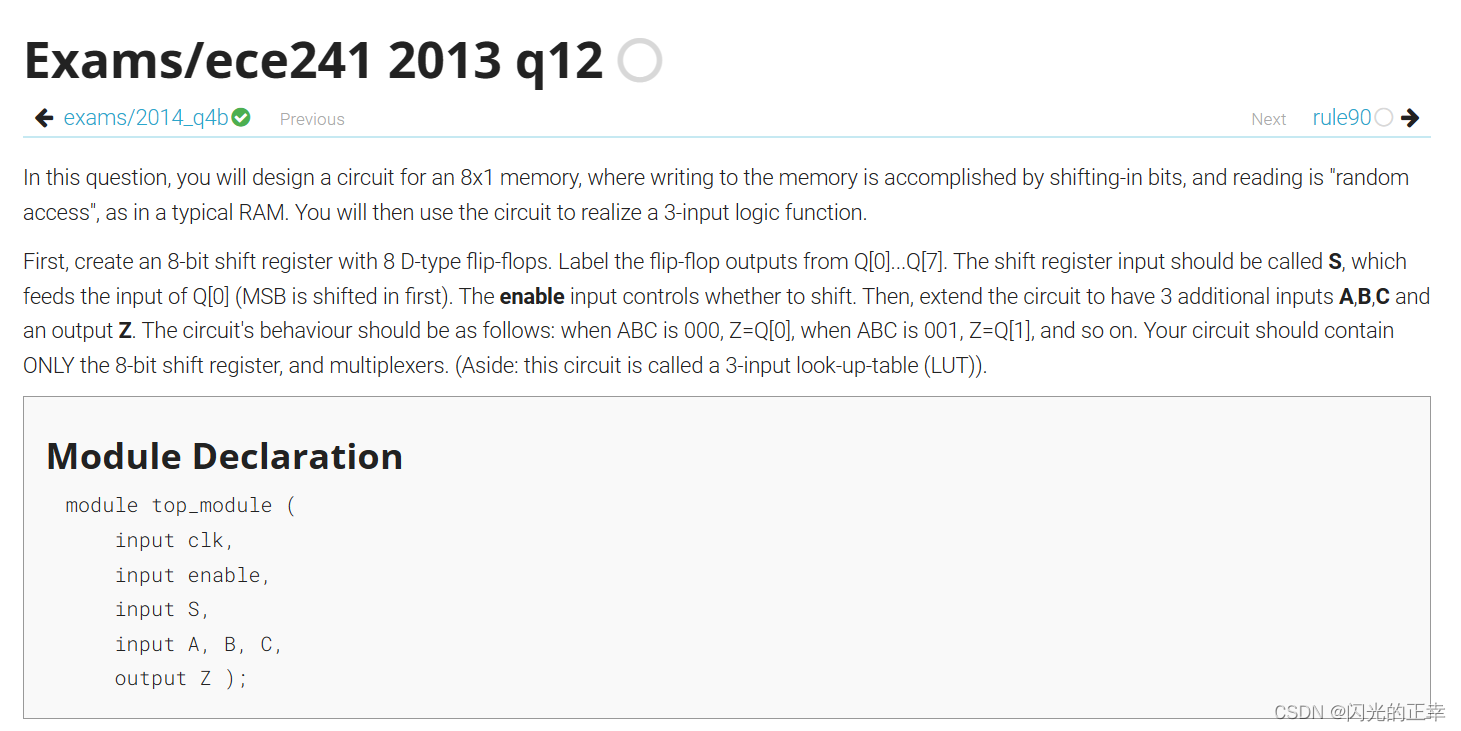

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output Z );

reg [7:0]Q;

dfif dff_u0(.clk(clk), .d(S), .enable(enable), .q(Q[0]));

dfif dff_u1(.clk(clk), .d(Q[0]), .enable(enable), .q(Q[1]));

dfif dff_u2(.clk(clk), .d(Q[1]), .enable(enable), .q(Q[2]));

dfif dff_u3(.clk(clk), .d(Q[2]), .enable(enable), .q(Q[3]));

dfif dff_u4(.clk(clk), .d(Q[3]), .enable(enable), .q(Q[4]));

dfif dff_u5(.clk(clk), .d(Q[4]), .enable(enable), .q(Q[5]));

dfif dff_u6(.clk(clk), .d(Q[5]), .enable(enable), .q(Q[6]));

dfif dff_u7(.clk(clk), .d(Q[6]), .enable(enable), .q(Q[7]));

always@(*)begin

case({A,B,C})

3'd0:Z=Q[0];

3'd1:Z=Q[1];

3'd2:Z=Q[2];

3'd3:Z=Q[3];

3'd4:Z=Q[4];

3'd5:Z=Q[5];

3'd6:Z=Q[6];

3'd7:Z=Q[7];

endcase

end

endmodule

module dfif(

input clk,

input d,

input enable,

output q

);

always@(posedge clk)begin

if(enable)begin

q<=d;

end

else begin

q<=q;

end

end

endmodule

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?