创建项目

先添加c设计文件(.c /.h)再添加c-based testbench文件(test.c/out.gold.dat这是标准输出)

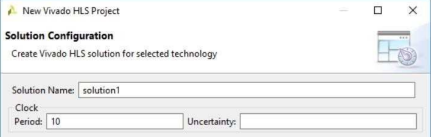

时钟周期(10ns)和时钟不确定性(默认为12.5%的时钟周期,留空/未定义)。

实践步骤

一共四个步骤,其实就对应这下列图标从左到右

-

c仿真 将函数输出与已知正确值比较,若失败可以选择launch debugger调试。生成csim文件夹

-

C综合,将c设计合成为RTL(verilog语言描述的寄存器转换电路),报告中有时延、利用率估算(使用的各个模块数)、接口等信息。生成syn文件夹

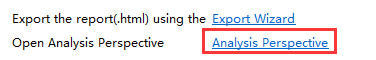

下图红框可以看结构(具体怎么看?)

-

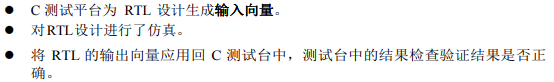

C/RTL联合仿真,验证生成的RTL的正确性。sim文件夹

可以看硬件仿真波形 -

export RTL,即创建IP 生成impl文件夹

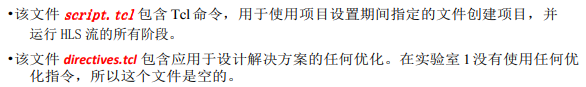

tcl文件

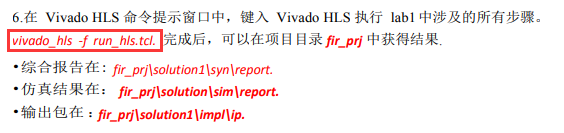

用tcl文件可以以批处理的模式运行vivado HLS,可以很简单的复现出别人由一些步骤得到的结果

其实下面impl等中也有tcl文件,我们就用script.tcl重命名成run_hls.tcl 在Vivado HLS 2018.3 Command Prompt (命令提示符)中运行

HLS中的ap_axis,ap_axiu

HLS中要利用AXI-stream总线传输数据,HLS中的接口需要用ap_axis,ap_axiu类型的结构体定义,结构体中的data数据是ap_uint<32>的,也就是说AXI-stream传输的数据会被统一被封装为ap_uint<32>类型。

hls接口还没看的部分:

http://xilinx.eetrend.com/blog/2021/100063927.html

https://blog.csdn.net/mmphhh/article/details/115655208

https://blog.csdn.net/qq_37719487/article/details/114794569

https://blog.csdn.net/h__ang/article/details/90084477

2770

2770

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?