DDR原理及MIG IP核使用记录

资料参考

1、Xilinx FPGA平台DDR3设计保姆式教程(汇总篇)——看这一篇就够了这篇写的很全面详细

2、快速上手Xilinx DDR3 IP核----汇总篇(MIG) 该系列介绍了Xilinx 控制DDR3的IP核----MIG IP核的基本构成和使用方法,在MIG 接口的基础上在外部封装了FIFO,使得操作时序更加简单,并用此方法实现了几个练手的小项目。

3、FPGA ——DDR基础概念详解_居安士的博客读写操作引脚有详细说明

4、DDR全接口说明: 知乎:基于FPGA的DDR3设计(3)MIG IP核的使用教程

5、

关于上图的教程自己找的:

一个总的下载链接:eechina

仿真篇

设计篇

综合篇

高富帅篇

6、FPGA:DDR3保姆级教程 b站讲了IP配置过程,带宽计算和官方源码解读,对照波形图进行了说明,对时钟的选择讲的比较清楚

一、DDR

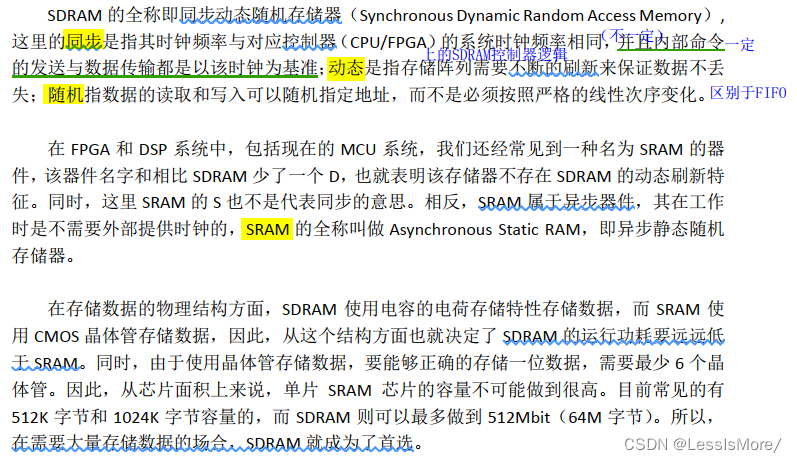

DDR SDRAM介绍

DDR=Double Data Rate双倍速率,DDR SDRAM=双倍速率同步动态随机存储器,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。

SDR SDRAM采用单端(Single-Ended)时钟信号, 在一个时钟周期内只传输一次数据;而 DDR由于工作频率比较快,采用可降低干扰的差分时钟信号作为同步时钟。在一个时钟周期内可以传输两次数据,它能够在的DQS上升沿和和下降沿各传输一次数据。

相对比于DDR,DDR2的时钟加速,是DDR的两倍,DDR3的时钟是DDR的四倍

DDR存储机制

DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank(Logical Bank,下面简称Bank)。

目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。

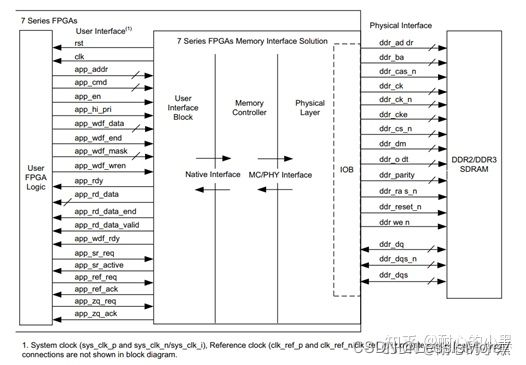

二、MIG ip核

MIG(Memory Interface Generators) IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的 控制流程。MIG IP 核对外分出了两组接口,左侧是用户接口,就是 用户(FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。右侧为 DDR 物理芯片 接口,负责产生具体的操作时序,并直接操作芯片管脚。这一侧用户只负责分配正确的管脚,其他不用关心。

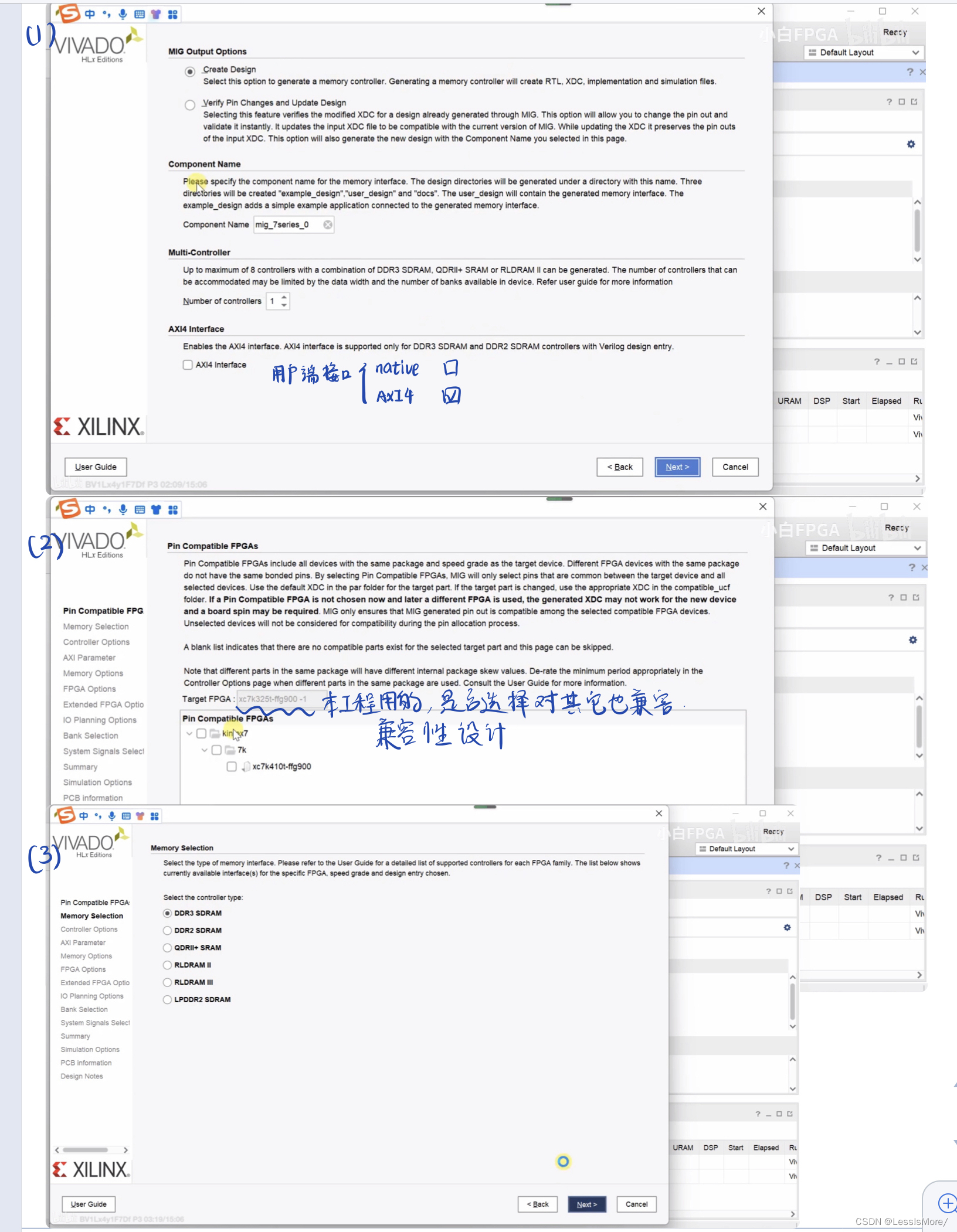

MIG IP核对外提供了两类接口:Native接口和AXI4接口,把我们从DDR3芯片自身复杂的接口和时序中解放了出来。 Native接口比较简单,而且效率很高,但是不如AXI4接口通用性强。本次工程中使用的是AXI4接口。

基于Vivado MIG IP核的DDR3控制器(DDR3_CONTROL)有下图和ip核的对应配置

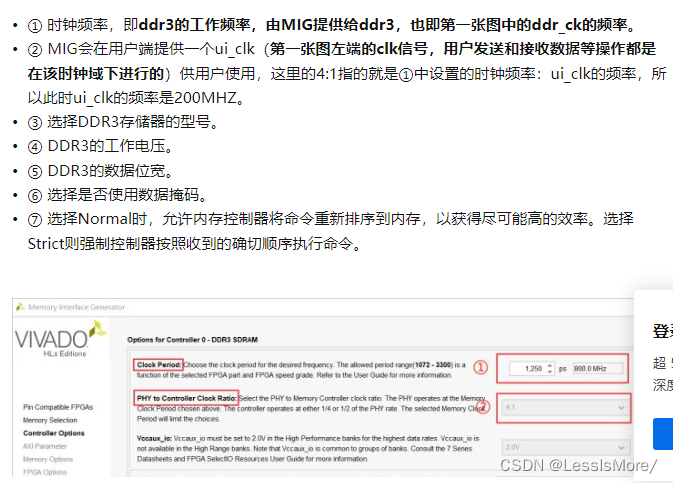

下面介绍MIG在vivado中调用时的配置,前面简单的就不说了,重点来说时钟设置。

以下内容大多参考:FPGA——调用DDR的IP核(MIG核)

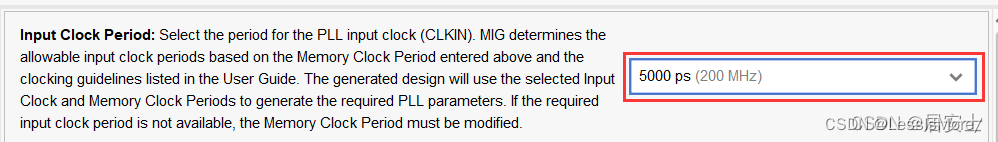

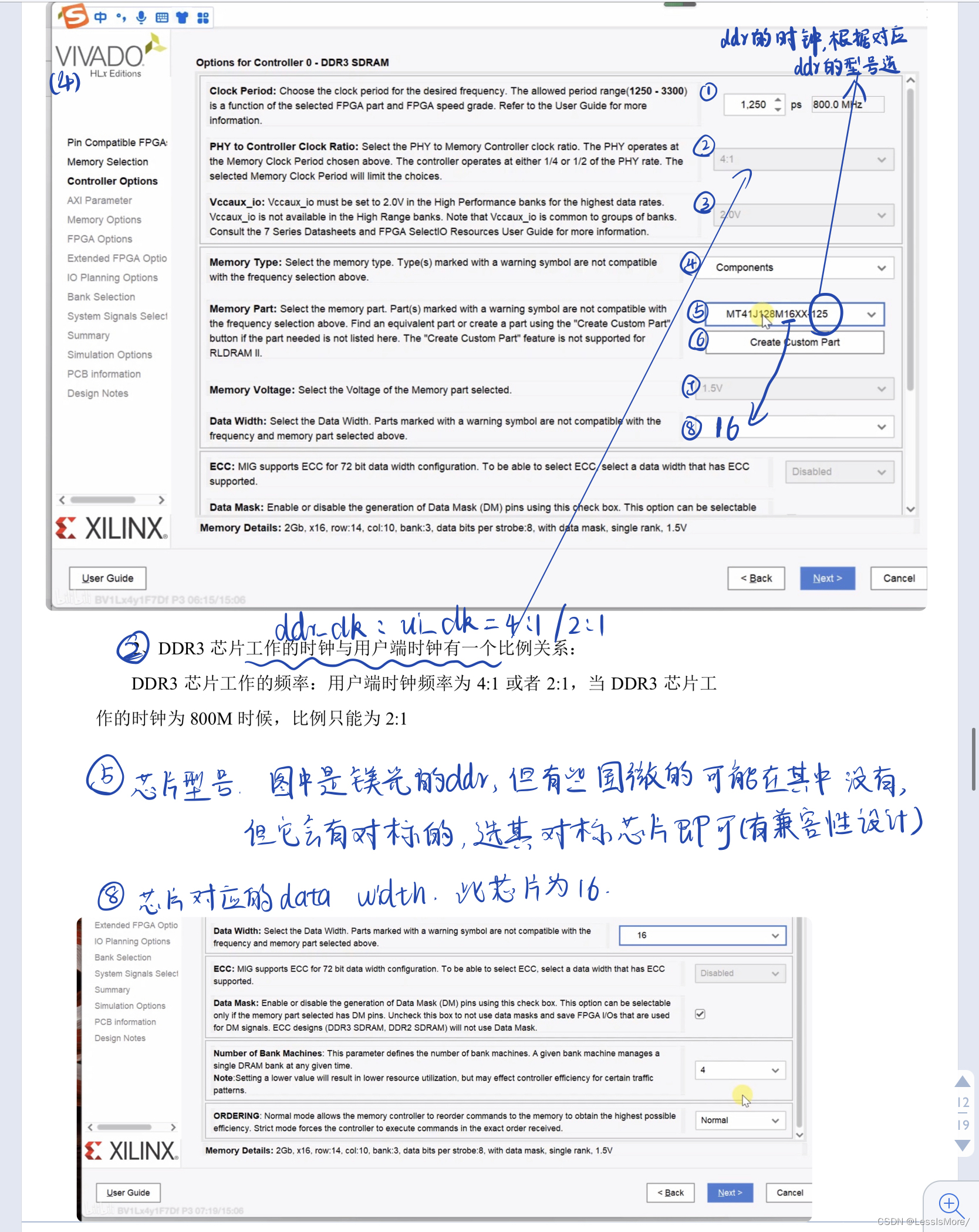

这个讲解的更详细:快速上手Xilinx DDR3 IP核(1)----MIG IP核的介绍及配置(Native接口)有ip核的接口介绍和配置介绍 。其中提到:Clock Period:DDR3 芯片运行时钟周期,这里选400M,实际传输频率800M(上下沿双触发)?那用户4:1是100?

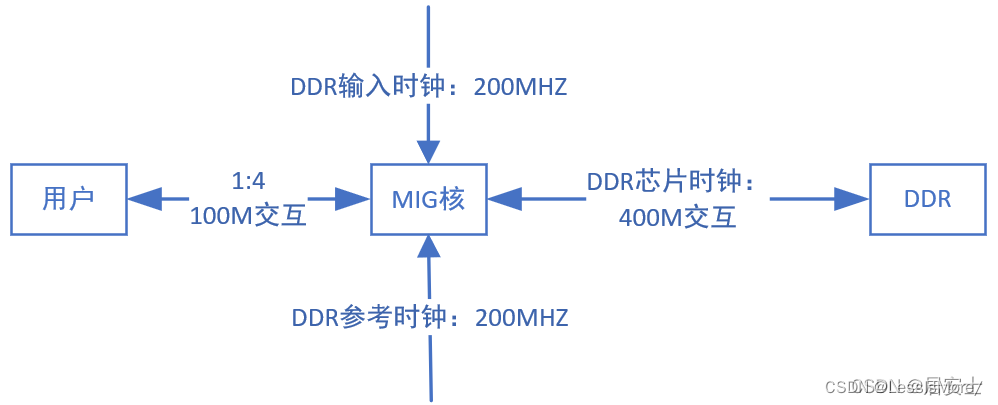

1、DDR的ddr_ck与用户的ui_clk

上图中的800MHZ是由MIG核送给FPGA外的DDR3芯片的

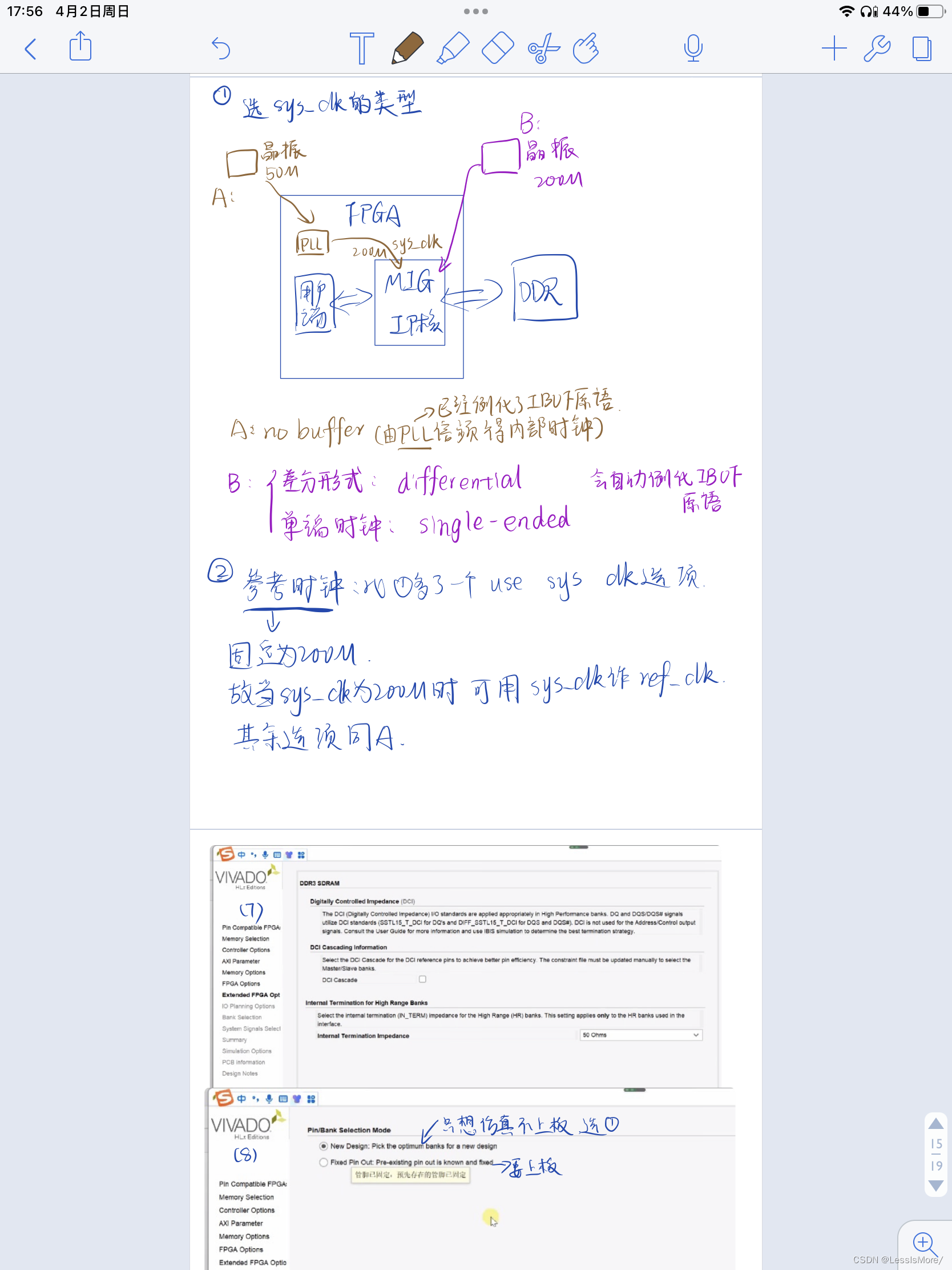

2、给MIG ip核的输入时钟与参考时钟

※DDR输入时钟:此处选择的时**提供给MIG核的时钟**

建议选择200MHZ和参考时钟(固定为200MHZ)相同

注意,这个地方只选了输入时钟的频率,并没有让选输入时钟的形式,输入时钟形式在下一页面选择

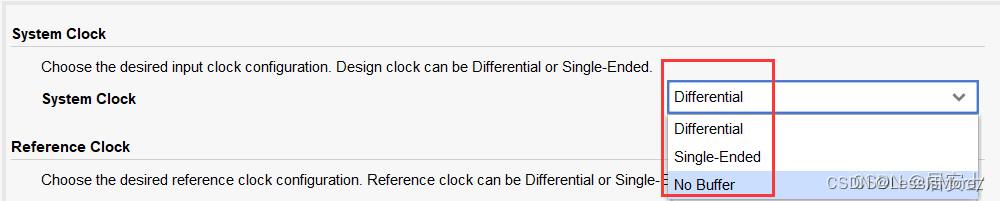

下面就是※MIG核输入时钟的形式选择

输入MIG核的时钟可以从FPGA外部直接给,也可以从FPGA内部给,如果时钟从外部给,那么可以选择差分,如果时钟从内部给,那么选no buffer(没有buffer计)或者单端。

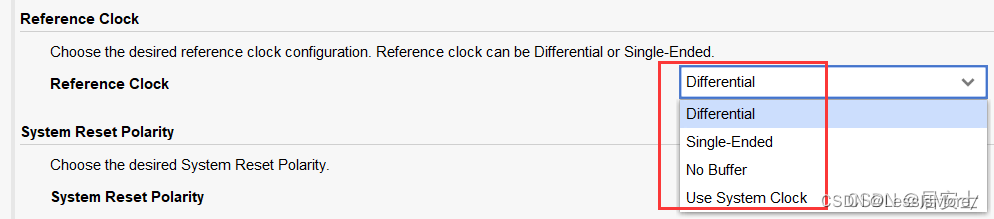

下图为※MIG参考时钟(为200MHZ)

这里面的四个时钟(DDR芯片时钟,DDR输入时钟,DDR参考时钟,用户时钟)是非常叫人迷惑的,下面画张图帮助理解

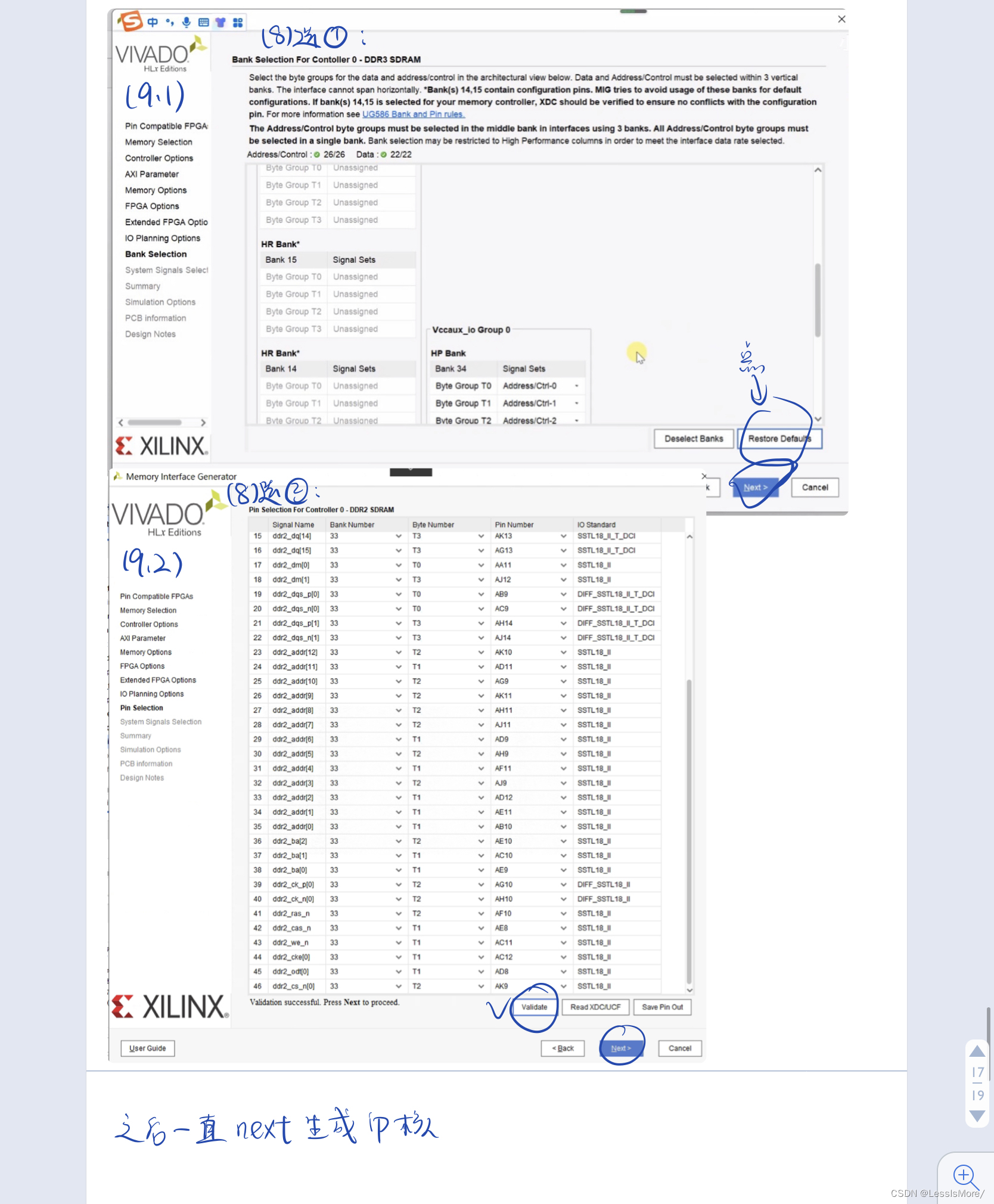

3、ip核使用步骤记录

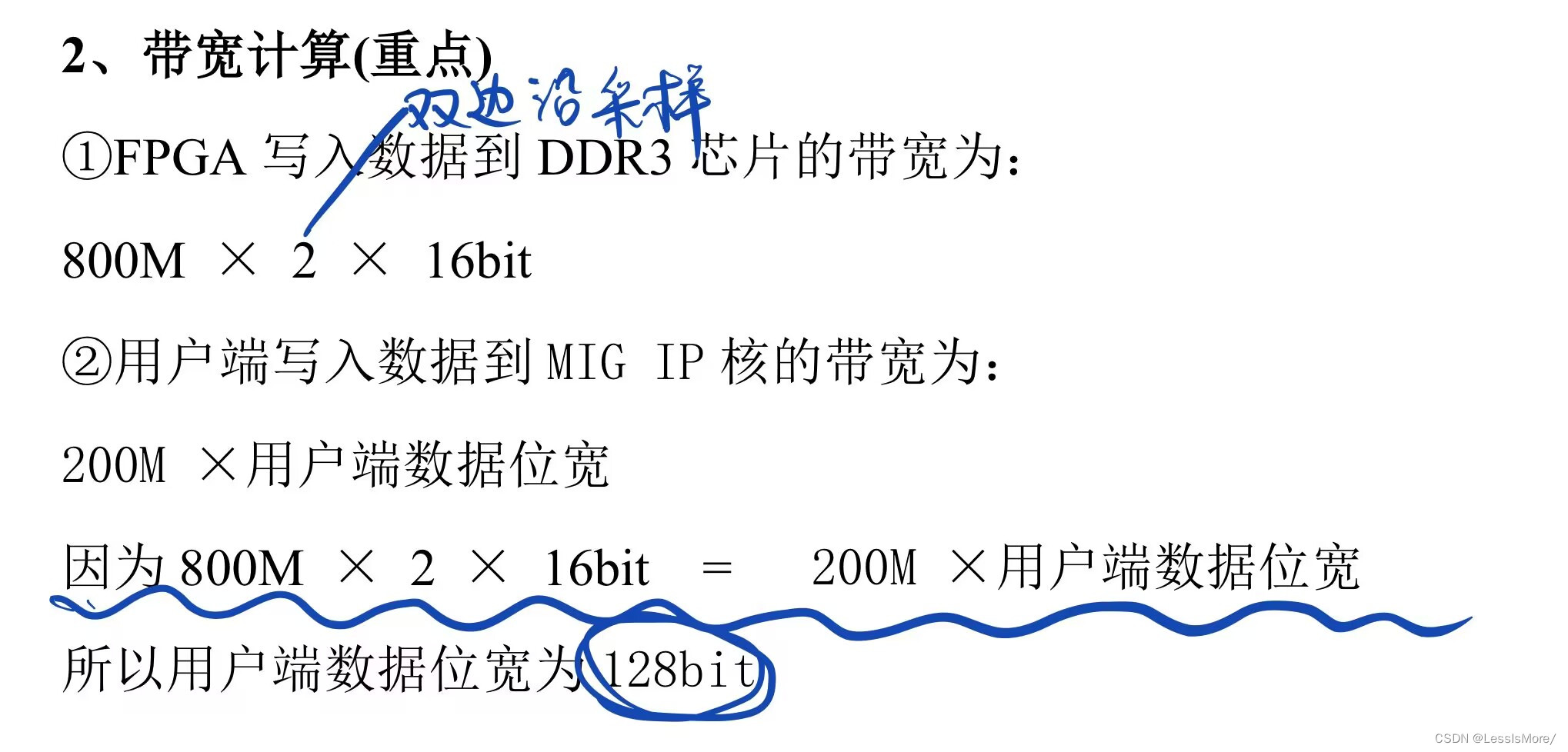

中间好像少了一个axi的位宽,这里是根据用户端核ddr端带宽相等算出来的,如下图。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?