一、时钟基础:

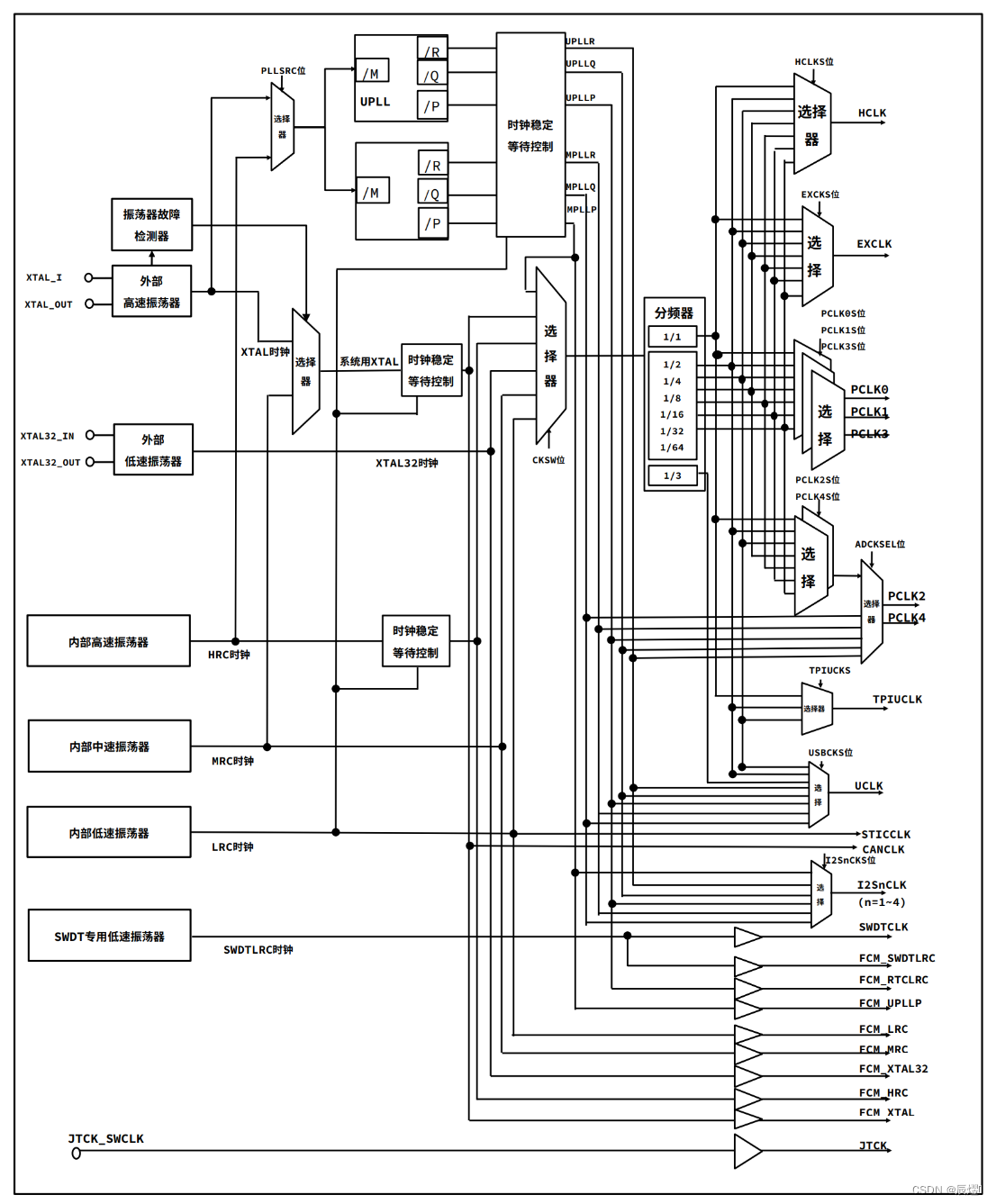

时钟控制器(CMU)

1.简介

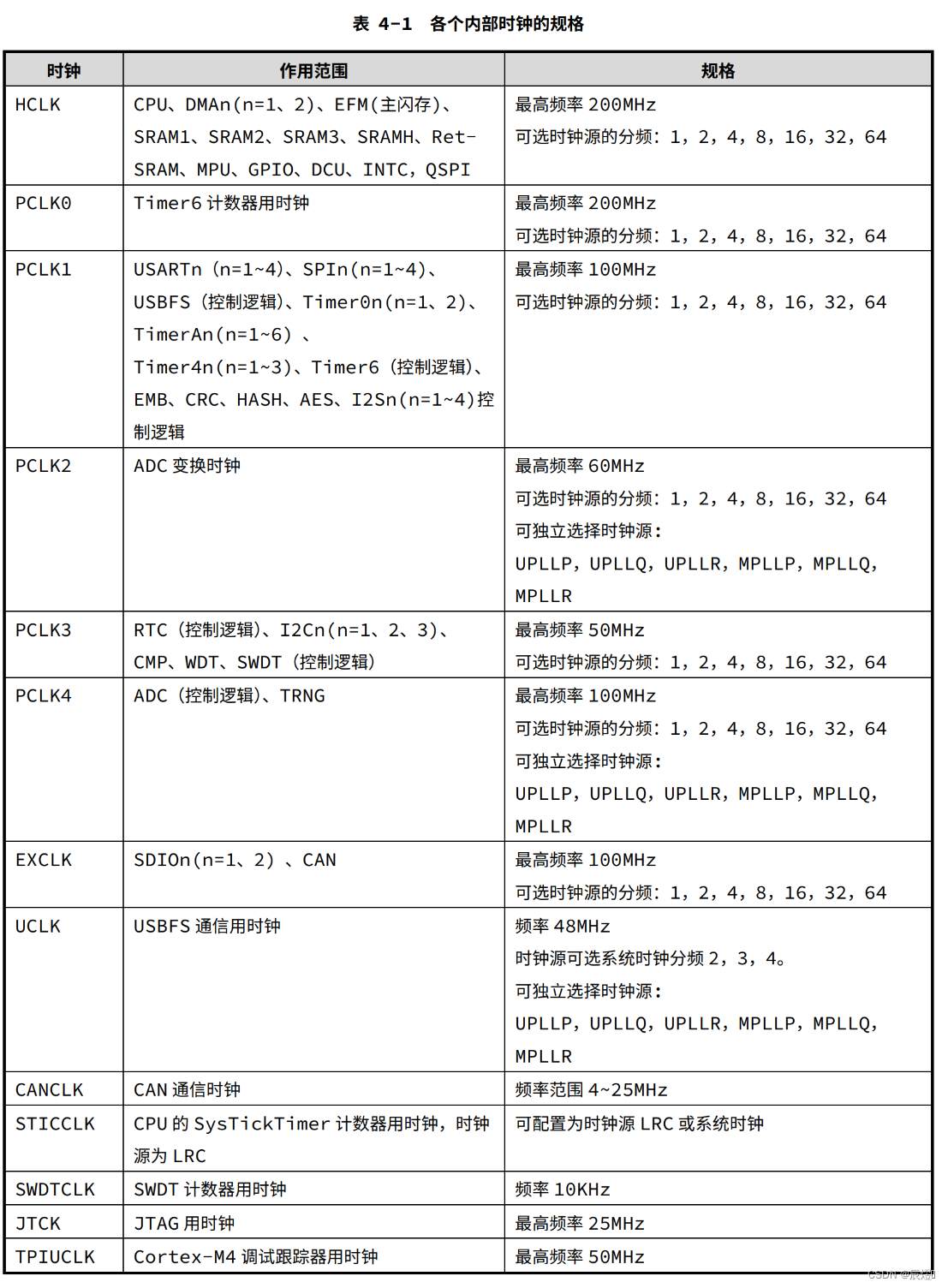

时钟控制单元提供了一系列频率的时钟功能,包括:一个外部高速振荡器、一个外部低速振荡器、两个 PLL 时钟、一个内部高速振荡器、一个内部中速振荡器、一个内部低速振荡器、一个 SWDT 专用内部 低速振荡器、时钟预分频器、时钟多路复用和时钟门控电路。 时钟控制单元还提供时钟频率测量功能。时钟频率测量电路(FCM)使用测定基准时钟对测定对象时钟 进行监视测定。在超出设定范围时发生中断或者复位。 AHB、APB 和 Cortex-M4 时钟都源自系统时钟,系统时钟的源可选择 6 个时钟源: 1) 外部高速振荡器(XTAL) 2) 外部低速振荡器(XTAL32) 3) MPLL 时钟(MPLL) 4) 内部高速振荡器(HRC) 5) 内部中速振荡器(MRC) 6) 内部低速振荡器(LRC) 系统时钟的最大运行时钟频率可以达到 200MHz。SWDT 有独立的时钟源:SWDT 专用内部低速振荡 器(SWDTLRC)。实时时钟(RTC)使用外部低速振荡器或者内部低速振荡器作为时钟源。USB-FS 的 48MHz 时钟可以选择系统时钟,MPLL,UPLL 作为时钟源。 对于每一个时钟源,在未使用时都可以单独打开和关闭,以降低功耗

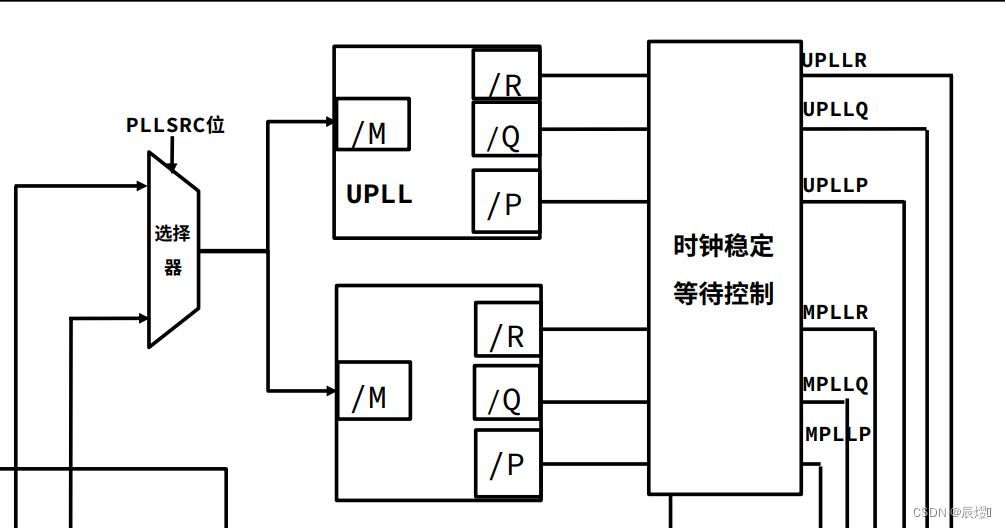

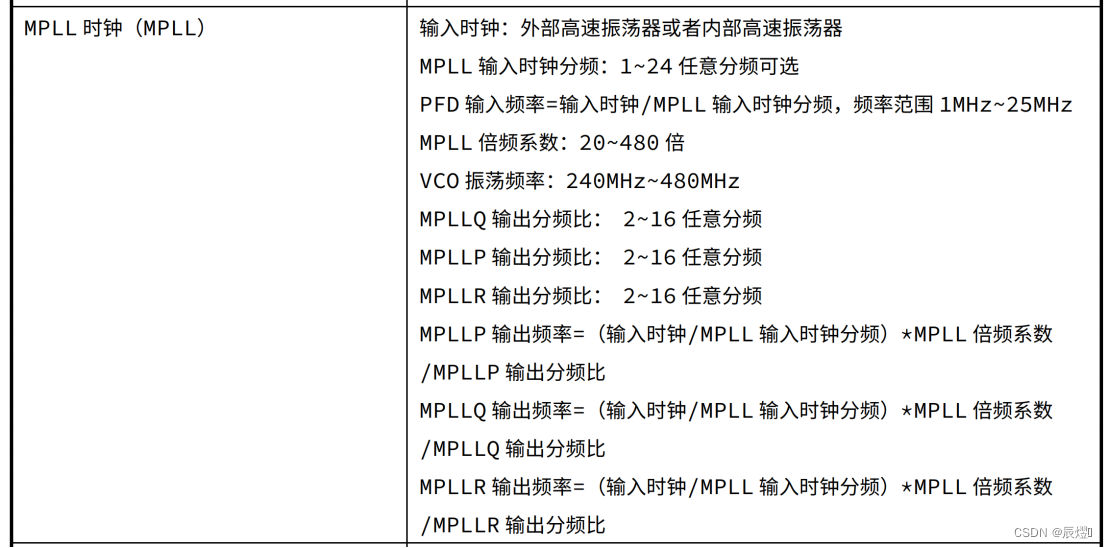

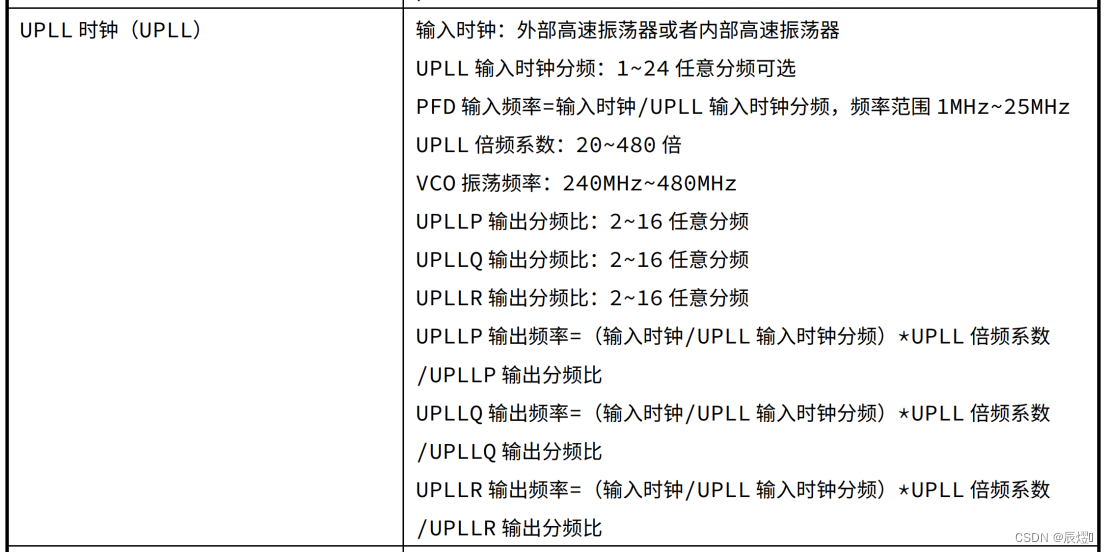

2.PLL 的配置

在实际使用中,我们多数情况下需要将时钟源进行倍频,以使系统时钟达到一个较高的频率。倍频使用的器件就是 PLL。HC32F46xx 器件具有两个PLL:

(1)MPLL 由 XTAL 或HRC 振荡器提供时钟信号,并具有三个不同的输出时钟:

P 分频器输出用于生成系统时钟(最高达 200 MHz)

三个输出都可用于生成 USBFS、TRNG、ADC 和 I2S 时钟。

(2)UPLL 三个输出亦可用于生成 USBFS、TRNG、ADC 和 I2S 时钟。

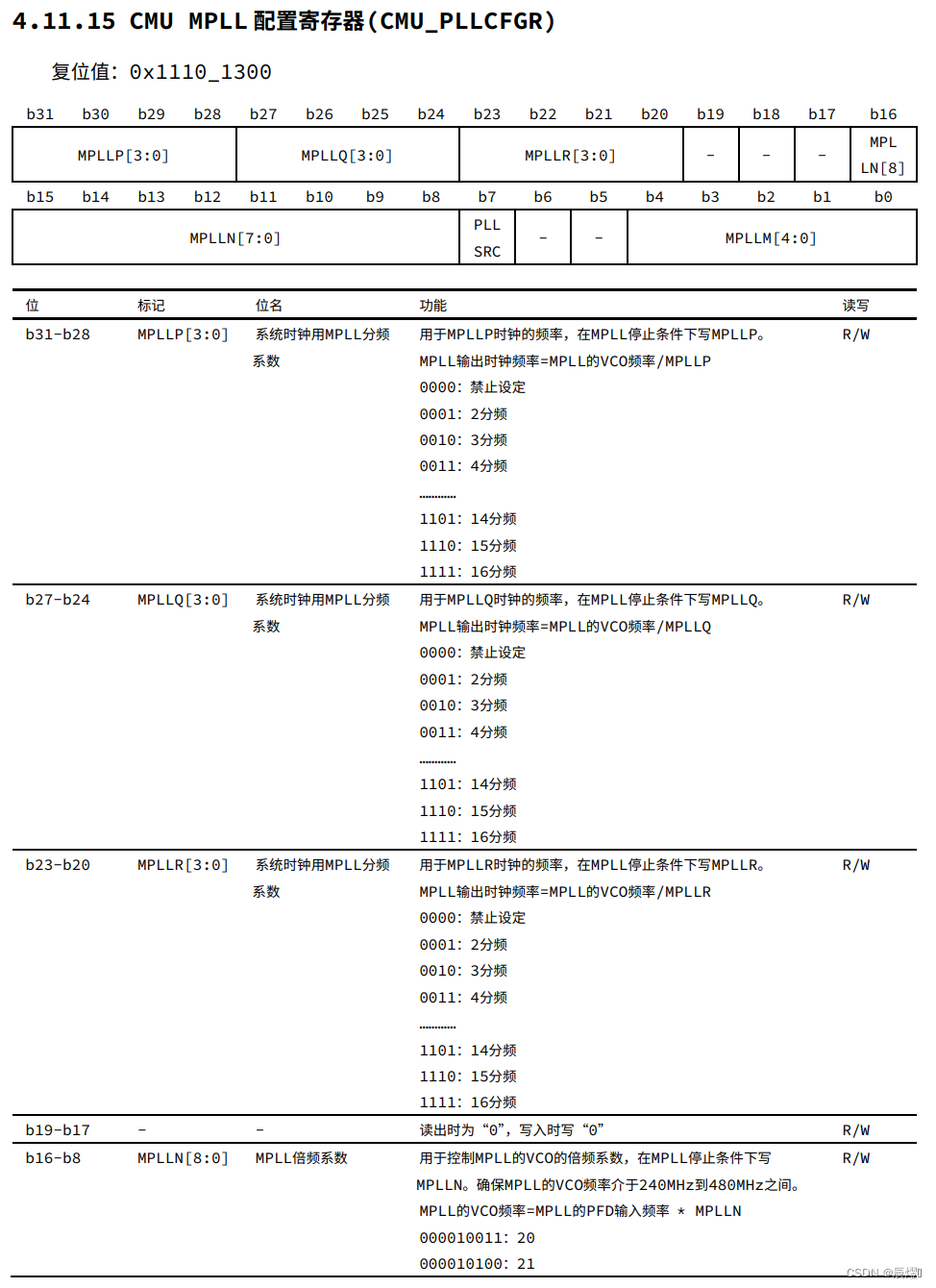

使用时注意以下三点: 在 HRC 或 XTAL 振荡器稳定后,再对 PLL 进行配置。 MPLL/UPLL 的分频系数 M、N、P、Q、R

可独立配置,由于在 PLL 使能后 PLL 配置参数便不可更改,所以建议先对 PLL 进行配置,然后再使能。 当进入掉电和停止模式后,两个

PLL 将由硬件禁止。

二、总体框图和寄存器介绍

三、更换晶振后代码修改

1.更改外部晶振频率

在system_hc32f460.h中

将外部高速振荡器(XTAL)频率更改为12M

#if !defined (XTAL_VALUE)

#define XTAL_VALUE (12000000UL) /*!< External high speed OSC freq. */

#endif

2.更改时钟配置

在ev_hc32f460_lqfp100_v2.c中

rt_thread 在 board.c SystemClock_Config(void)中

修改后代码:

/* MPLL config (XTAL / pllmDiv * plln / PllpDiv = 200M). */

stcMpllInit.PLLCFGR_f.PLLM = 3UL - 1UL;

stcMpllInit.PLLCFGR_f.PLLN = 100UL - 1UL;

stcMpllInit.PLLCFGR_f.PLLP = 2UL - 1UL;

stcMpllInit.PLLCFGR_f.PLLQ = 2UL - 1UL;

stcMpllInit.PLLCFGR_f.PLLR = 2UL - 1UL;

解析:

MPLL config (XTAL / pllmDiv * plln / PllpDiv = 200M)

8M晶振时: 8M/1×50/2=200

12M晶振时: 12M/3×100/2=200

四、名词解释

1.PLL

锁相环接收一个它所锁定的信号,然后可以从其内部的VCO输出这个信号。乍一看,这可能不是特别有用,但是在你完全明白它之后,就有可能开发出大量的锁相环应用。

锁相环的基本构成是什么?

一个基本的锁相环PLL,由三个基本元素组成:

相位比较器/检测器:顾名思义,锁相环内的这个电路块对两个信号的相位进行比较,并根据两个信号的相位差产生一个电压。

2.VCO

压控振荡器(VCO):压控振荡器是产生无线电频率信号的电路块,通常被认为是回路的输出。它的频率可以控制在环路所需的工作频段上。

环路滤波器: 这个滤波器用于过滤锁相环路中相位比较器的输出。它用于去除VCO线路中相位被比较的信号的任何成分,即参考和VCO输入。它还控制着环路的许多特性,包括环路的稳定性、锁定的速度等。

3.锁相环电路的主要目的是做什么?

PLL用于生成、稳定、调制、解调、过滤或从数据被中断的 "噪声 "通信通道中恢复信号。PLL电路的主要目的是使输出振荡器信号与参考信号同步。当这两个信号之间的相位差为零时,系统被 “锁定”。PLL是一个闭环系统,有一个控制机制来减少可能发生的任何相位误差。

4.PFD

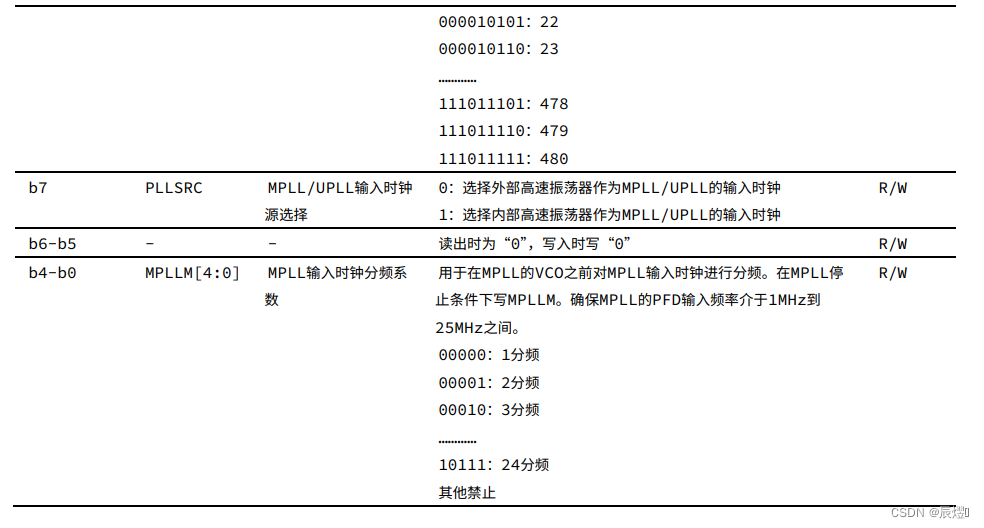

输入频率=输入时钟/MPLL 输入时钟分频

PFD 输入时钟频率=输入时钟/PLLH 输入时钟分频,频率范围

8MHz~24MHz

2911

2911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?