位拆分与运算

题目描述

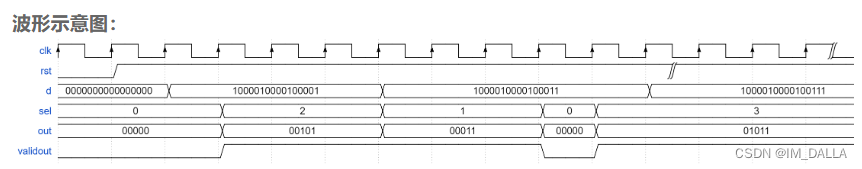

现在输入了一个压缩的16位数据,其实际上包含了四个数据[3:0][7:4][11:8][15:12],

现在请按照sel选择输出四个数据的相加结果,并输出valid_out信号(在不输出时候拉低)

0: 不输出且只有此时的输入有效

1:输出[3:0]+[7:4]

2:输出[3:0]+[11:8]

3:输出[3:0]+[15:12]

输入描述

输入信号 d, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述

输出信号 validout out

类型 reg

解题思路

当我们看到题目中有sel信号,首先在语句块中想到使用case语句块,其分支分别表示各个sel信号的情况;

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output [4:0]out,

output validout

);

//*************code***********//

reg validout_t;

reg [4:0] out_t;

reg [15:0] d_t;

always @(posedge clk or negedge rst)

if (!rst) begin

validout_t <= 1'b0;

out_t <= 5'b00000;

end

else begin

case (sel)

2'b00: begin

d_t = d; //注意此处阻塞赋值和非阻塞赋值的区别,进行锁存

out_t <= 5'b00000;

validout_t <= 1'b0;

end

2'b01: begin

out_t <= d_t[3:0] + d_t[7:4];

validout_t <= 1'b1;

end

2'b10: begin

out_t <= d_t[3:0] + d_t[11:8];

validout_t <= 1'b1;

end

2'b11: begin

out_t <= d_t[3:0] + d_t[15:12];

validout_t <= 1'b1;

end

endcase

end

assign validout = validout_t;

assign out = out_t;

//*************code***********//

endmodule

117

117

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?