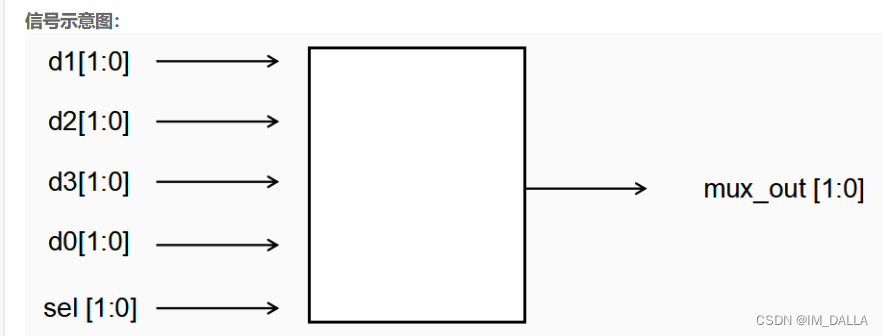

四选一多路器

题目要求如下:制作一个四选一的多路选择器,要求输出定义上为线网类型.

状态转换 (即将d0~d3作为sel信号时,其对应的mux_out值)

d0(d0 = 11) 11

d1(d1 = 00) 10

d2(d2 = 01) 01

d3(d3 = 02) 00

输入描述

输入信号 d1,d2,d3,d4 sel

类型 wire

下面给出不同的解题思路

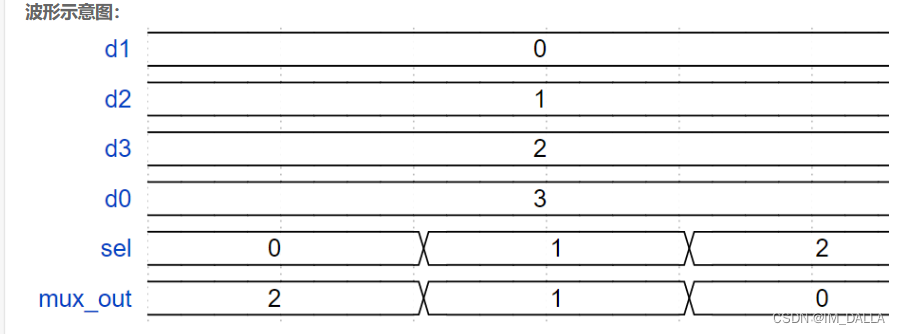

当选择信号sel = 0时,多路选择器的输出mux_out = 2 (即选择数据输入端d3)

当选择信号sel = 1时,多路选择器的输出mux_out = 1 (即选择数据输入端d2)

当选择信号sel = 2时,多路选择器的输出mux_out = 0(即选择数据输入端d1)

当选择信号sel = 3时,多路选择器的输出mux_out = 3(即选择数据输入端d0)

1.使用条件分支语句——case

由于条件分支语句case,if都需在always语句块中,其中的变量必须为寄存器型变量;由于题目中要求的输出内容为wire类型,因此,重新定义一个寄存器型变量mux_out_t作为中间变量;

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

//*************code***********//

reg [1:0] mux_out_t;

always @(*)

begin

case(sel)

2'b00: mux_out_t = d3;

2'b01: mux_out_t = d2;

2'b10: mux_out_t = d1;

2'b11: mux_out_t = d0;

default: mux_out_t = d0; //该语句可加可不加

endcase

end

assign mux_out = mux_out_t;

//*************code***********//

endmodule2.使用assign语句 ——使用条件表达符

<条件表达式>?<表达式1>:<表达式2>

——条件表达式的计算结果有真“1”,假“0”和未知态“x”三种,当条件表达式的结果为真时,执行表达式1,当条件表达式的结果为假时,执行表达式2。

基本思想:将一个4选1多路器拆分为两个2选1多路器

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

//*************code***********//

wire [3:0] w1;

wire [1:0] w2;

assign w1 = sel[0] ? {d2, d0} : {d3, d1};

assign w2 = sel[1] ? w1[1:0] : w1[3:2];

assign mux_out = w2;

//*************code***********//

endmodule

313

313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?