奇偶校验

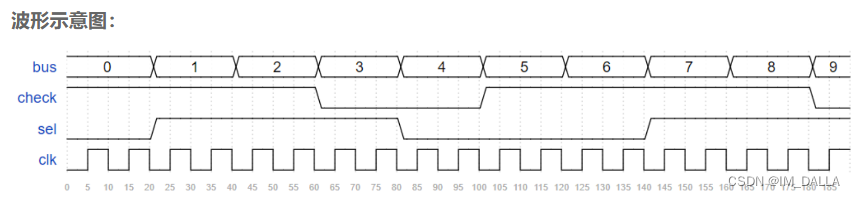

题目描述:现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

输入描述

输入信号 bus sel

类型 wire

输出描述

输出信号 check

类型 wire

解题思路

当sel = 0时,其输出偶校验。即输入bus(32位数据)中有偶数个0时,check = 1,输入bus中有奇数个0时,check = 0;

当sel = 1时,其输出奇校验。即输入bus(32位数据)中有奇数个1时,check = 1,输入bus中有偶数个1时,check = 0;

方法1:使用always语句块

其中:我们来了解一下归约运算符(缩位运算符)的定义:

归约运算符按位进行逻辑运算,属于单目运算符。由于这一类运算符运算的结果是产生1位逻辑值,因而被形象地称为缩位运算符。

Verilog HDL中,缩位运算符包括&(与)、|(或)、^(异或)以及相应的非操作~&、~|、~^、^~。归约运算符的操作数只有一个

归约运算符的运算过程是:设a是一个4位的寄存器变量,它的4位分别是a[0], a[1], a[2], a[3]。当对a进行缩位运算时,先计算a[0]和a[1]的缩位运算,产生1位的结果,再将这个结果与a[2]进行运算,再与a[3]进行运算,最终只产生1位的结果。

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

reg t;

always @(*)

if (sel) //奇校验

t = ^bus; //32位bus信号按位异或; 若为奇数个1,t=1; 若为偶数个1,t=0

else

t = ~^bus; //若为奇数个1,t=0; 若为偶数个1,t=1

assign check = t;

//*************code***********//

endmodule方法2:使用条件表达符

仅需一条assign语句

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

assign check = sel ? ^bus : ~^bus;

//*************code***********//

endmodule

1223

1223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?