偶数倍分频:

如果进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。

奇数倍分频:

首先,使用上升沿触发和下降沿触发分别产生占空比不为50%的时钟,占空比小的部分为高电平。两个时钟进行相或运算,最终产生占空比为50%的奇分频。

偶数分频:

module Even_pra(

input wire clk ,

input wire rst_n ,

input wire [ 3: 0] num ,

output wire dri_clk

);

reg [ 3: 0] cnt;

reg dri_clk_reg;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 4'd0;

else if(cnt == num - 1'b1)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dri_clk_reg <= 1'b0;

else if(cnt < (num >> 1))

dri_clk_reg <= 1'b0;

else

dri_clk_reg <= 1'b1;

end

endmodule

奇数分频:

module Odd_pra(

input wire clk ,

input wire rst_n ,

input wire [ 3: 0] num ,

output wire dri_clk

);

reg [ 3: 0] cnt;

reg dri_clk_r1;

reg dri_clk_r2;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 4'b0;

else if(cnt == num - 1)

cnt <= 4'b0;

else

cnt <= cnt + 1'b1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dri_clk_r1 <= 1'b0;

else if(cnt < (num >> 1))

dri_clk_r1 <= 1'b1;

else

dri_clk_r1 <= 1'b0;

end

always @(negedge clk or negedge rst_n) begin

if(!rst_n)

dri_clk_r2 <= 1'b0;

else if(cnt < (num >> 1))

dri_clk_r2 <= 1'b1;

else

dri_clk_r2 <= 1'b0;

end

assign dri_clk = dri_clk_r1 | dri_clk_r2;

endmodule

`timescale 1ps/1ps

module Odd_pra_TB();

reg clk, rst_n;

wire [ 3: 0] num = 4'd3;

wire dri_clk;

initial begin

rst_n = 0;

# 20

rst_n = 1;

end

initial clk = 0;

always # 10 clk = ~clk;

Odd_pra Odd_pra_Init(

.clk (clk ),

.rst_n (rst_n ),

.num (num ),

.dri_clk (dri_clk)

);

endmodule

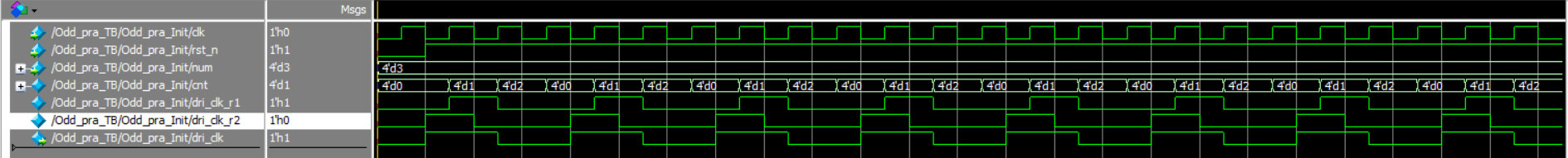

三分频

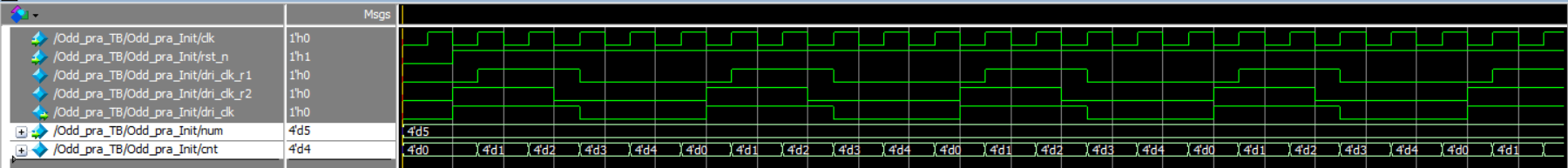

五分频

7465

7465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?