描述

编写一个模块,对输入的时钟信号clk_in,实现任意奇数分频,要求分频之后的时钟信号占空比为50%。模块应包含一个参数,用于指定分频的倍数。

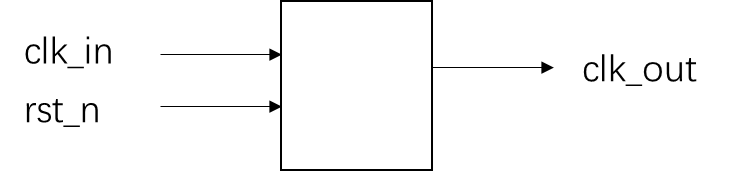

模块的接口信号图如下:

要求:使用Verilog HDL语言实现,并编写testbench验证模块的功能。

输入描述:

clk_in:输入时钟信号

rst_n:复位信号,低电平有效

输出描述:

clk_out:分频之后的时钟信号

参考代码

`timescale 1ns/1ns

module clk_divider

#(parameter dividor = 5)

( input clk_in,

input rst_n,

output clk_out

);

//定义计数器的位宽,$clog2()为取对数操作,在编译过程中执行完成。因此在模块运行过程中CNT_WIDTH是一个确定的数值。

parameter CNT_WIDTH = $clog2(dividor-1);

reg flag_1;

reg flag_2;

reg [CNT_WIDTH :0] cnt;

always @(posedge clk_in or negedge rst_n)

if (!rst_n)

cnt <= 0;

else if(cnt == dividor-1)

cnt <= 0;

else cnt <= cnt + 1'd1;

always @(posedge clk_in or negedge rst_n)

if (!rst_n)

flag_1 <= 0;

else if(cnt == (dividor-1>>1))

flag_1 <= ~flag_1;

else if(cnt == dividor-1)

flag_1 <= ~flag_1;

else flag_1 <= flag_1;

always @(negedge clk_in or negedge rst_n)

if (!rst_n)

flag_2 <= 0;

else if(cnt == (dividor-1 >>1))

flag_2 <= ~flag_2;

else if(cnt == dividor-1)

flag_2 <= ~flag_2;

else flag_2 <= flag_2;

assign clk_out = flag_1 || flag_2;

endmodule

2756

2756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?