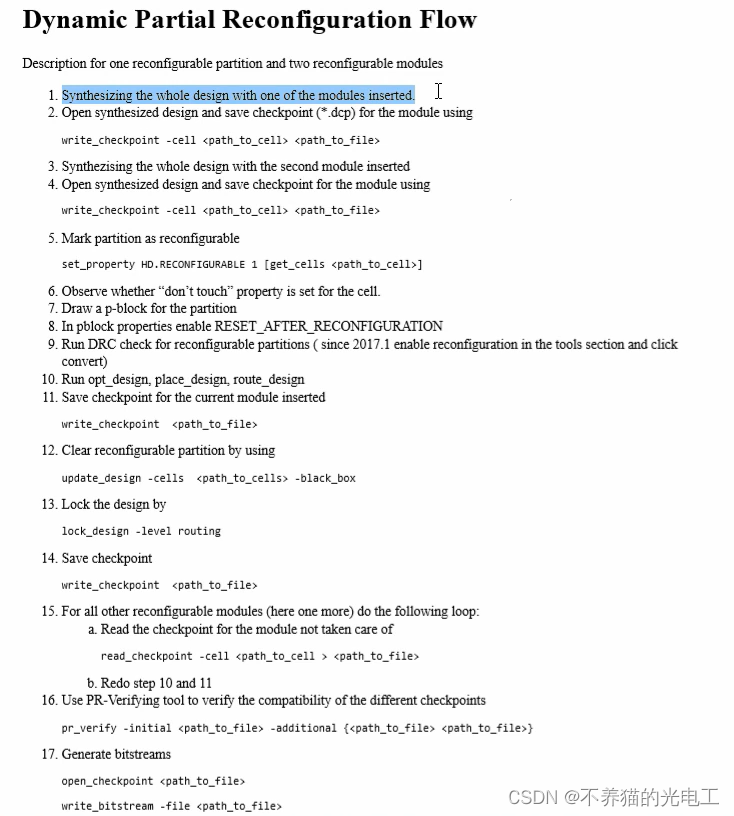

FPGA动态重编译,主要使用控制台:

新建工程,在工程目录下新建文件夹drp(e:/Projects/DRP/project_2/drp)

打开vivado工程(示例工程: e/project/drp/project1)

cd e:/Projects/DRP/project_2/drp/ TCL工作台跳转到FPGA工程下的drp目录

2、控制台输入:write_checkpoint -cell U1 led_1pps.dcp 当前网表文件中将设为可重编译的cell模块的路径+ 文件名

4、控制台输入:write_checkpoint -cell U1 led_3pps.dcp 当前网表文件中将设为可重编译的cell模块的路径+ 文件名

5、控制台输入:set_property HD.RECONFIGURABLE 1 [get_cells U1] 指定当前网表文件中设为可重编译的cell模块的路径

确认 U1 状态为don't touch ;画pblock,pblock属性勾选reset_after_reconfigguraation,sanpping_mode 为on;

9 、report drc ,rules只选择 partial reconfigeration

10、控制台输入:opt_design ,place_design ,route_design

11、控制台输入:write_checkpoint top_led_3pps_pblock.dcp 保存当前工程dcp文件

12、控制台输入:update_design -cells led_3pps -black_box 设置需重配置的模块为黑盒子

13、控制台输入:lock_design -level routing 此时网表中所有使用的资源会变橙色

14、控制台输入:write_checkpoint top_led_3pps_black.dcp

15、控制台输入:read_checkpoint -cell U1 led_1pps.dcp 将前面的led_1pps.dcp 读到当前网表文件中设为可重编译的cell路径下

redo 10 、opt_design ,place_design ,route_design

redo 11 、write_checkpoint top_led_1pps_pblock.dcp

16、控制台输入:pr_verify -initial top_led_3pps_pblock.dcp -additional {top_led_1pps_pblock.dcp} 验证两个.dcp文件的兼容性

17、控制台输入:open_checkpoint top_led_3pps_pblock.dcp

新控制台输入:write_bitstream -file top.bit

控制台输入:open_checkpoint top_led_1pps_pblock.dcp

新控制台输入:write_bitstream -file top.bit

1439

1439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?