这篇文章是基于之前FX3实现FPGA与USB3.0通信的内容。本人新手,写的不好如有错误请原谅。今天来记录一下官方文档的学习。

一、基本信息讲解

1.1 GPIF II Designer和CYUSB3014芯片是什么?

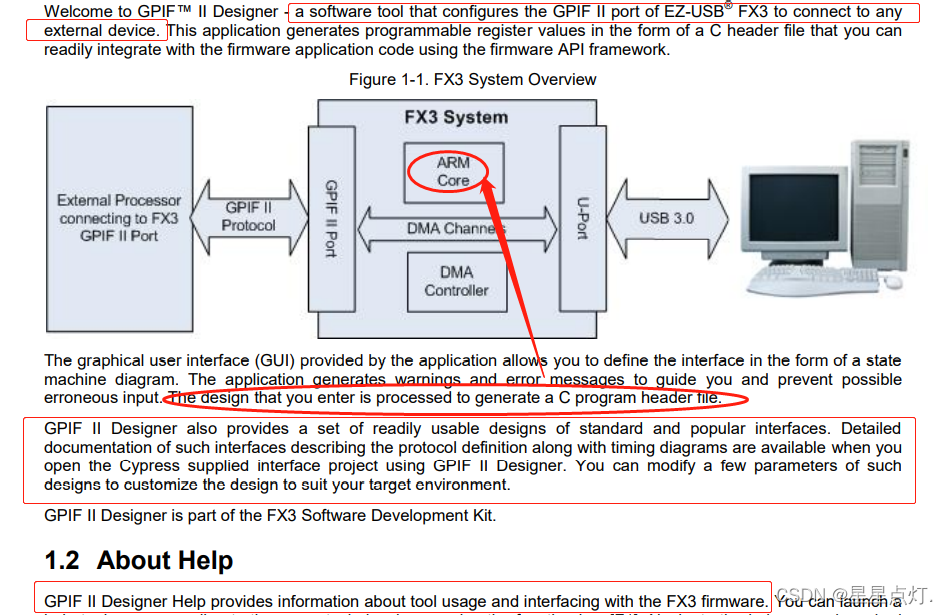

①GPIF II Designer是一个用来配置FX3的GPIF II接口的软件,如图所示,通过正确的配置,使遵从GPIF II接口协议的 外部处理器(如FPGA) 和 FX3通信,进而通过USB3.0与外部设备通信。比如AD采集数据经FPGA、FX3、通过USB3.0将数据传输至PC机。

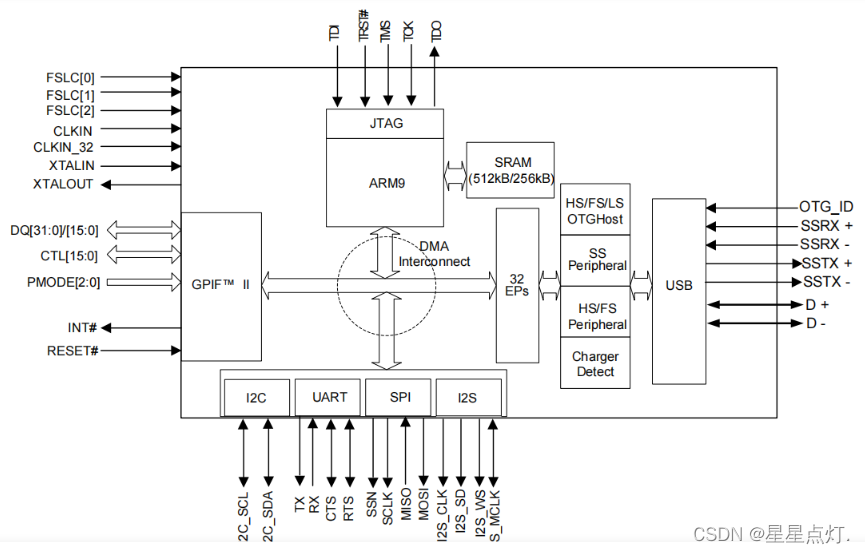

②FX3芯片内部集成了200MhzARM9内核,具有一个可进行完全配置的并行通用可编程接口 GPIF II,它可与任何处理器、ASIC 或 FPGA 连接,从 GPIF II 到 USB 接口的数据传输速度可达 320 MBps。EZ-USB FX3同时还支持I2C、UART、SPI、I2S串行设备接口,EZ-USB FX3 配有用于存储代码和数据的 512 KB 片上 SRAM。EZ-USB FX3 能在多种外设(如 USB、GPIF II、I2 S、SPI、UART) 之间实现高效灵活的的 DMA 连接。固件只需配置外设间数据访问,这些外设随后由 DMA 结构进行管理。

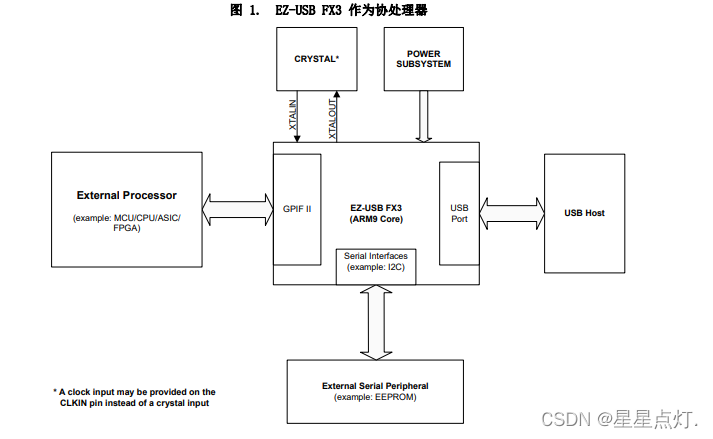

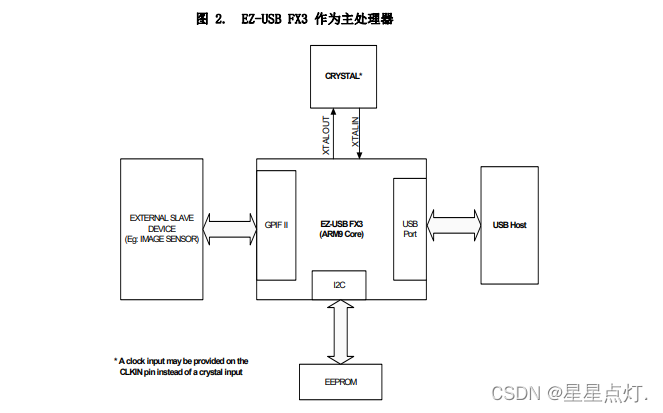

③EZ-USB FX3典型应用:主处理器和协处理器

之前记录过的USB3.0和FPGA通讯的例程中就是作为协处理器的应用,是不能主动访问外部处理器(如FPGA)的寄存器这些东西的。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2195

2195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?