一、编码/译码器的module

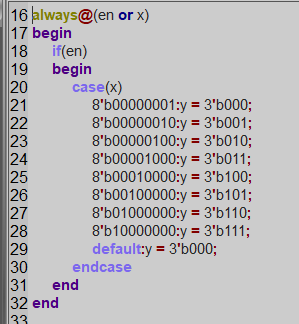

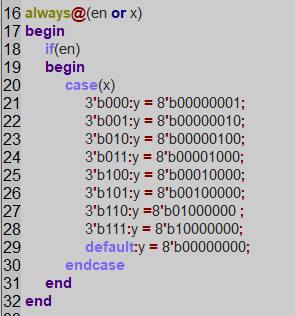

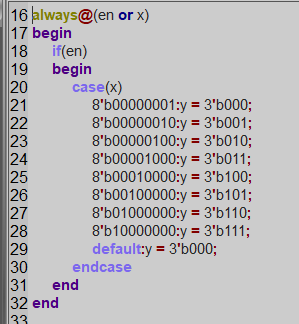

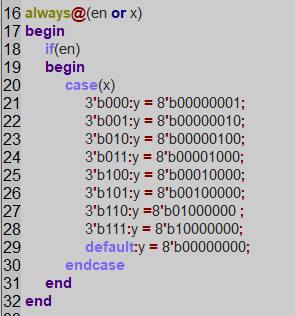

编码器设计为8线-3线编码器,x为3输入端(wire类型),en为使能端,y为8输出端(reg类型)。译码器为3线-8线译码器,类似于上。

二、测试模块

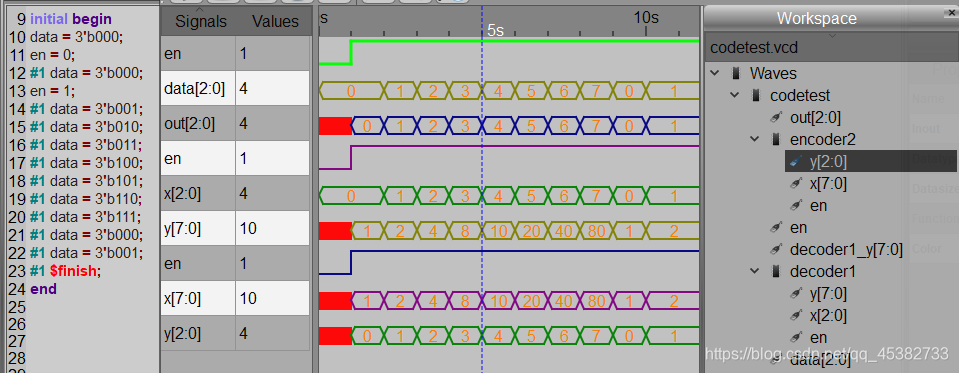

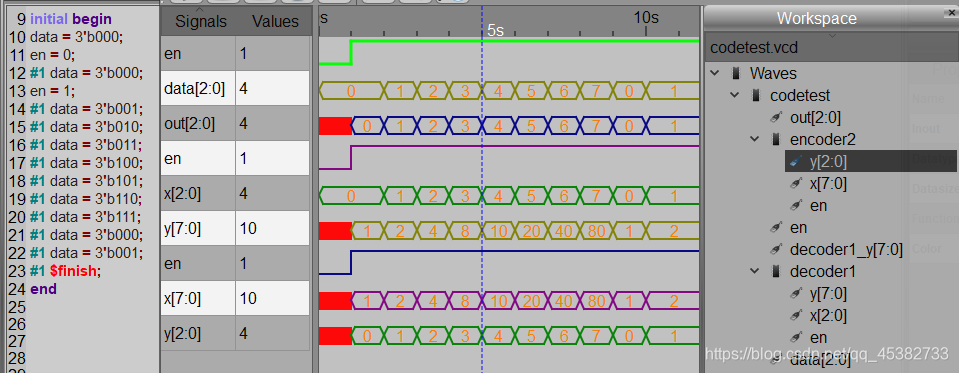

data为输入激励(reg类型),en为使能端(reg类型),out为输出端(wire)。实现的功能是:使能有效时,输入等于输出。

激励以及波形如下:

注:图中5s时的20为十六进制。

RobeiEDA 编码/译码器的设计

最新推荐文章于 2024-04-22 12:07:41 发布

一、编码/译码器的module

编码器设计为8线-3线编码器,x为3输入端(wire类型),en为使能端,y为8输出端(reg类型)。译码器为3线-8线译码器,类似于上。

二、测试模块

data为输入激励(reg类型),en为使能端(reg类型),out为输出端(wire)。实现的功能是:使能有效时,输入等于输出。

激励以及波形如下:

注:图中5s时的20为十六进制。

188

188

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?